0

0

电子产业一站式服务平台

电子百科

典型TTL与非门电路电路组成

输入级——晶体管T1和电阻Rb1构成。

中间级——晶体管T2和电阻Rc2、Re2构成。

输出级——晶体管T3、T4、D和电阻Rc4构成,推拉式结构,在正常工作时,T4和T3总是一个截止,另一个饱和。

工作原理

当输入Vi=3.6V(高电平)

Vb1=3.6+0.7=4.3V 足以使T1(bc结)T2(be结)T3 (be结)同时导通, 一但导通Vb1=0.7+0.7+0.7=2.1V(固定值),此时V1发射结必截止(倒置放大状态)。

Vc2=Vces+Vbe2=0.2+0.7=0.9V 不足以T3和D同时导通,T4和D均截止。

V0=0.2V (低电平)

当输入Vi=0.2V(低电平)

Vb1=0.2+0.7=0.9V不 足以使T1(bc结)T2(be结)T3 (be结)同时导通,

T2 T3均截止, 同时Vcc---Rc2----T4---D---负载形成通路,

T4和D均导通。

V0=Vcc-VRc2(可略)-Vbe4-VD=5-0.7-0.7 =3.6(高电平)

结论:输入高,输出低;输入低,输出高(非逻辑)

主要特点

·TTL优势:

·1、工作速度快 ·2、带负载能力强 ·3、传输特性好

TTL反相器的电压传输特性

电压传输特性是指输出电压跟随输入电压变化的关系曲线,即UO=f(uI)函数关系。如图2.3.2所示曲线大致分为四段:

AB段(截止区):当UI≤0.6V时,T1工作在深饱和状态,Uces1

TTL反相器的电压传输特性 BC段(线性区):当0.6V≤UI

DE段(饱和区):当UI≥1.4V时,随着UI增加 T1进入倒置工作状态,D截止,T4截止,T2、T3饱和,因而输出低电平UOL=0.3V。

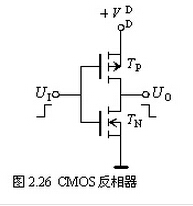

电路结构

CMOS反相器电路如图2.7-1(a) (b)所示它由两个增强型MOS场效应管组成,其中V1为NMOS管,称驱动管,V2为PMOS管,称负载管。 NMOS管的栅源开启电压UTN为正值,PMOS管的栅源开启电压是负值,其数值范围在2~5V之间。为了使电路能正常工作,要求电源电压UDD>(UTN+|UTP|)。UDD可在3~18V之间工作,其适用范围较宽。

工作原理

(1)当UI=UIL=0V时,UGS1=0,因此V1管截止,而此时|UGS2|>

|UTP|,所以V2导通,且导通内阻很低,所以UO=UOH≈UDD, 即输出为高电平.

(2)当UI=UIH=UDD时,UGS1=UDD>UTN,V1导通,而UGS2=0

CMOS反相器的主要特性?

CMOS反相器的电压传输特性如图2.7-2所示。

CMOS 反相器的电流传输特性2.7-3图 2.7-2 CMOS反相器的电压传输特性

在AB段由于V1截止,阻抗很高,所以流过V1和V2的漏电流几乎为0。 在CD段V2截止,阻抗很高,所以流过V1和V2的漏电流也几乎为0。只有在BC段,V1和V2均导通时才有电流iD流过V1和V2,并且在UI=1/2UDD附近,iD最大。