0

0

电子产业一站式服务平台

电子百科

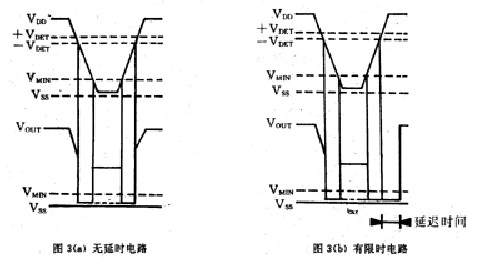

当输入电压(VDD)高于检测电压(-VDET)时,输入电压等于输出电压(VOUT),N沟道漏极开路MOSFET关断。如图3(a)所示。

当输入电压(VDD)低于检测电压(-VMIN)时,输出电压(VOUT)等于VSS。

当输入电压(VDD)下降到最低工作电压(VMIN)时,输出电压不确定。

输入电压从地电位(VSS)上升时,当VDD低于最低工作电压(VMIN)时,输出电压不确定。当VDD超过VMIN时,输出电压将维持在电位(VSS)。当输入电压上升到释放电压(+VDET)后,输出电压等于输入电压。

释放电压(+VDET)和检测电压(-VDET)之间的电压差为滞后电压。

当输入电压(VDD)从地电位上升时,延时电路将产生一定的延迟时间tDLY。输入电压(VDD)超过释放电压(+VDET)后,要经过一定的时间tDLY,输出电压才等于输入电压,如图3(b)表示。