0

0

电子产业一站式服务平台

USB端口对PC外设的发展起到了革命性的推动作用,并且正变得越来越流行,比如在采集测量数据或在机器上安装软件更新等应用中就非常常见。作为用于数据传输的一种总线系统,只要有移动设备连着的地方就有它的身影。虽然在日常生活中使用的连接器看起来非常结实,但USB应用开发人员仍然必须重视这些接口的保护。

在Intel公司的“高速USB平台设计指南”中,甚至提高了考虑USB端口易感性因素的重要性。Intel建议用电流补偿型扼流圈抑制 EMI,再用其它元件防止静电放电(ESD)。电子设备经常会遭受静电放电。静电放电脉冲电压可能高达30kV,因此对所有类型的集成电路来说都是非常危险的。目前有些IC对静电放电来说是“安全的”,但这种安全性只是对一小部分潜在威胁来说是有保证的。日常操作表明:额外保护是必不可少的。只有采取外部保护措施才能开发出整块电路板不受静电放电影响以及高度可靠的产品来。专门的抑制措施同样也是必需的。无线联网的电子设备如今是遍地开花,它们的数量正在与日俱增。

实际的抗干扰能力

在提到干扰对USB的影响时,差分模式数据传输与简单的同轴电缆相比具有很大的优势。在感性干扰效应(磁场)情况下,导线的绞合可以弥补干扰效应。鉴于每根双绞线的部分电感的对称性,干扰会彼此影响补偿效果。这种抗干扰效果在实际应用中会大打折扣。USB控制器的输入/输出不是完全对称的,因此USB信号显示出共模干扰。Layout与HF/EMC不兼容,寄生电容和缺少波阻匹配会产生共模干扰。电路设计(USB滤波器)不充分,滤波器影响信号质量,和/或插损太低。接口设计(插座,外壳)不充分。不良的接地会减小电缆的屏蔽衰耗。滤波器具有不良的接地参考。USB电缆不对称、屏蔽不良以及没有足够好的接地。这种电缆会劣化信号质量,辐射信号谐波,对外部干扰源起不到足够的屏蔽衰减。

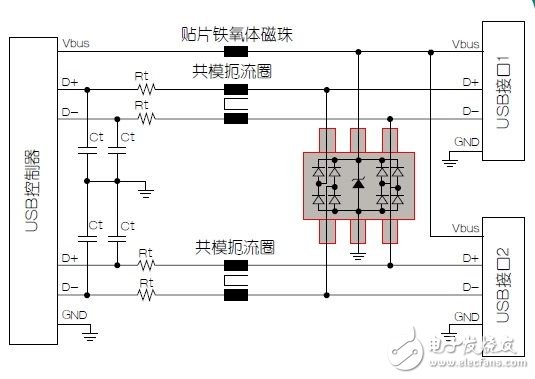

对于一个端到端的EMC兼容设计而言,对电源(VBUS)进行滤波也很重要。许多开发人员忽视了这一点,却不知道他们的产品为何通不过 EMC实验室的测试。这里介绍了针对一个或两个USB端口的两种优化设计。两条USB线可以用TVS二极管加以保护。所有4条信号线以及公共电源都得到了很好的静电放电保护。进一步的优化可以通过用一个电流补偿式数据线扼流圈和电容,搭建一个LC滤波器滤除输入端的共模和差模干扰来实现。在电源端使用 WE-CBF系列贴片磁珠可以实现卓越的抑制性能(图1)。

图1:具有静电放电保护功能的双端口USB端口。

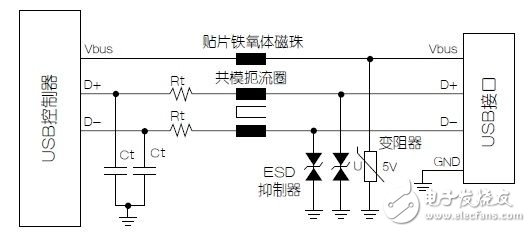

单通道保护元件(如WE-VE系列静电放电抑制器)必须始终连接在信号线与地之间。不必使用小电容的静电放电抑制器来保护电源,普通的SMD变阻器就足够了。它可以吸收较高的能量和较高的电流,因此是设计的第一选择(图2)。

图2:与屏蔽数据线不同,电源端不必使用小电容的静电放电抑制器。

针对USB端口的推荐Layout

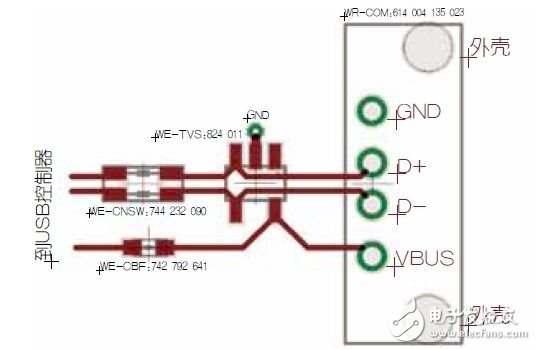

从图3可以明显看出,有两条差分信号线(D+和D-)从插头连接器连接到TVS二极管,再通过电流补偿式数据线扼流圈连接到USB控制器。这样能够得到出色的静电放电保护功能,并能良好的抑制数据线对。VBUS通过TVS二极管路由到贴片磁珠。在贴片磁珠之后,可以插入额外的电容和另一个贴片磁珠来实现最大可能的PI滤波器衰减。

图3:USB端口保护。