# Is Now Part of

# ON Semiconductor®

To learn more about ON Semiconductor, please visit our website at <a href="https://www.onsemi.com">www.onsemi.com</a>

ON Semiconductor and the ON Semiconductor logo are trademarks of Semiconductor Components Industries, LLC dba ON Semiconductor or its subsidiaries in the United States and/or other countries. ON Semiconductor owns the rights to a number of patents, trademarks, copyrights, trade secrets, and other intellectual property. A listing of ON Semiconductor's product/patent coverage may be accessed at www.onsemi.com/site/pdf/Patent-Marking.pdf. ON Semiconductor reserves the right to make changes without further notice to any products herein. ON Semiconductor makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does ON Semiconductor assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. Buyer is responsible for its products and applications using ON Semiconductor products, including compliance with all laws, regulations and safety requirements or standards, regardless of any support or applications information provided by ON Semiconductor. "Typical" parameters which may be provided in ON Semiconductor data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. ON Semiconductor does not convey any license under its patent rights nor the rights of others. ON Semiconductor products are not designed, intended, or authorized for use as a critical component in life support systems or any EDA Class 3 medical devices with a same or similar classification in a foreign jurisdiction or any devices intended for implantation in the human body. Should Buyer purchase or use ON Semiconductor products for any such unintended or unauthorized application, Buyer shall indemnify and hold ON Semiconductor and its officers, employees, emplo

# **Application Note 7525**

# PCB Land Pattern Design and Surface Mount Guidelines for MicroFET™ Packages

Scott Pearson (Fairchild Semiconductor), Jim Benson (Intersil Corporation)

# Introduction

Fairchild's MicroFET<sup>™</sup> package is a relatively new packaging concept that is currently experiencing rapid acceptance. It offers a variety of benefits including reduced lead inductance, a small sized "near chip scale" footprint, thin profile, and low weight. Its use of an exposed copper die-pad technology (Figure 2) offers good thermal and electrical performance. These features make the MicroFET<sup>™</sup> an ideal choice for many new applications where size, weight, thermal and electrical performance are important.

Figure 1. 3D Cutaway of 8 pin MicroFET™

There are general industry references, such as IPC-SM-782, for printed circuit board (PCB) land pattern design. But because the MicroFET<sup>™</sup> package style is relatively new, such industry guidelines for it are still in development. This Application Note provides general guidelines for use in developing land pattern layouts and solder mounting processes.

It should be emphasized that these guidelines are general in nature and should only be considered a starting point in this effort. The user must apply their actual experiences and development efforts to optimize designs and processes for their manufacturing practices and the needs of varying end-use applications.

# MicroFET™ Package Outline Drawings

Fairchild's individual product data sheets reference the appropriate Fairchild package outline drawings. These in turn reference compliance to any applicable industry standard outlines. For MicroFET™ packages, the JEDEC MO-220 outline series generally applies. The MicroFET™ dimensions used in the land pattern design can be taken from these drawings.

# **General Design Guidelines**

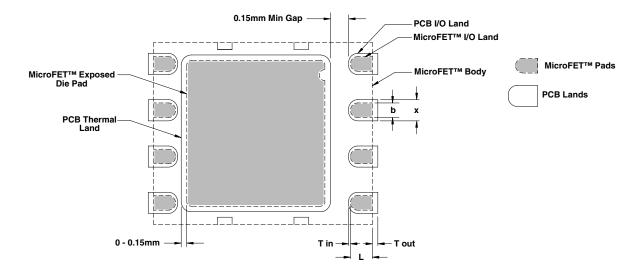

The MicroFET<sup>™</sup> die pad and perimeter I/O pads are fabricated from a planar copper lead-frame substrate. This is encapsulated in plastic with the bottom of the die pad and I/O pads exposed to create a very small footprint "exposed-pad" package. Both the I/O pads and die pad should be soldered to the PCB.

The corresponding PCB lands need to be designed to fit well within the PCB assembly process capabilities, as well as promote good long term solder joint reliability. Note that the process of soldering the exposed die pad "anchors" the package and provides important thermo-mechanical temperature cycling stress benefits that improve the reliability of the I/O pad solder joints.

The PCB "thermal land" design for the exposed die pad should include thermal vias that drop down and connect to buried metal plane(s). This combination of vias for vertical heat escape and buried planes for heat spreading allows the MicroFET™ to achieve its full thermal potential.

Figure 2. Typical MicroFET™ Land Pattern Layout with Package Overlay

# **Land Pattern Guidelines**

# Peripheral I/O Lands

The I/O lands should be a little larger on all sides than the package's I/O pads. Inward corners may be rounded to match the I/O pad shape. Design dimension guidelines are shown in Table 1. Typical package I/O pad dimensions are shown for reference only; and it should be noted that package outline drawings are the controlling specification for such package dimensions.

Table 1. Typical Pad and Land Dimension

| Typical Nominal Package I/O Pad Dimensions (mm) |                  |                   | I/O Land "Design Dimension" Guidelines (mm) |                          |                           |

|-------------------------------------------------|------------------|-------------------|---------------------------------------------|--------------------------|---------------------------|

| Pad Pitch                                       | Pad Width<br>(b) | Pad Length<br>(L) | Land Width (X)                              | Outward Extension (Tout) | Inward Extension<br>(Tin) |

| 1.27                                            | 0.40             | 0.6               | 0.49 Nom                                    | 0.15 Min                 | 0.05 Min                  |

|                                                 |                  |                   |                                             |                          |                           |

| 0.8                                             | 0.33             | 0.6               | 0.42 Nom                                    | 0.15 Min                 | 0.05 Min                  |

|                                                 |                  |                   |                                             |                          |                           |

| 0.65                                            | 0.28             | 0.6               | 0.37 Nom                                    | 0.15 Min                 | 0.05 Min                  |

|                                                 |                  |                   |                                             |                          |                           |

| 0.5                                             | 0.23             | 0.6               | 0.28 Nom                                    | 0.15 Min                 | 0.05 Min                  |

| 0.5                                             | 0.23             | 0.4               | 0.28 Nom                                    | 0.15 Min                 | 0.05 Min                  |

|                                                 |                  |                   |                                             |                          |                           |

| 0.4                                             | 0.20             | 0.6               | 0.25 Nom                                    | 0.15 Min                 | 0.05 Min                  |

| 0.4                                             | 0.20             | 0.4               | 0.25 Nom                                    | 0.15 Min                 | 0.05 Min                  |

With available PCB area, the outward extension (Tout) can be increased beyond 0.15mm as this could potentially improve this external solder joint. Any increase in the inward extension (Tin) above 0.05mm must consider the effect on the isolation gap to the thermal land.

#### **PCB Thermal Land**

The thermal land should be designed 0 to 0.15mm larger per side (0 to 0.30mm larger overall) than the package's exposed die pad. "Larger than", as opposed to the same size, is preferred.

But for package designs with die pad sizes near the maximum available for that package, whether or not the thermal land should be designed larger, or by how much, depends on your requirement for the isolation gap to the I/O lands. The recommended design gap is 0.15mm minimum. When space is available, a gap of 0.25mm or more is preferred. Don't make the thermal land so large that your desired gap is compromised.

#### **Thermal Vias**

A grid of 1.0mm to 1.2mm pitch thermal vias, which drop down and connect to buried copper plane(s), should be placed under the thermal land. The vias should be about 0.3mm to 0.33mm in diameter, with the barrel plated to about 1.0 ounce copper.

Although adding more vias (such as by decreasing via pitch) will improve thermal performance, diminishing returns will be seen as more and more vias are added. Therefore, simply use as many vias as practical for the thermal land size and your board design groundrules.

## Solder Mask Design

Two types of land patterns are used for surface mount packages:

- 1) Solder Mask Defined (SMD): Solder mask openings smaller than metal pads.

- 2) Non-Solder Mask Defined (NSMD): Solder mask openings larger than metal pads.

Better control of the copper etching process as compared to the solder masking process makes NSMD preferable. Also, the SMD pad definition can introduce stress concentrations near the solder mask overlap region that can result in solder joints cracking under extreme fatigue conditions. Using NSMD instead improves the reliability of solder joints as solder is allowed to "wrap around" the sides of the metal pads on the board.

For these reasons, NSMD is recommended for the perimeter I/O lands and generally for the thermal land; however SMD should be used on the thermal land when it is relatively large as discussed below.

For NSMD pads, the solder mask opening should be about 120µm to 150µm larger than the pad size, providing a 60µm to 75µm design clearance between the copper pad and solder mask. Rounded portions of package pads should have a matching rounded solder mask-opening shape, especially at corner leads to allow for enough solder mask web to prevent solder bridging.

Typically each pad on the PCB should have it's own solder mask opening with a web of solder mask between adjacent pads. However for 0.4mm pitch parts with an I/O land width of about 0.25mm, space may not be available for solder mask web in between the pads. In that case, use one big opening designed around a whole strip of pads (for instance all the pads on one side of a package) with no solder mask in between the pads.

For package designs with exposed die pad sizes near the maximum available for that package, the gap between the thermal land and I/O pads may be small. In this case there may be more potential for solder bridging, so the thermal land should be solder mask defined (SMD). The mask opening should be approximately 100µm smaller than the thermal land on all four sides, which increases the solder mask web between the thermal and I/O lands.

Solder masking is also required for thermal vias to prevent solder wicking inside the vias, drawing solder away from the thermal land-to-die pad interface. The solder mask diameter should be about 100µm larger than the via diameter. The vias can be plugged or tented with solder mask, either from the bottom or top surface of the PCB. Tenting from the top is considered a better option as it results in smaller voids under the die pad. Solder masking of vias from the bottom side can result in increased outgassing during reflow, creating bigger voids around vias. But note that small voids in this area are not unusual and will have little effect on thermal or electrical performance or on the reliability of the perimeter I/O pad solder joints.

## Stencil Guidelines

## Stencil Design for I/O Lands

Re-flowed solder joints on the perimeter I/O lands should have about a  $50\mu m$  to  $75\mu m$  (2 to 3 mil) standoff height and a good-sized fillet on the outside. The solder paste stencil design is the first step in developing such optimized, reliable joints.

Stencil aperture size-to-land size should typically be a 1:1 ratio. For finer pitch parts, especially as tight as 0.4mm, the aperture width may need to be reduced slightly to help prevent solder bridging between adjacent I/O lands.

#### Stencil Design for Thermal Land

To reduce solder paste volume on the thermal land, it is recommended that an array of smaller apertures be used instead of one large aperture. The smaller apertures can be circular or square and of various dimensions and array sizes; but the main goal should be a dimensional combination that results in 50 to 80% solder paste coverage. This reduced coverage on the thermal land is important in achieving good solder joints at the perimeter I/O lands.

## Stencil Type and Thickness

A laser-cut, stainless steel stencil with electropolished trapezoidal walls is recommended. Electropolishing "smooths" aperture walls, resulting in reduced surface friction, good paste release and void reduction. Using a trapezoidal section aperture (TSA) promotes paste release and also forms "brick-like" paste deposits that assist in firm component placement.

A 0.125mm stencil thickness is recommended for finer pitch packages (0.5mm and smaller), and this may be increased to 0.15mm to 0.2mm thickness for greater than 0.5mm pitch packages.

## Solder Paste and Reflow Profile

Due to the low mounted height of the MicroFET™, "No Clean" Type 3 paste per ANSI/J-STD-005 is recommended. Nitrogen purge is also recommended during reflow.

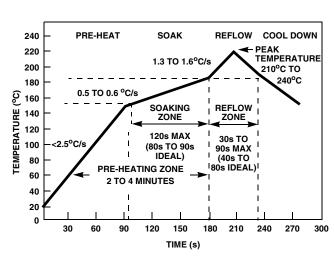

Figure 3. Typical Lead-Tin Solder Reflow Profile

A system board reflow profile depends on the thermal mass of the entire populated board, so it is not practical to define a specific soldering profile just for the MicroFET $^{\text{TM}}$ . The following profile is provided as a guideline, to be customized for varying manufacturing practices and applications.

## **Rework Guidelines**

After PCB assembly, the package should be inspected in transmission x-ray for the presence of voids, solder balling, or other defects underneath the package. Cross sectioning may also be required to determine the fillet shape and size, and the joint standoff height. In a MicroFET™, only the external side-fillet solder joint is exposed and any retouch is limited to this area. For rework of defects underneath the package, the whole package needs to be removed.

Removal and rework of MicroFET™ packages can be a challenge due to their small size and since they are commonly mounted on smaller, thinner, and denser PCBs. The following steps are provided as a guideline – a starting point in developing a successful rework process.

#### Bake

Before rework, bake the PCB assembly at 125C for at least 4 hours to remove any residual moisture.

## **Component Removal**

Ideally, the reflow profile for part removal should be similar to that used for part attachment. However, the time above liquidus can be reduced as long as the reflow is complete.

It is recommended that the board be heated from the bottom side using convective heaters and from the top side with hot gas nozzles directing heat at the component to be removed. Heating of adjacent components should be minimized. The MicroFET $^{TM}$  is small and light, so avoid excessive flow.

Once the joints have reflowed, remove the MicroFET™ with a vacuum lift-off. Because of the small package size, the vacuum pressure should be kept below 15" of Hg to help prevent premature lift-off (and possible PCB damage) before all joints have fully reflowed.

#### **Site Redress**

Clean the site properly, removing residual solder with a combination of a blade-style conductive tool and desoldering braid. After residual solder removal clean the lands with a solvent specific to the type of paste used in the original assembly.

# **Solder Paste Printing**

Use a miniature stencil specific to the component and align the stencil aperture under appropriate magnification (~50 to 100X). Lower the stencil onto the PCB and deposit the paste with a small squeegee blade. The blade width should be the same as the package width to ensure single pass paste deposition, avoiding any overprinting.

#### **Component Placement and Reflow**

Due to it's small mass, the MicroFET™ has good self-centering abilities during solder reflow, so the placement of this package should be similar to that of BGAs. The placement machine should have fine adjustment capability in the x, y, and rotational axes. Since the pads are on the underside of the package, use an optical system that can overlay an image of the solder paste pattern to aid in component alignment, which should be done at 50 to 100X magnification. Reflow the PCB using the same profile as that developed for the initial attachment.

# Acknowledgements

Many thanks to Jim Benson and Dennis Foster who completed the background work for this application note.

#### **TRADEMARKS**

The following are registered and unregistered trademarks Fairchild Semiconductor owns or is authorized to use and is not intended to be an exhaustive list of all such trademarks.

SMART START™  $VCX^{TM}$ FAST ® OPTOLOGIC™ STAR\*POWER™ FASTr™ Bottomless™ OPTOPLANAR™ Stealth™ CoolFET™ FRFET™ PACMAN™ SuperSOT™-3 CROSSVOLT™ GlobalOptoisolator™ POP™ SuperSOT™-6 DenseTrench™ GTO™ Power247™  $HiSeC^{TM}$ SuperSOT™-8  $Power Trench^{\, @}$ DOME™ SyncFET™ EcoSPARK™ ISOPLANAR™ QFET™ TinyLogic™ E<sup>2</sup>CMOS<sup>TM</sup> LittleFET™  $OS^{TM}$ TruTranslation™

STAR\*POWER is used under license

#### DISCLAIMER

FAIRCHILD SEMICONDUCTOR RESERVES THE RIGHT TO MAKE CHANGES WITHOUT FURTHER NOTICE TO ANY PRODUCTS HEREIN TO IMPROVE RELIABILITY, FUNCTION OR DESIGN. FAIRCHILD DOES NOT ASSUME ANY LIABILITY ARISING OUT OF THE APPLICATION OR USE OF ANY PRODUCT OR CIRCUIT DESCRIBED HEREIN; NEITHER DOES IT CONVEY ANY LICENSE UNDER ITS PATENT RIGHTS, NOR THE RIGHTS OF OTHERS.

#### LIFE SUPPORT POLICY

FAIRCHILD'S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF FAIRCHILD SEMICONDUCTOR CORPORATION. As used herein:

1. Life support devices or systems are devices or systems which, (a) are intended for surgical implant into the body, or (b) support or sustain life, or (c) whose failure to perform when properly used in accordance with instructions for use provided in the labeling, can be reasonably expected to result in significant injury to the

2. A critical component is any component of a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system, or to affect its safety or effectiveness.

## PRODUCT STATUS DEFINITIONS

## **Definition of Terms**

| Datasheet Identification | Product Status            | Definition                                                                                                                                                                                                            |  |

|--------------------------|---------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Advance Information      | Formative or<br>In Design | This datasheet contains the design specifications for product development. Specifications may change in any manner without notice.                                                                                    |  |

| Preliminary              | First Production          | This datasheet contains preliminary data, and supplementary data will be published at a later date. Fairchild Semiconductor reserves the right to make changes at any time without notice in order to improve design. |  |

| No Identification Needed | Full Production           | This datasheet contains final specifications. Fairchild Semiconductor reserves the right to make changes at any time without notice in order to improve design.                                                       |  |

| Obsolete                 | Not In Production         | This datasheet contains specifications on a product that has been discontinued by Fairchild semiconductor. The datasheet is printed for reference information only.                                                   |  |

Rev. H4

ON Semiconductor and in are trademarks of Semiconductor Components Industries, LLC dba ON Semiconductor or its subsidiaries in the United States and/or other countries. ON Semiconductor owns the rights to a number of patents, trademarks, copyrights, trade secrets, and other intellectual property. A listing of ON Semiconductor's product/patent coverage may be accessed at <a href="www.onsemi.com/site/pdt/Patent-Marking.pdf">www.onsemi.com/site/pdt/Patent-Marking.pdf</a>. ON Semiconductor reserves the right to make changes without further notice to any products herein. ON Semiconductor assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. Buyer is responsible for its products and applications using ON Semiconductor products, including compliance with all laws, regulations and safety requirements or standards, regardless of any support or applications information provided by ON Semiconductor. "Typical" parameters which may be provided in ON Semiconductor data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. ON Semiconductor does not convey any license under its patent rights nor the rights of others. ON Semiconductor products are not designed, intended, or authorized for use as a critical component in life support systems or any FDA Class 3 medical devices or medical devices with a same or similar classification in a foreign jurisdiction or any devices intended for implantation in the human body. Should Buyer purchase or use ON Semiconductor products for any such unintended or unauthorized application, Buyer shall indemnify and hold ON Semiconductor and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and exp

# **PUBLICATION ORDERING INFORMATION**

#### LITERATURE FULFILLMENT:

Literature Distribution Center for ON Semiconductor 19521 E. 32nd Pkwy, Aurora, Colorado 80011 USA Phone: 303-675-2175 or 800-344-3860 Toll Free USA/Canada Fax: 303-675-2176 or 800-344-3867 Toll Free USA/Canada Email: orderlit@onsemi.com N. American Technical Support: 800-282-9855 Toll Free USA/Canada

Europe, Middle East and Africa Technical Support: Phone: 421 33 790 2910

Japan Customer Focus Center

Phone: 81-3-5817-1050

ON Semiconductor Website: www.onsemi.com

Order Literature: http://www.onsemi.com/orderlit

For additional information, please contact your local Sales Representative