## Understanding a Digital Transistor Datasheet

### ON Semiconductor®

http://onsemi.com

### APPLICATION NOTE

#### Introduction

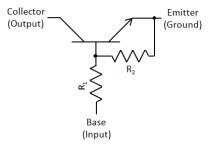

This application note will describe the common specifications of a Digital Transistor. It will also show how to use these specifications to successfully design with a Digital Transistor. Parameters from the DTC114E/D datasheet will be used to help with explanations. This datasheet describes a Digital Transistor that has an input resistor, R1, equal to  $10~k\Omega$  and a base–emitter resistor, R2, equal to  $10~k\Omega$ . Figure 1 gives a labeled schematic of a Digital Transistor. These labels will be used throughout this application note.

Figure 1. Labeled Schematic

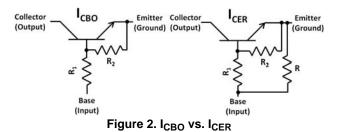

For Digital Transistors it is important to realize that the transistor and resistor network is considered as one unit. An example of this is the  $I_{CBO}$  parameter. Looking at this parameter one would think that it is not possible. How could the emitter be open when  $R_2$  connects the emitter and base of the transistor? Shouldn't it be  $I_{CER}$ ? The answer is yes  $R_2$  connects the emitter and base of the transistor, but this connection is built into the device. What is considered the emitter and base of the Digital Transistor is left open. In the case of a Digital Transistor  $I_{CER}$  would mean that there is an additional resistor placed between the emitter and base of the digital transistor. Figure 2 shows the difference between  $I_{CBO}$  and  $I_{CER}$  when referring to Digital Transistors.

### **Maximum Ratings**

Below is the maximum ratings table that can be found in every Digital Transistor datasheet.

**Table 1. MAXIMUM RATINGS**

| Rating                         | Symbol               | Max | Unit |  |

|--------------------------------|----------------------|-----|------|--|

| Collector-Base Voltage         | V <sub>CBO</sub>     | 50  | Vdc  |  |

| Collector–Emitter Voltage      | V <sub>CEO</sub>     | 50  | Vdc  |  |

| Collector Current – Continuous | I <sub>C</sub>       | 100 | mAdc |  |

| Input Forward Voltage          | V <sub>IN(fwd)</sub> | 40  | Vdc  |  |

| Input Reverse Voltage          | V <sub>IN(rev)</sub> | 10  | Vdc  |  |

Stresses exceeding those listed in the Maximum Ratings table may damage the device. If any of these limits are exceeded, device functionality should not be assumed, damage may occur and reliability may be affected.

The first spec,  $V_{CBO}$ , states that the maximum voltage that can be applied from the collector to the base is 50 V. The Collector–Emitter Voltage,  $V_{CEO}$ , spec states the maximum voltage that can be applied from the collector to emitter is 50 V. In addition, the table specifies that the maximum DC collector current ( $I_C$ ) that the device can conduct is 100 mA.

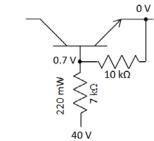

There are two maximum ratings for the input voltage, forward and reverse. The input voltage is defined as the voltage applied from the base and the emitter. The maximum input forward voltage is determined from the power capabilities of the input resistor,  $R_1.$  Figure 3 and Equations 1 and 2 describe how the maximum input forward voltage is calculated when the maximum power capability of  $R_1$  is 220 mW. It is important to use the minimum value of  $R_1$  because it will cause the greatest power to be dissipated on the die. The minimum value of  $R_1$  can be found in the Electrical Characteristics Table of every Digital Transistor datasheet. In this case  $R_{1(\text{min})}=7~\mathrm{k}\Omega.$  The resulting maximum input forward voltage is 40 V. For this particular device a voltage greater than this would result in the resistor failing.

Figure 3. Input Forward Voltage

$$P_{R1} = \frac{(V_{R1})^2}{R_1} \rightarrow V_{R1} = \sqrt{P_{R1} \times R_1}$$

$$= \sqrt{0.220 \times 7000} = 39.3 \text{ V}$$

(eq. 1)

$$V_{IN(max)} = V_{R1} + V_{BE} = 39.3 + 0.7 = 40 V$$

(eq. 2)

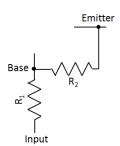

The maximum input reverse voltage is determined by the breakdown voltage of the base–emitter junction and the resistor network. The equivalent circuit in Figure 4 can be drawn when analyzing the maximum input reverse voltage and is justified by Equation 3. Looking at Figure 4 one sees that it is just a simple voltage divider. The voltage divider equation is shown in Equation 4. In applications where a large reverse voltage will be applied to the base–emitter junction it is recommended to use a Digital Transistor with a small  $R_2$  and large  $R_1$ . This will cause the majority of the voltage to be dropped across  $R_1$ , thus a smaller voltage will be dropped across  $R_2$  and consequently the base–emitter junction. The worst case for this spec is when  $R_1$  is at its minimum value and  $R_2$  is at its maximum value.

Figure 4. Input Reverse Voltage Equivalent Circuit

$$\begin{split} R_{\text{Equivalent}} &= R_{\text{BE}} / / R_2 = \left( \frac{1}{R_{\text{BE}}} + \frac{1}{R_2} \right)^{-1} \\ \text{When } R_{\text{BE}} & \gg R_2, \frac{1}{R_{\text{BE}}} + \frac{1}{R_2} = \frac{1}{R_2} \quad \text{(eq. 3)} \\ R_{\text{Equivalent}} &= \left( \frac{1}{R_2} \right)^{-1} = R_2 \\ V_{\text{B}} &= V_{\text{E}} \times \left( \frac{R_1}{R_1 + R_2} \right) \quad \text{(eq. 4)} \end{split}$$

### **Electrical Characteristics**

The first section of the Electrical Characteristics Table has specs pertaining to when the Digital Transistor is OFF. There are three leakage current parameters I<sub>CBO</sub>, I<sub>CEO</sub>, and I<sub>EBO</sub>.

For  $I_{CBO}$  and  $I_{CEO}$ , one can expect the leakage current to be below the value that is stated on the datasheet when a reverse voltage is applied between the respective junctions. However,  $I_{EBO}$  is dependent on both the input resistor and the base–emitter resistor. The resistor network path is significantly less resistive then the path through the reversed biased base–emitter junction. Ohm's Law is used to determine the  $I_{EBO}$  value. An example for a Digital Transistor with  $R_{1(min)} = 7 \, k\Omega$ ,  $R_{2(min)} = 7 \, k\Omega$ , and a  $V_{EB} = 6 \, V$  is shown below. It is important to note that the minimum value of  $7 \, k\Omega$  was used instead of  $10 \, k\Omega$ . This is done because it will estimate the largest possible leakage.

$$I_{\text{EBO}} = \frac{6 \text{ V}}{7 \text{ k}\Omega + 7 \text{ k}\Omega} = 0.43 \text{ mA}$$

(eq. 5)

Digital Transistors only specify the collector–base,  $V_{(BR)CBO}$ , and collector–emitter,  $V_{(BR)CEO}$ , breakdown voltages. These ensure that the device will have a breakdown voltage above the specified value.

The second section of the Electrical Characteristics Table describes specs for when the digital transistor is ON. Table 2 will be used as an example to help explain the following parameters. First, the DC Current Gain,  $h_{FE}$ , is a specification of how much the base current will be amplified in resulting collector current. The  $h_{FE}$  spec states that with an  $I_C=5.0\ mA$  and a  $V_{CE}=10\ V$  one can expect the gain to be around 60, but is ensured that it will be above 35. This means that the base current,  $I_B$ , will need to be 83  $\mu A$  if the typical gain of 60 is used.

$$I_B = \frac{I_C}{h_{FF}} = \frac{5 \text{ mA}}{60} = 83 \mu\text{A}$$

(eq. 6)

The next parameter is the Collector–Emitter Saturation Voltage,  $V_{CE(sat)}$ . This parameter tells the designer the maximum voltage drop that will occur when the device is ON. In this instance a maximum of 250 mV will be dropped across the transistor when the  $I_C=10$  mA and the base is driven with 0.3 mA ( $I_{FE}=33$ ). The  $I_{FE}$  spec can be seen as a threshold current ratio of base drive to collector current. If the base current is greater than the collector current divided by the  $I_{FE}$  spec then the transistor begins to saturate and the collector–emitter voltage drops to the saturation voltage.

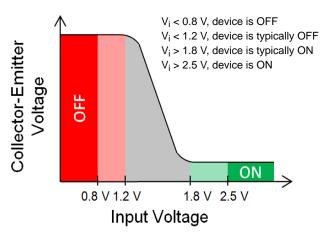

In most cases a Digital Transistor will be used as a switch. There are four parameters that characterize this operation: Input Voltage (off), Input Voltage (on), Output Voltage (on), and Output Voltage (off). The first parameter, Input Voltage (off), states that an input voltage less than 0.8 V will turn the device OFF ( $V_{CE} = 5$  V,  $I_{C} = 100 \,\mu\text{A}$ ). The Input Voltage (on) parameter defines that at a  $V_{CE} = 0.3$  V and  $I_{C} = 10$  mA a minimum input voltage of 2.5 V needs to be applied to turn the device ON. These two parameters also list typical values. These typical values are the measured voltages when the device is exactly at those ON and OFF conditions. It is not recommended to operate the device at these voltages if one wants to ensure the device is ON/OFF. Figure 5 gives a graphical representation of these specs.

### AND9129/D

Figure 5. Output Voltage vs. Input Voltage

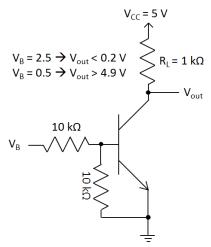

The output voltage of a switch is also very valuable to a designer. The Output Voltage (on),  $V_{OL}$ , spec states that the output voltage will be less than 0.2 V under the following conditions:  $V_{CC} = 5.0$  V,  $V_B = 2.5$  V,  $R_L = 1.0$  k $\Omega$ . The  $V_{OL}$  is similar to the  $V_{CE(sat)}$  of the device in that they both describe the maximum voltage that will be dropped across the collector—emitter when the Digital Transistor is in saturation(ON). The conditions for the Output Voltage (off),

$V_{OH}$ , spec are:  $V_{CC}$  = 5.0 V,  $V_B$  = 0.5 V,  $R_L$  = 1.0 k $\Omega$ . Under these conditions the output voltage will be greater than 4.9 V. Refer to Figure 6 for further understanding of the  $V_{OL}$  and  $V_{OH}$  specs.

Figure 6. Output Voltage Test Schematic

**Table 2. ELECTRICAL CHARACTERISTICS**

| Characteristics                                                                                         | Symbol                         | Min | Тур | Max  | Unit |

|---------------------------------------------------------------------------------------------------------|--------------------------------|-----|-----|------|------|

| OFF CHARACTERISTICS                                                                                     |                                |     |     | •    | •    |

| Collector-Base Cutoff Current (V <sub>CB</sub> = 50 V, I <sub>E</sub> = 0)                              | I <sub>CBO</sub>               | _   | _   | 100  | nAdc |

| Collector-Emitter Cutoff Current (V <sub>CE</sub> = 50 V, I <sub>B</sub> = 0)                           | I <sub>CEO</sub>               | -   | -   | 500  | nAdc |

| Emitter-Base Cutoff Current (V <sub>EB</sub> = 6 V, I <sub>C</sub> = 0)                                 | I <sub>EBO</sub>               | -   | -   | 0.5  | mAdc |

| Collector–Base Breakdown Voltage (I <sub>C</sub> = 10 μA, I <sub>E</sub> = 0)                           | V <sub>(BR)CBO</sub>           | 50  | -   | -    | Vdc  |

| Collector–Emitter Breakdown Voltage (I <sub>C</sub> = 2.0 mA, I <sub>B</sub> = 0)                       | V <sub>(BR)CEO</sub>           | 50  | _   | -    | Vdc  |

| ON CHARACTERISTICS                                                                                      |                                |     |     |      |      |

| DC Current Gain (I <sub>C</sub> = 5.0 mA, V <sub>CE</sub> = 10 V)                                       | h <sub>FE</sub>                | 35  | 60  | -    |      |

| Collector-Emitter Saturation Voltage (I <sub>C</sub> = 10 mA, I <sub>B</sub> = 0.3 mA)                  | V <sub>CE(sat)</sub>           | -   | -   | 0.25 | Vdc  |

| Input Voltage (off) ( $V_{CE} = 5.0 \text{ V}$ , $I_{C} = 100 \mu\text{A}$ )                            | V <sub>i(off)</sub>            | -   | 1.2 | 0.8  | Vdc  |

| Input Voltage (on) ( $V_{CE} = 0.3 \text{ V}$ , $I_{C} = 10 \text{ mA}$ )                               | V <sub>i(on)</sub>             | 2.5 | 1.8 | -    | Vdc  |

| Output Voltage (on) (V <sub>CC</sub> = 5.0 V, V <sub>B</sub> = 2.5 V, R <sub>L</sub> = 1.0 k $\Omega$ ) | V <sub>OL</sub>                | -   | _   | 0.2  | Vdc  |

| Output Voltage (off) (V <sub>CC</sub> = 5.0 V, $V_B$ = 0.5 V, $R_L$ = 1.0 k $\Omega$ )                  | V <sub>OH</sub>                | 4.9 | _   | -    | Vdc  |

| Input Resistor                                                                                          | R <sub>1</sub>                 | 7.0 | 10  | 13   | kΩ   |

| Resistor Ratio                                                                                          | R <sub>1</sub> /R <sub>2</sub> | 0.8 | 1.0 | 1.2  |      |

Product parametric performance is indicated in the Electrical Characteristics for the listed test conditions, unless otherwise noted. Product performance may not be indicated by the Electrical Characteristics if operated under different conditions.

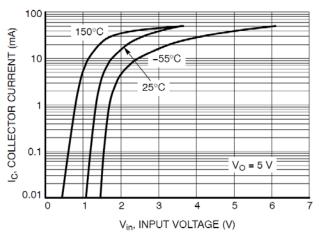

There are two curves present on all Digital Transistor datasheet that provide more data on the  $V_{i(on)}$  and  $V_{i(off)}$  parameters. The first is the Output Current vs. Input Voltage, Figure 7. This curve characterizes the  $V_{i(off)}$  parameter, and the data was taken when the  $V_{CE}$  or the output voltage is 5 V. One can use this curve to determine at what voltage the current will drop rapidly, or in other words turn OFF. For this device the voltage at which the current rapidly drops off is around 1.4 V at 25°C.

Figure 7. Output Current vs. Input Voltage

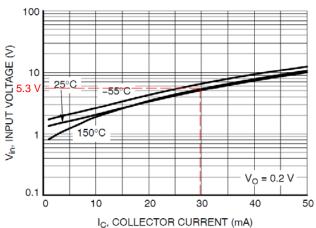

The other datasheet curve is the Input Voltage vs. Output Current, Figure 8. This curve characterizes the  $V_{i(on)}$  parameter and the data was taken with the  $V_{CE} = 0.2$  V. This chart provides the designer the voltage needed for a desired collector current while maintaining an output voltage of 0.2 V. For example, to operate the device characterized in Figure 8 at an  $I_C$  of 30 mA and a  $V_{CE}$  of 0.2 V, an input voltage of 5.3 V would need to be applied.

Figure 8. Input Voltage vs. Output Current

The last two parameters describe the built in resistors of the Digital Transistor. First, is the typical  $R_1$  value along with the minimum and maximum values that are  $\pm 30\%$  of the typical value. The typical resistor ratio of  $R_1/R_2$  is also defined along with a minimum and maximum spec of  $\pm 20\%$  of the typical value. The actual value of  $R_2$  is not defined

because the ratio of  $R_1/R_2$  is more pertinent when designing with Digital Transistors. The  $R_1/R_2$  ratio is what controls the critical parameters of the Digital Transistor. However, if desired it is possible to calculate the minimum and maximum values of  $R_2$ . Equations 7 and 8 help explain how to do this using the values in Table 2.

$$R_{2(min)} = \frac{R_{1(min)}}{(R_1/R_2)_{max}} = \frac{7 \text{ k}\Omega}{1.2} = 5.8 \text{ k}\Omega$$

(eq. 7)

$$R_{2(max)} = \frac{R_{1(max)}}{(R_1/R_2)_{min}} = \frac{13 \text{ k}\Omega}{0.8} = 16.3 \text{ k}\Omega \text{ (eq. 8)}$$

# Example of Designing with Digital Transistor Datasheet

Design requirements:

Polarity: NPN

$I_C = 10-20 \text{ mAdc}$

$V_{CE(max)} = V_{CB(max)} = 40 \text{ Vdc}$

$V_{IN(fwd)} = 20 \text{ Vdc}$

$V_{IN(rev)} = 10 \text{ Vdc}$

Micro controller output voltage:

Off: 0.4–0.6 V On: 1.5–4.2 V

Micro controller max output current: 250 µA

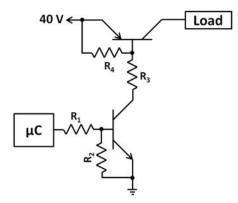

Figure 9. Schematic for Example

Now that the design requirements have been established it is time to indentify the Digital Transistor that works best for the application. Table 3 will help with this selection. The first step should be to find a Digital Transistor that meets the max current and voltage requirements. The majority of Digital Transistors within ON Semiconductors portfolio are rated at 100 mA. The remaining Digital Transistors are rated above 100 mA. Also, the majority of them have a  $V_{\rm CEO}$  and  $V_{\rm CEO}$  of 50 V, which will meet the above requirement.

Next, is to find a Digital Transistor that meets the forward and reverse input voltage requirements. Using Table 3 it is seen that the  $V_{IN(fwd)}$  requirement of 20 V is reached by all digital transistors except for ones that have a  $R_1$  of 1 k $\Omega$  or 2.2 k $\Omega$ . Digital Transistors with a  $R_1/R_2 \ge 1$  will meet the 10 V requirement for  $V_{IN(fev)}$ .

### AND9129/D

The next requirement to look at is  $V_{i(off)}$ . In the design requirements it states that the micro controller will give a voltage of 0.4–0.6 V when it wants the Digital Transistor to be OFF. This eliminates the Digital Transistors that have a maximum  $V_{i(off)}$  spec of 0.5 V because these should be supplied with a voltage of less than 0.5 V when the device is desired to be OFF.

The design requirements also state that the maximum output voltage of the micro controller is 4.2 V. A Digital Transistor needs to be selected that can provide a maximum  $I_C$  of 20 mA when the input voltage is 4.2 V. It also has to provide an  $I_C$  of 10 mA with an input voltage of greater than 1.5 V. Looking at the Input Voltage vs. Output Current charts of the four remaining Digital Transistors only two meet the input voltage requirements. They are the Digital Transistors with  $R_1/R_2=10~k\Omega/10~k\Omega$  and  $22~k\Omega/22~k\Omega$ .

It is also important to consider the max output current of the controller. In this case the micro controller can source a maximum of 250  $\mu A$ . For the 10  $k\Omega/10~k\Omega$  digital transistor

the typical voltage needed to drive an  $I_C$  of 20 mA is 3.3 V. In this case the micro controller would have to source approximately 260  $\mu A$  which is above the max output current of the micro controller.

$$\frac{3.3 \ V - 0.7 \ V}{10 \ k\Omega} = 260 \ \mu A \ \equad (eq. 9)$$

However, for the  $22k\Omega/22k\Omega$  the typical voltage needed for an  $I_C$  of 20 mA is 3.8 V resulting in a current of 140  $\mu$ A.

$$\frac{3.8 \; \text{V} - 0.7 \; \text{V}}{22 \; \text{k}\Omega} = 140 \; \mu \text{A} \tag{eq.} \label{eq.} \tag{10}$$

After considering all the design requirements it is found that the Digital Transistor that will work best for this specific application is the Digital Transistor with  $R_1/R_2 = 22 \ k\Omega/22 \ k\Omega$ . The final step would be to pick the package. ON Semiconductor offers single Digital Transistors in six packages ranging from SC-59 to SOT-1123.

**Table 3. INPUT VOLTAGE SPECIFICATIONS**

|         |         | V <sub>IN(fwd)</sub> (V) |     | V <sub>IN(rev)</sub> (V) |     | V <sub>i(on)</sub> (V) |             | V <sub>i(off)</sub> @ 0.1 mA (V) |     |

|---------|---------|--------------------------|-----|--------------------------|-----|------------------------|-------------|----------------------------------|-----|

| R1 (kΩ) | R2 (kΩ) | PNP                      | NPN | PNP                      | NPN | PNP                    | NPN         | PNP                              | NPN |

| 1       | 1       | 10                       | 10  | 10                       | 10  | 2.0 @ 20 mA            | 2.0 @ 20 mA | 0.5                              | 0.5 |

| 2.2     | 2.2     | 12                       | 12  | 10                       | 10  | 2.0 @ 20 mA            | 2.0 @ 20 mA | 0.5                              | 0.5 |

| 4.7     | 4.7     | 30                       | 30  | 10                       | 10  | 3.0 @ 20 mA            | 2.5 @ 20 mA | 0.5                              | 0.5 |

| 10      | 10      | 40                       | 40  | 10                       | 10  | 2.5 @ 10 mA            | 2.5 @ 10 mA | 0.8                              | 0.8 |

| 22      | 22      | 40                       | 40  | 10                       | 10  | 2.5 @ 5 mA             | 2.5 @ 5 mA  | 0.8                              | 0.8 |

| 47      | 47      | 40                       | 40  | 10                       | 10  | 3.0 @ 2 mA             | 3.0 @ 2 mA  | 0.8                              | 0.8 |

| 100     | 100     | 40                       | 40  | 10                       | 10  | 3.0 @ 1 mA             | 3.0 @ 1 mA  | 0.5                              | 0.5 |

| 2.2     | 47      | 12                       | 12  | 5                        | 6   | 1.1 @ 5 mA             | 1.1 @ 5 mA  | 0.5                              | 0.5 |

| 4.7     | 47      | 30                       | 30  | 5                        | 6   | 1.3 @ 5 mA             | 1.3 @ 5 mA  | 0.5                              | 0.5 |

| 10      | 47      | 40                       | 40  | 6                        | 7   | 1.4 @ 1 mA             | 1.4 @ 1 mA  | 0.5                              | 0.5 |

| 22      | 47      | 40                       | 40  | 7                        | 8   | 2.0 @ 2 mA             | 2.0 @ 2 mA  | 0.5                              | 0.5 |

| 47      | 22      | 40                       | 40  | 10                       | 10  | 4.0 @ 2 mA             | 4.0 @ 2 mA  | 1.2                              | 1.2 |

| 2.2     | Inf.    | 12                       | 12  | 5                        | 6   | 1.3 @ 10 mA            | 1.1 @ 10 mA | 0.5                              | 0.5 |

| 4.7     | Inf.    | 30                       | 30  | 5                        | 6   | 1.3 @ 10 mA            | 1.3 @ 10 mA | 0.5                              | 0.5 |

| 10      | Inf.    | 40                       | 40  | 5                        | 6   | 1.7 @ 10 mA            | 1.7 @ 10 mA | 0.5                              | 0.5 |

| 47      | Inf.    | 40                       | 40  | 5                        | 6   | 4.0 @ 10 mA            | 4.0 @ 10 mA | 0.5                              | 0.5 |

| 100     | Inf.    | 40                       | 40  | 5                        | 6   | 1.5 @ 1 mA             | 1.5 @ 1 mA  | 0.5                              | 0.5 |

### Conclusion

Throughout this application note the characteristics of Digital Transistors have been discussed. These characteristics range from the maximum ratings to the input/output characteristics. It was shown how the resistor network of Digital Transistors determines the input voltage characteristics. ON Semiconductor understands that having

a variety of resistor combinations is pivotal in helping designers fulfill their design requirements. This is why ON Semiconductor has worked to provide a complete portfolio of Digital Transistors. Please visit <a href="https://www.onsemi.com">www.onsemi.com</a> to explore ON Semiconductor's Digital Transistor Portfolio.

### AND9129/D

ON Semiconductor and in are registered trademarks of Semiconductor Components Industries, LLC (SCILLC). SCILLC owns the rights to a number of patents, trademarks, copyrights, trade secrets, and other intellectual property. A listing of SCILLC's product/patent coverage may be accessed at www.onsemi.com/site/pdf/Patent-Marking.pdf. SCILLC reserves the right to make changes without further notice to any products herein. SCILLC makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does SCILLC assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. "Typical" parameters which may be provided in SCILLC data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. SCILLC does not convey any license under its patent rights nor the rights of others. SCILLC products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the SCILLC product could create a situation where personal injury or death may occur. Should Buyer purchase or use SCILLC products for any such unintended or unauthorized application, Buyer shall indemnify and hold SCILLC and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that SCILLC was negligent regarding the design or manufacture of the part. SCILLC is an Equal Opportunity/Affirmative Action Employer. This literature is subject to all applicable copyright laws and is not for resale in any manner.

### **PUBLICATION ORDERING INFORMATION**

#### LITERATURE FULFILLMENT:

Literature Distribution Center for ON Semiconductor P.O. Box 5163, Denver, Colorado 80217 USA Phone: 303-675-2175 or 800-344-3860 Toll Free USA/Canada Fax: 303-675-2176 or 800-344-3867 Toll Free USA/Canada

Email: orderlit@onsemi.com

N. American Technical Support: 800-282-9855 Toll Free USA/Canada

Europe, Middle East and Africa Technical Support: Phone: 421 33 790 2910

Japan Customer Focus Center Phone: 81-3-5817-1050

ON Semiconductor Website: www.onsemi.com

Order Literature: http://www.onsemi.com/orderlit

For additional information, please contact your local Sales Representative