### Is Now Part of

# ON Semiconductor®

To learn more about ON Semiconductor, please visit our website at <a href="https://www.onsemi.com">www.onsemi.com</a>

ON Semiconductor and the ON Semiconductor logo are trademarks of Semiconductor Components Industries, LLC dba ON Semiconductor or its subsidiaries in the United States and/or other countries. ON Semiconductor owns the rights to a number of patents, trademarks, copyrights, trade secrets, and other intellectual property. A listing of ON Semiconductor's product/patent coverage may be accessed at www.onsemi.com/site/pdf/Patent-Marking.pdf. ON Semiconductor reserves the right to make changes without further notice to any products herein. ON Semiconductor makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does ON Semiconductor assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. Buyer is responsible for its products and applications using ON Semiconductor products, including compliance with all laws, regulations and safety requirements or standards, regardless of any support or applications information provided by ON Semiconductor. "Typical" parameters which may be provided in ON Semiconductor data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. ON Semiconductor does not convey any license under its patent rights nor the rights of others. ON Semiconductor products are not designed, intended, or authorized for use as a critical component in life support systems or any EDA Class 3 medical devices with a same or similar classification in a foreign jurisdiction or any devices intended for implantation in the human body. Should Buyer purchase or use ON Semiconductor products for any such unintended or unauthorized application, Buyer shall indemnify and hold ON Semiconductor and its officers, employees, emplo

# AN-9005 快速开关超结 MOSFET 的驱动和布局设计

### 摘要

功率 MOSFET 技术继续朝着更高单元密度和低导通电阻 发展。然而,由于导通电阻的大小会随阻断电压的增大而呈指数增长,因此使用传统平面 MOSFET 技术显著减小导通电阻时就存在硅限制。克服硅限制的其中一个努力是在高电压功率 MOSFET 中采用超级结技术。超级结技术可同时显著降低导通电阻和寄生电容,而其通常存在权衡取舍。由于寄生电容较小,这些超级结 MOSFET 具有极快的开关特性,从而可以降低开关损耗。当然,这种开关行为会产生 较大的dv/dt 和 di/dt 通过器件和印制电路板中的寄生元件影响开关性能。开关行为还与系统的 EMI 性能有关。因此,优化的设计对操作高速 MOSFET 非常重要。本应用指南的目的是讨论与快速开关 MOSFET 开关性能有关的驱动方法和布局要求。

## 简介

开关器件的功率损耗可以分为四部分: 导通损耗、开关损耗、由漏电流产生的关断状态损耗,以及驱动损耗。在采用高压开关器件的开关电源应用中,最后两部分损耗可以忽略。可以通过最小导通电阻,降低导通损耗。开关损耗取决于开关转换时段,在该时段,电流和电压同时通过器件沟道。开关转换时段越短,开关动中。还有极小电压同时通过器件沟道。开关转换时段越短,开关对心寄生电容。因此,大量工作集中在改善导通电阻和电容上。连续几代超级结 MOSFET 技术已显著减少了晶极电告定的导通电阻 (Rom,sp)[1]-[2]。通过降低 Roscon 和栅极电荷 (Qo) 能够实现更小的裸片和更快的开关性能。然而,电压和电流的尖锐过渡导致高频噪音和辐射型 EMI。

为了降低噪音辐射,需要较高的寄生电容值。寄生电容要求存在直接的冲突。根据最近的系统趋势,提高效率是关键目标,而仅仅为了减少 EMI 而降低开关器件的速度并不是最佳解决方案。本指南说明在设计快速开关电源器件时,如何权衡这些考虑因素。

### 超级结 MOSFET 技术

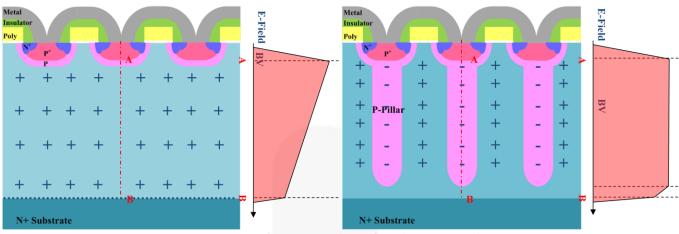

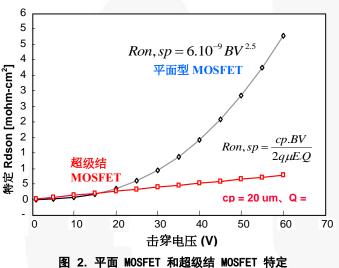

通常认为 R<sub>DS (ON) x OG</sub>, 即品质因数 (FOM) 是开关电源 (SMPS) MOSFET 最重要的单项性能指标。因此,已经开发出数项提高 R<sub>DS (ON)</sub> x Q<sub>G</sub> FOM 的新技术。10 年前,采用电荷平衡理论的超级结器件就已引入到半导体行业,为高电压功率 MOSDFET 市场设定了新基准<sup>[3]</sup>图 1。显示了平面型 MOSFET 和超级结 MOSFET 的垂直结构和电场分布。平面型 MOSFET 的击穿电压取决于漂移层掺杂度及其厚度。电场分布的斜率与漂移层掺杂度成正比。因此,需要较厚且轻掺杂的 EPI 来支持更高的击穿电压。高压 MOSFET 的导通电阻主要来自漂移区。因此,导通电阻随较厚且轻掺杂的漂移层呈指数增加,从而实现较高的击穿电压,如图 2所示。

与传统平面技术的井状结构相比,超级结技术体中有较深的P-型柱状结构。柱状结构可有效限制轻掺杂 epi 区域中的电场。由于采用这种P-型柱状结构,与传统平面结构相比,N-型 EPI 的电阻显著减少,同时维持了同等的击穿电压。因此,这种新技术打破了导通电阻方面的硅限制,并且与传统平面工艺相比,实现了单位面积的导通电阻仅为原来的1/3<sup>[4]</sup>。众所周知,该技术还提供独特的非线性寄生电容性能并能够减少开关功率损耗。

图 1. 平面型 MOSFET (左) 和超级结 MOSFET (右)

图 2. 平面 MOSFET 和超级结 MOSFET 特定 Roscom 与击穿电压曲线图

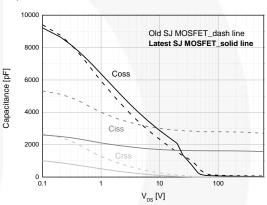

# MOSFET 中的功率损耗

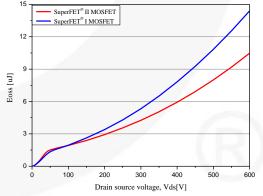

采用电荷平衡理论的超级结器件能够显著减少高电压 MOSFET 的导通电阻。由于导通损耗与导通电阻成正比 , 超级结器件如 SupreMOS®在导通损耗方面具有很大的 优势。开关转换时段越短, 开关功率损耗就越低。由于 MOSFET 是单极器件,寄生电容是开关转换的唯一限制 因素。若要降低开关损耗,需要降低寄生电容。 [5] 与标 准 MOSFET 技术相比, 电荷平衡原理能够降低单位面积 的导通电阻,并能够在 Roscon相同时缩减芯片尺寸。如 图 3所示,与前一代相比,最新的超级结 MOSFET 输 入电容和米勒电容都显著降低。然而,输出电容曲线相 差不大。最新的超级结 MOSFET 仅表现出更高的非线性 程度。若要弄清楚输出电容与开关损耗之间的对应关系 ,一种可能的方法是评估输出电容的有效值。计算 MOSFET 输出电容中存储能量的方法是, 在导通转换之 前对输出电容和漏源极电压(即从零到漏源极之间的漏 源极电压)乘积作积分运算。所存储的能量在开关周期 每个导通时段通过 MOSFET 沟道分散。SuperFET® II

MOSFET 输出电容的存储能量,与前一代 SuperFET® I MOSFET (用于典型开关电源大容量电容电压)类似的导通电阻器件相比,减少了约 27%。输出电容中的存储能量基准,如图 4 所示。

图 3. SuperFET\* | MOSFET 与 SuperFET\* | I MOSFET 电容比较

图 4. 输出电容中的存储能量

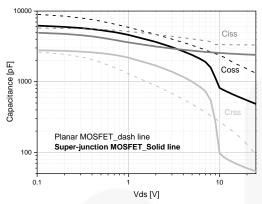

图 5显示超级结 MOSFET 和平面型 MOSFET 的电容。超级结 MOSFET 的  $C_{ISS}$  基本保持不变,而超级结 MOSFET 的 CRSS和  $C_{OSS}$  表现出很强的非线性程度。 $C_{RSS}$  在约 10 V 漏源极电压处迅速降低。这些效应允许极快的 dv/dt 和 di/dt。快速开关速度损耗能够降低开关损耗,但也有负面效应,如增加了 EMI、栅极振荡和较

高的漏源极电压峰值。因此,控制最大开关速度对于获取不带负面效应的超级结 MOSFET 极端性能来说非常重要。

图 5. 平面型 MOSFET 和超级结 MOSFET 之间的电容比较

### 电路参数对开关特性的影响

开关速度更快的功率 MOSFET 可以实现更高的功率转换效率。但是,随着开关速度的提高,装置和电路板上的寄生元件对开关特性的影响也随之加大。从而带来一些副作用,比如出现电压/电流尖峰或 EMI 性能恶化。由于功率 MOSFET 是栅极控制型器件,所以实现平衡的重点在于优化栅极驱动电路。最大限度地减少印制电路板上的寄生电感和电容同样重要。

### 栅极电阻的影响

栅极驱动设计中的一个关键控制参数为外部串联栅极电阻( $R_s$ )。这些栅极电阻能够抑制漏源极峰值电压并能够防止功率 MOSFET 中导线电感和寄生电容产生的栅极振荡。还能够在导通和关断期间减缓电压和电流上升速度(dv/dt)和(di/dt)。然而, $R_s$ 影响 MOSFET 中的开关损耗。由于器件需要在目标应用中达到最高效率,因此控制损耗非常重要。因此,从应用角度讲,选择优化的  $R_s$ 非常重要。 $R_s$ 值过小会造成 MOSFET 开关关闭时漏源极间的 dv/dt 过高,因此下限值就是为保证开关的 dv/dt 符合数据表中的规格要求。 $R_s$ 值过大会增加损耗,并降低效率;因此选择的上限值应确保与超级结 MOSFET 或竞争产品的前一版本有相似的开关损耗。

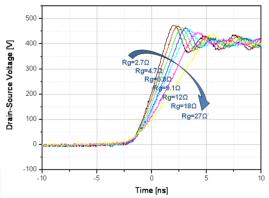

图 6. 栅极电阻不同时对应 MOSFET的漏源极波形。

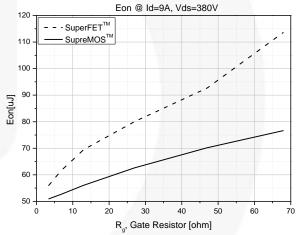

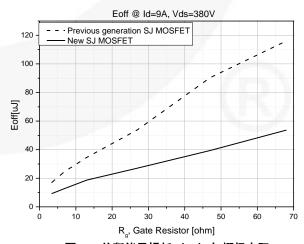

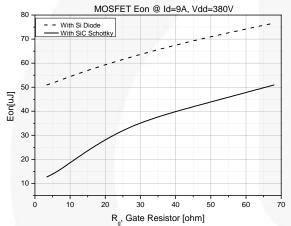

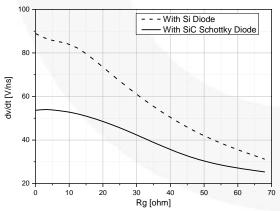

图 6 显示了不同栅极电阻下 MOSFET 的关断响应时间。如果用超级结 MOSFET 直接取代平面型 MOSFET 或其他前一代功率 MOSFET,可降低开关损耗,但 dv/dt 会增大。若要控制超级结 MOSFET,需要更大的  $R_s$ 。在这种情况下,应该限制  $R_s$ 图 7的增大量,否则超级结 MOSFET 的开关损耗会增大。图 8 显示前一代超级结 MOSFET 的开关损耗,显示新一代超级结 MOSFET 的开关损耗。根据这些图,可以选择开关损耗类似或更少并且 dv/dt 受控的  $R_s$ 。

图 7. 导通能量损耗 (Eon) 与栅极电阻

图 8. 关断能量损耗 (E<sub>off</sub>) 与栅极电阻

### 箝位二极管的影响

MOSFET 的导通特性很大程度上受控于箝位感应开关上 续流二极管的反向恢复特性。在 Si 二极管突然反向偏 置时,大量尚未在耗尽层重组的存储电荷可能在阻断反 向电压前流入相反方向。SiC 肖特基二极管在开关过渡 过程中没有反向恢复电流,原因是不存在过多的少数载 流子。然而, 却存在寄生结电容中的位移电流, 可以忽 略不计。因此,采用 SiC 肖特基二极管和 Si 二极管 作为箝位二极管, 因为瞬间行为中反向恢复特性的巨大 差别导致 MOSFET 开关损耗和 dv/dt 也有显著不同。 图 9 显示采用不同外部栅极电阻和不同的箝位二极管 时的导通开关损耗。与 Si 二极管相比, 使用 SiC 肖 特基二极管时, dv/dt 较低, 原因在于 SiC 具有较高 的结电容,如 图 10 所示。在漏极电流较低 R<sub>s</sub>较小 时, dv/dt值的间隙会加大。因此在低电流的情况下, dv/dt相对较低, MOSFET的输出电容和二极管结电容对 dv/dt的影响加大。

图 9. 采用不同箝位二极管时,超级结 MOSFET 的导通能量损耗(E<sub>ov</sub>)

图 10.采用不同箝位二极管时,超级结 MOSFET 的关断 dy/dt

#### 铁氧体磁芯的影响

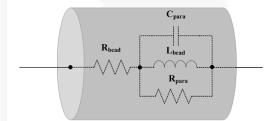

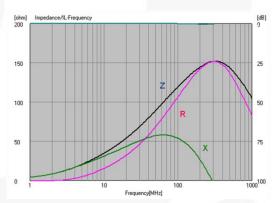

经追踪, 主要噪声源来自开关瞬间 MOSFET 中的振荡。 通常来说,寄生振荡频率在几十到几百兆赫兹范围内。 寄生振荡可能导致栅源极电压击穿、EMI性能恶化、较 大的开关损耗、栅极失控,甚至可能导致 MOSFET 失效 。通常在 MOSFET 栅极引线上使用铁氧体磁珠, 抑制寄 生振荡, 同时最大限度地降低开关损耗, 从而保证稳定 运行。事实上,添加铁氧体磁珠比单独使用栅极电阻更 加有效, 这是因为铁氧体磁珠的阻抗随频率变化。图 11 显示铁氧体磁珠的等效电路,图 12 显示作为频率 函数的阻抗性能。Rbad 和 Lbad 分别为铁氧体磁珠的直 流电阻和有效电感。 coara 和 Roara 为与铁氧体磁珠有关的 并联电容和电阻。简单来说,铁氧体磁珠是跟频率相关 的电阻。低频时, Cpara 为开路而 Lbead 为短路, 仅留 Rbead 作为铁氧体磁珠的直流电阻。随着频率增大, Lbead的阻 抗开始随频率 (jωL<sub>bead</sub>) 线性增大, 而 Cpara的阻抗与 频率 (1/ jωC<sub>para</sub>) 成反比降低,如方程式(1) 所示:

$$Z = R + jX \tag{1}$$

图 11. 铁氢体磁珠的等效电路

图 12.阻抗特性与频率

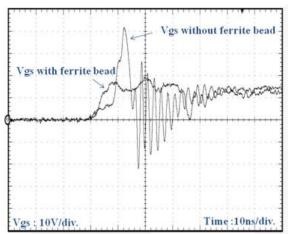

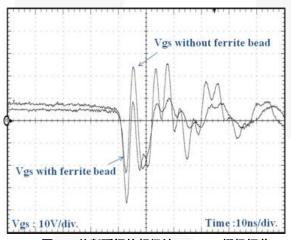

铁氧体阻抗与频率曲线的上升线性斜率主要取决于 Lbad 的电感。在某特定高频点上,Cpara 的阻抗开始占据主导地位,而铁氧体阻抗开始减小,与电感相反。在这种情况下,阻抗与频率曲线的下降斜率主要取决于磁珠的寄生电容 Cpara。低频时,感性阻抗较低。因此,铁氧体磁珠电感的功能类似于电阻,而不是高频时的电感。一般情况下,寄生振荡频率比开关频率高得多。高频时的高阻抗对于阻断漏栅极噪声极其有效。如果铁氧体中有足够的电感,结合电阻,可以明显抑制高频寄生振荡。图 13 和 图 14 显示采用不同铁氧体磁珠时的栅极振荡

比较。通过在 MOSFET 栅极导线上应用铁氧体磁珠能够 大幅抑制振荡。这是解决某些应用中振荡问题的一种非 常简单并且能够节约成本的方式。通过铁氧体磁珠电感 ,阻抗随材料和内部结构而变化。当选择一个铁氧体磁 珠时,有必要考虑噪声频段阻抗、额定电流和阻抗梯度

图 13.导通瞬间的超级结 MOSFET 栅极振荡 V<sub>ss</sub>

图 14.关断瞬间的超级结 MOSFET 栅极振荡 V。。

### 驱动器 IC 电流能力的影响

驱动器是控制电路和功率 MOSFET 之间的接口。驱动电路放大控制信号至所需电平,从而驱动功率 MOSFET,并在必要情况下提供功率 MOSFET 和逻辑电平控制电路(比如桥式拓扑中的高端开关)之间的电子隔离。驱动器的主要功能是将 MOSFET 从关断状态切换到导通状态,或从导通状态切换到关断状态。高功率应用中需要高峰值电流,因此能够为寄生电容尽快充放电,从而提高MOSFET 的开关效率。开关行为和功率耗散取决于输出驱动器的电流能力,而 MOSFET 栅源极电压介于阀值电平和米勒效应平台电压之间。Table 1 显示了驱动 IC峰值灌电流和源电流能力之间的比较。

Table 1. 栅极驱动器关键规格比较

| 设备       | 条件                                                               | I <sub>PK_SINK</sub> | I PK_SOURCE |

|----------|------------------------------------------------------------------|----------------------|-------------|

| FAN3122T | $C_{LOAD} = 1.0 \mu F, f = 1 \text{ kHz}, V_{DD} = 12 \text{ V}$ | 11.4 A               | -10.6 A     |

| FAN3224T | $C_{LOAD} = 1.0 \mu F, f = 1 \text{ kHz}, V_{DD} = 12 \text{ V}$ | 5. 0 A               | -5.0 A      |

| FAN3111C | $C_{LOAD} = 1.0 \mu F, f = 1 \text{ kHz}, V_{DD} = 12 \text{ V}$ | 1.4 A                | -1.4 A      |

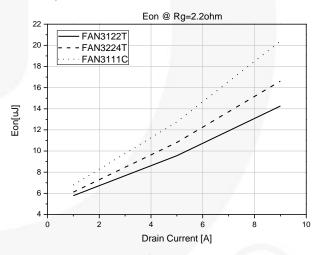

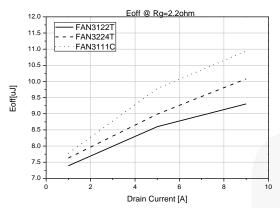

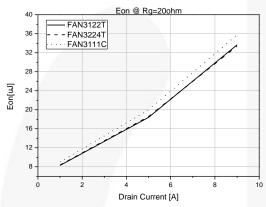

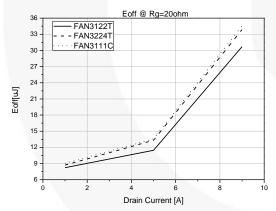

图 15 - 图 18图 25 显示可以通过高电流驱动器减少的开关损耗量。采用较大栅极电阻时,开关电阻差距不是很大,因为栅极电阻会限制栅极电流。

图 15.导通能量损耗 (E<sub>ok</sub>) 与 R<sub>e</sub>= 2.2 Ω 的栅极驱动器

图 16.关断能量损耗 (E<sub>oF</sub>) 与 R<sub>c</sub>= 2.2 Ω 的栅极驱动器

图 17.导通能量损耗 (E<sub>ok</sub>) 与 R<sub>e</sub>= 20 Ω 的栅极驱动器

图 18.关断能量损耗 (E<sub>oF</sub>) 与 R<sub>e</sub>= 20 Ω 的栅极驱动器

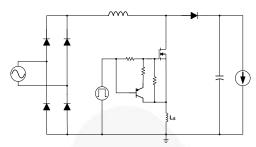

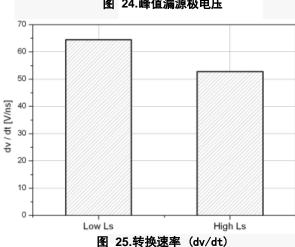

### 源电感的影响

交错式 CRM PFC

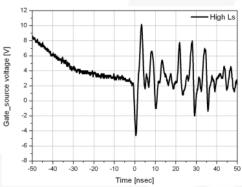

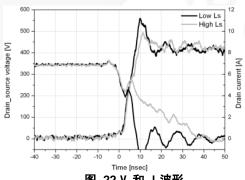

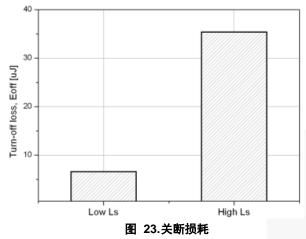

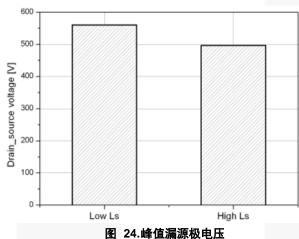

电路中需要考虑共源电感的两种不同情况, 因为必须通 过共源电感对开关行为进行平衡。图 19

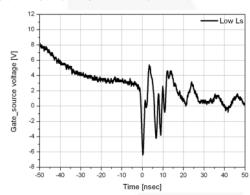

显示考虑了共源电感的两相交错式 CRM PFC 电路的单相。Ls

值较低的电路中, 尽管由于快速转换速度导致栅源极负 电压和漏源极过冲电压会稍高, 但其关断损耗和栅极振 荡都较低。相反,L。

值较高的电路中,关断损耗和栅极振荡较高,

而由于较慢的压摆率漏源极击穿电压较低,如 图 20 - 图

25 所示。由于对接中存在寄生元件,超级结 MOSFET 的极快开关速度可能导致开关过程中出现严重的电压和 电流振荡。在应用中,这些对接通常包括印制电路板、 元件引线、线缆和导线等。对接导致的问题通常受控于 杂散电感, 而非杂散电容, 尤其是在中低压电源中。减 少开关噪声的最佳方式是最大限度地减少共源电感。

图 19.考虑了共源电感的交错式 CRM PFC 电路的单相

图 20.LS值较低的V。波形

图 21.LS值较高的 Vs.波形

图 22. V₀ 和 I₀波形

#### 栅极驱动电路的影响

避免振荡的最重要方式是最小化电感,即栅极驱动器和栅极之间的长走线。

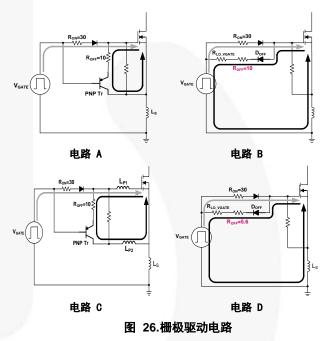

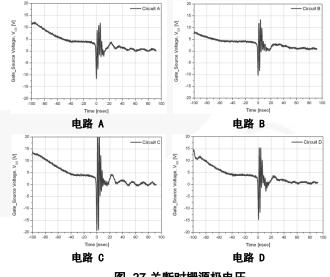

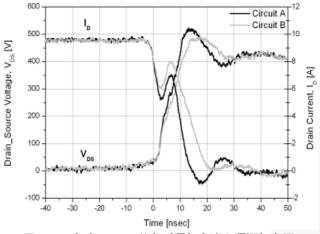

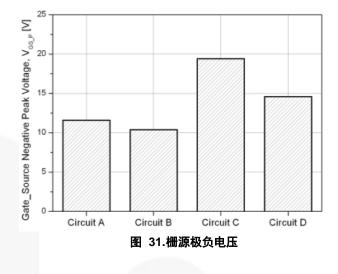

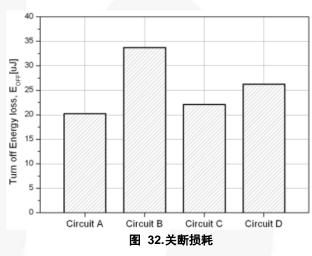

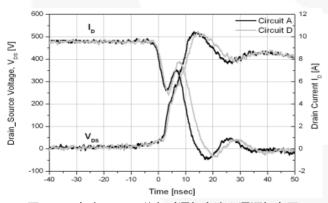

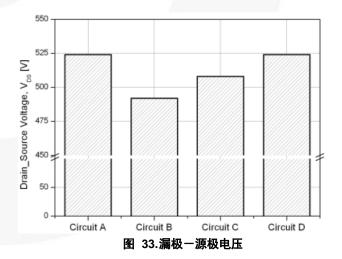

栅极驱动电路的配置对开关特性同样重要。在 图 26 中,考虑了四种栅极驱动器。一种是 PNP 晶体管关断电路(电路 A),最常用于最小化回路和快速关断。在下列图中,栅极振荡和关断损耗较低,但是漏源极击穿电压稍高。二极管关断加速电路(电路 B)的栅极振荡

比电路 A 低,但是 MOSFET 的放电电流流过栅极驱动器 IC 中图腾柱的关断电阻,因此其开关速度较慢、关断损耗较高、并且漏源极击穿电压较低。电路 D 是串联电阻(Roff=  $5.6~\Omega$ )减小了的补充电路,其总串联电阻与电路 A 相同。但电路 D 的栅极振荡和关断损耗较高。电路 C 是导通和关断路径比电路 A 长的驱动电路。它的栅极振荡较高。Lpi 和 Lpi 分别是导通和关断路径中的寄生电感。若要获得栅极振荡的最佳性能,将驱动器级接地尽可能近得直连至 MOSFET 的源极引脚非常重要。这样就可以减少关断瞬间寄生元件导致的栅极振荡。综合考虑上述结果,PNP 晶体管关断电路(电路 A)是减少栅极振荡和开关损耗的最佳配置。

图 27.关断时栅源极电压

图 28. 电路 A & B 关断时漏极电流和漏源极电压

Circuit A Circuit C 10 8 6 10 10 10 20 30 40 50 Time [nsec]

图 29. 电路 A & C 关断时漏极电流和漏源极电压

图 30. 电路 A & D 关断时漏极电流和漏源极电压

### 实际布局要求

#### 测量方法

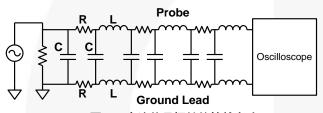

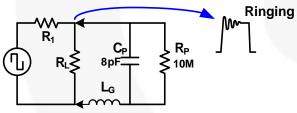

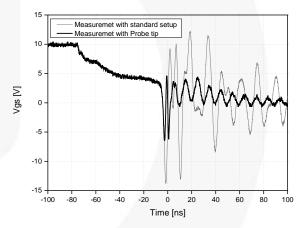

若使用示波器测量噪声,有几个注意事项。首先,重点 保证探针(即使只是简单的一段导线)为潜在的复杂电 路。对于直流信号来说,探针表现为简单的导线对,带 有一些串联电阻和一个终端电阻。而对于交流信号,在 信号频率增加时,画面变化巨大,如图 34 所示。 由于接地引线为导线,引线存在一定量的分布电感,如 图 35 所示。大约 10 cm 长的接地引线卡入电路接地 ,探针上的弹簧筒挂在测试点上。电感和探针电容相互 作用, 以 L 和 C 值确定的频率产生振荡。这种振荡不 可避免, 可视作施加到脉冲上衰减振幅的正弦波。通过 设计探针接地可以减少振荡效应,从而保证振荡频率在 探针或示波器系统的带宽限制之外。若要避免接地问题 重点是保证始终采用最短的接地引线。接地的其他替 代方法可能导致测得的脉冲上出现振荡。最好是使用示 波器的最大带宽进行测量,从而确保器件的所有波形都 能显示出来。充分利用示波器的测量性能,需要一个与 示波器设计思路相匹配的探针。

图 34.交流信号探针的等效电路

图 35.探针接地引线的影响

图 36 显示了标准示波器探针测试引线。大约 10 cm 长的接地引线卡入电路接地中,探针的弹簧筒挂在测试点上。图 38 显示不同探针设置下的栅极波形比较。存在 26 V 的峰值间栅源极电压。图 37 显示采用具有合理设置的同一示波器探针进行低栅极振荡测量。已去掉探针的探针筒和接地引线。存在 11.2 V 的峰值间栅源极电压。最好使用示波器的最大带宽进行这些测量。探针的接地引线必须直接连至开关器件的源极,而不是大容量电容的接地。

图 36.采用标准设置进行的测量

图 37.去掉探针末端和接地引线后进行的测量

图 38. 采用不同探测方法时测得的振荡比较

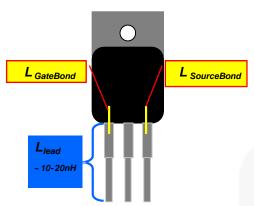

#### 封装和布局的寄生效应

若要在不同应用中驱动快速开关超级结 MOSFET, 还需要了解封装对 MOSFET 开关性能的影响。这在低压 MOSFET 文档中有详细说明。

低压封装要想获得最佳开关性能、降低传导损耗,并实现最高效率,必须采用  $R_{DS}$  和电感较低的封装。超级结 MOSFET 主要用于 500-600 V 的电压范围内。在这些额定电压下,必须考虑电气间隙距离和爬电距离。因此,最常用的封装包括业界标准的 TO-220、TO-247、TO-3P 和 TO-263。

图 39.T0-220 封装中的几种寄生效应

封装对性能的影响有限,这是因为内部栅极和源极焊接导线长度是固定的。只有引线的长度可以改变,以减少封装的源电感。典型的引线电感为 10 nH, 如图 40所示,虽然看起来不是很大,但通过这些 MOSFET di/dt = 500 A/μs 的关断电流则非常容易实现。通过电感的电压为  $V_{IND}$  = 5 V, 其关断 DI/DT 为 1000 A/μs, 感应电压为  $V_{IND}$  = 10 V。简短的计算表明完整的源电感(而不仅仅是封装的引线电感)必须降低到可接受的值。必须使用低电感检流电阻。

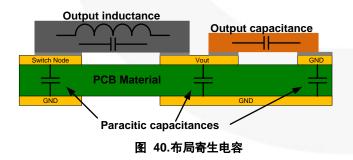

噪声的另一个来源是布局寄生效应。有两种可见的布局寄生效应: 寄生电感和寄生电容。这两种寄生效应都会影响布局的性能。如前所述,1 cm 的走线间距有 6-10 nH 的电感,可以通过在 PCB 顶部添加一层,在PCB 底部添加一个 GND 平面减少电感。另一种寄生效应是寄生电容。图 40显示布局寄生电容的原理。一条引线之间的电容紧挨在另一条引线或 PCB 另一面的GND 平面上。另一种电容为器件和 GND 平面间的电容建压。PCB 板两面上的两个并联引线能够增加电容,同时还能减少回路电感,从而减少电磁噪声辐射。

#### 振荡电路

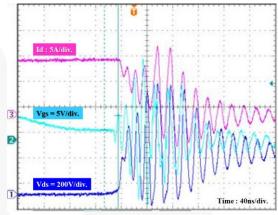

图 41 显示了关断瞬间观察到 PFC 电路中的级结 MOSFET振荡波形。在这种情况下,增加栅极电阻能够抑制漏源极峰值电压并防止超级结 MOSFET 引线电感和寄生电容产生的栅极振荡。

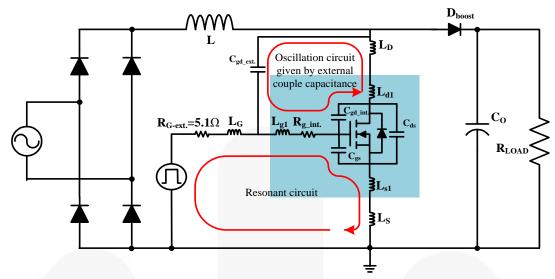

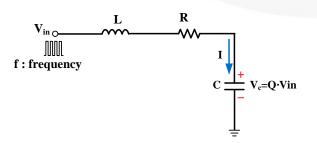

图 41. 布局寄生电容

通常来说,存在几个影响 MOSFET 开关行为的振荡电路 . 包括内外部振荡电路。图 42 显示包含功率 MOSFET 的内部寄生效应和电路板布局外部耦合电容 Cgd ext. 构 成的外部振荡电路的 PFC 简易电路图。但是, 随着开 关速度的提高,器件和电路板上的寄生元件对开关特性 的影响也随之加大。在图 42中, L、C。和 Doost分别是 电感、输出电容和升压二极管。Css、Cgd\_int和 Cds分别为功 率 MOSFET 的寄生电容。Lat, Lst 和 Lgt 分别为功率 MOSFET 的漏极、源极和栅极焊接导线和引线电感。 Rg int 和 Rg ext 为内部栅极电阻和外部栅极驱动电阻。 Cgd ext. 为寄生栅漏极电容。Locals 和 La 为印制电路板的 漏极、源极和栅极铜引线杂散电感。栅极寄生振荡出现 在 MOSFET 导通和关断时由栅漏极电容 Cad 和栅极引线 电感 L<sub>s1</sub> 组成的谐振电路中。当出现谐振条件 (ωL = 1/ωC) 时, 在栅源极间电压 Vgs中出现比驱动电压 V<sub>ss(in)</sub>大的振荡电压,图 43这是因为由谐振产生的电压 振荡与谐振电路的选择性  $Q(=\omega L/R = 1/\omega CR)$  成比例 变化,如 所示。通过电容和电感的电压 Vo和 VL可 用方程式(2)和(3)计算:

$$V_c = \frac{1}{2\pi fC} = \frac{1}{\omega CR} = Q \cdot V \tag{2}$$

$$V_{L} = 1 \cdot 2\pi f L = \frac{V \cdot \omega CL}{R} = Q \cdot V \tag{3}$$

其中,

$$Q = \frac{\omega L}{R} = \frac{1}{\omega CR}$$

图 42. 带有功率 MOSFET 内外部寄生效应的 PFC 简易电路图

在 MOSFET 开关速度提高时,MOSFET 的漏源极振荡电压通过栅漏极电容  $C_{sd}$  原因是存在负载接线电感  $L_{s}$ 。 关断时,形成包含栅极引线电感  $L_{sl}$  的谐振电路。因为栅极电阻极小,振荡电路 Q 变得很大,并且在出现谐振条件时,在该点和  $C_{sd}$  或  $L_{sl}$  之间产生很大的振荡电压,并产生寄生振荡。另外,通过  $L_{s}$  和  $L_{sl}$  的压降(可用方程式(4)表示)是由关断瞬间的漏极负电流产生的。通过杂散源电感的压降在栅源极电压中产生振荡。寄生振荡可能导致栅源极击穿电压、EMI 恶化、较大的开关损耗、栅极失控、甚至 MOSFET 失效。

$$\Delta V_{GS} = (L_S + L_{s1}) \cdot \frac{di_d(t)}{dt} \tag{4}$$

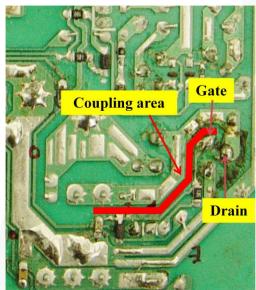

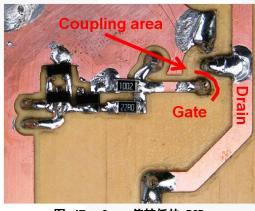

通常来说,存在几个影响 MOSFET 开关行为的振荡电路,包括内部<sup>[6][7]</sup>图 42 和外部振荡电路。显示一个功率 MOSFET 的简易电路图,包含内部寄生电容和电路板布局外部耦合电容 Copext 构成的外部振荡电路。外部耦合电容影响功率 MOSFET 关断时的 Vos 斜率。若要弄清楚外部 Cop 如何影响开关行为,在不同布局中进行比较。两种布局都是单层板设计。为了进行测量,两个升压级都运行单晶体管。

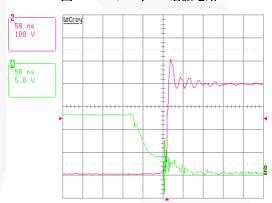

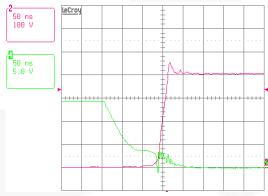

测量是在相同输入电压  $V_{IN}$ = 180 VAC和输出功率  $P_{OUT}$ 图 44= 300 W 下 PFC 升压级进行的。振荡差异如图 45 和 所示。 $V_{GS}$ (绿线)和  $V_{DS}$ (品红线)为关断期间电压。测试波形显示了特定布局中高低外部  $C_{Ed}$  的影响。

图 43. R、L 和 C 谐振电路

图 44.Cap\_ext 值较高时的关断

图 45.0 时 值较低时的关断

通过增加输出功率或在同等输出功率下降低输入电压,可以强制产生振荡效应。交流电压断电后也会出现这种情况: 当线路电压恢复供电时,升压级为大容量电容充电至标称电压。在这段时间,若 MOSFET 关断,漏极电流会非常高。漏极电流改变方向至 MOSFET 的输出电容 Coss, 为其充电至直流总线电压。电压斜率与负载电流成正比,与输出电容值成反比。Coss 的值在 VDS 低

时较高,在  $V_{\text{IS}}$  高时较低。因此,漏源极电压的 dv/dt 值在关断过程中会发生改变。较高的 dv/dt 值,由于各种寄生电容,会导致电容性位移电流。同时结合各种布局和寄生电感及电容,一个 LC 振荡电路只能通过内部  $R_{\text{S}}$  进行抑制。在某些情况下,如输入电压瞬间或短路情况下,会出现较高的 di/dt 和 dv/dt 值,这会导致不寻常的开关行为或器件损坏。然而,通过优化整个应用的布局和机械结构,快速开关超级结 MOSFET 有助于提高效率和功率密度。

### 布局要求

图 46. C<sub>aD\_EXT</sub> 值较高的 PCB

图 47. Cop\_EXT 值较低的 PCB

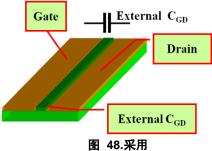

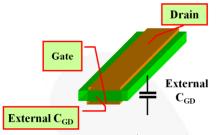

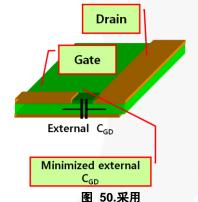

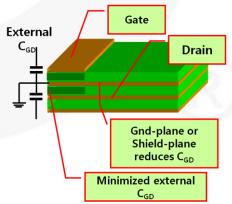

外部  $C_{sd}$  是受器件和 PCB 布局影响产生振荡的一个根因。必须尽量减少  $C_{sd}$ ,以减少栅极振荡。采用不同 PCB 布局时的测试波形如 图 46 和 图 47 所示。图 48 - 图 51 显示外部  $C_{sd}$  较高和外部  $C_{sd}$  较低时的布局。

引线之间的电容可计算如下:

$$C = \frac{\varepsilon_o \cdot \varepsilon_r \cdot A}{d} \tag{5}$$

图 48.采用 较高外部 C<sub>g</sub>d 时的单层板布局示例

图 49.采用 较高外部 C<sub>sc</sub> 时的双层板布局示例

图 50.采用 较低外部 C<sub>o</sub> 时的单层板布局示例

图 51.采用 较低外部 C<sub>o</sub> 时的双层板布局示例

比较 图 50 和 图 51,显示采用较低外部  $C_{sd}$ 时的布局解决方案。电感和电流回路对特定应用的性能有影响。电流必须运行在回路中,这些电流形成一个磁场。如果电流发生变化,磁场也随之发生变化,从而形成一个感性电压  $V_{IND}$ 。根据法拉第定律, $V_{IND}$ 的值可计算如下:

$$V_{ind} = -\frac{d\phi}{dt} = -L\frac{di}{dt}$$

with  $\phi = \int_A B \cdot dA = L \cdot I$  (6)

因此, L

同样依赖于回路的几何形状。电流回路的面积越大,电感 L 就越大。如果电流变化(di/dt)

稳定,但电流回路导致电感较高,则 V<sub>IND</sub>

升高。应尽可能地减少 di/dt

值较高的闭合电流回路。必须最大限度地减少源电感和分流电阻电感,以避免 EMI

和开关行为恶化。例如, PCB 板上 1 cm 长的引线几乎相当于 6-10 nH 感性阻抗。

### 快速超级结 MOSFET 布局指南

- 若要获得超级结 MOSFET 最佳性能,需要优化布局。

- 栅极驱动器和 R<sub>s</sub>必须尽可能地靠近 MOSFET 栅极引脚。

- 将电源 GND 和栅极驱动器 GND 分开。

- 最大限度地减少 PCB 板上的寄生电容 Cg和源极引线电感。

- 对于并联超级结 MOSFET, 必须采用对称布局。

- 通过增加 R<sub>s</sub> 或采用铁氧体磁珠减缓 dv/dt 和 di/dt。

### 结论

随着功率转换效率变得越来越重要,分立器件技术进步日新月异。开关速度极快的超级结 MOSFET 是提高效率的必要选择,但相较前代产品更难以控制。在设计快速开关 MOSFET 时,优化的栅极驱动器和电路板布局是最重要的设计参数。实用的设计技巧能够让设计人员充分利用超级结 MOSFET 的特性。

## 参考文献

- [1] T. Fujihira 和 Y. Miyasaka, "Simulated superior performances of semiconductor super junction devices" (半导体超级结器件的卓越性能模拟), ISPSD 会议记录, 页数: 423-426, 1998 年 6 月

- [2] T. Fujihira, "Theory of semiconductor super junction devices" (半导体超级结器件的理论), 日本应用物理快报, 第 36 卷, 页数: 6254-6262, 1997.

- [3] L. Lorenz、G. Deboy、A. Knapp 和 M. Maerz, "CoolMOS a new milestone in high voltage Power MOSFET" (CoolMOS 高电压功率 MOSFET 的新里程碑), 1999 年 ISPSD 会议

- [4] G. Deboy、M. Maerz、J.-P. Stengl、H. Strack、J. Tihanyi 和 H. Weber, "A new generation of high voltage MOSFET's breaks the limit line of silicon"(新一代高电压 MOSFET 打破硅限制),*电子器件会议技术 摘要*,1998 年,页数: 683-685.

- [5] S. Clementi、B. R. Pelly 和 A. Isidori, "Understanding power MOSFET switching performance"(了解功率 MOSFET 开关性能),会议记录 IAS,页数: 763-776, 1981 年

- [6] T. Fujihira、T. Yamada 和 Y Minoya, "New Oscillation Circuits Discovered in Switching-Mode Power Supplies" (开关电源中最新发现的振荡电路), 功率半导体器件和功率集成电路国际会议记录, 2008 年

- [7] Wonsuk Choi 和 Dongkook Son, "SuperFET® II a Super-Junction MOSFET that Provides Low EMI" (提供较低 EMI 的 SuperFET® II 代超级结 MOSFET), Bodo's 功率系统, 2012 年 8 月

## 作者

Won-suk Choi、Dong-kook Son 和 Markus Hallenberger HV PCIA PSS 团队/飞兆半导体

#### 负害吉旺

飞兆半导体公司保留对该产品的功能、性能或设计进行改动,且不另行通知的权力。对于本文描述的任何产品和电路在应用中所出现的问题,飞 兆半导体公司不承担任何责任,不转让其专利权下的任何许可证,也不转让其他权力。

#### 生命支持政策

若无飞兆半导体公司正式的书面授权,其产品不可作为生命支持设备或系统中的关键器件。 具体说明如下:

- 生命支持器件或系统是指如下的设备或系统:(a) 用于外科植入人体,或(b)支持或维持生命,以及(c)即使依照标示中的使用说明进行正确操作,但若操作失败,仍将对使用者造成严重的伤害。

- 关键器件是指生命支持设备或系统中,由于该器件的失效会导 致整个生命支持设备或系统的失效,或是影响其安全性及使用 效果。

ON Semiconductor and in are trademarks of Semiconductor Components Industries, LLC dba ON Semiconductor or its subsidiaries in the United States and/or other countries. ON Semiconductor owns the rights to a number of patents, trademarks, copyrights, trade secrets, and other intellectual property. A listing of ON Semiconductor's product/patent coverage may be accessed at <a href="www.onsemi.com/site/pdt/Patent-Marking.pdf">www.onsemi.com/site/pdt/Patent-Marking.pdf</a>. ON Semiconductor reserves the right to make changes without further notice to any products herein. ON Semiconductor assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. Buyer is responsible for its products and applications using ON Semiconductor products, including compliance with all laws, regulations and safety requirements or standards, regardless of any support or applications information provided by ON Semiconductor. "Typical" parameters which may be provided in ON Semiconductor data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. ON Semiconductor does not convey any license under its patent rights nor the rights of others. ON Semiconductor products are not designed, intended, or authorized for use as a critical component in life support systems or any FDA Class 3 medical devices or medical devices with a same or similar classification in a foreign jurisdiction or any devices intended for implantation in the human body. Should Buyer purchase or use ON Semiconductor products for any such unintended or unauthorized application, Buyer shall indemnify and hold ON Semiconductor and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and exp

#### **PUBLICATION ORDERING INFORMATION**

#### LITERATURE FULFILLMENT:

Literature Distribution Center for ON Semiconductor 19521 E. 32nd Pkwy, Aurora, Colorado 80011 USA Phone: 303-675-2175 or 800-344-3860 Toll Free USA/Canada Fax: 303-675-2176 or 800-344-3867 Toll Free USA/Canada Email: orderlit@onsemi.com N. American Technical Support: 800-282-9855 Toll Free USA/Canada

Europe, Middle East and Africa Technical Support:

Phone: 421 33 790 2910

Japan Customer Focus Center

Phone: 81-3-5817-1050

ON Semiconductor Website: www.onsemi.com

Order Literature: http://www.onsemi.com/orderlit

For additional information, please contact your local Sales Representative