#### Is Now Part of

# ON Semiconductor®

To learn more about ON Semiconductor, please visit our website at <a href="https://www.onsemi.com">www.onsemi.com</a>

ON Semiconductor and the ON Semiconductor logo are trademarks of Semiconductor Components Industries, LLC dba ON Semiconductor or its subsidiaries in the United States and/or other countries. ON Semiconductor owns the rights to a number of patents, trademarks, copyrights, trade secrets, and other intellectual property. A listing of ON Semiconductor's product/patent coverage may be accessed at www.onsemi.com/site/pdf/Patent-Marking.pdf. ON Semiconductor reserves the right to make changes without further notice to any products herein. ON Semiconductor makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does ON Semiconductor assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. Buyer is responsible for its products and applications using ON Semiconductor products, including compliance with all laws, regulations and safety requirements or standards, regardless of any support or applications information provided by ON Semiconductor. "Typical" parameters which may be provided in ON Semiconductor data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. ON Semiconductor does not convey any license under its patent rights nor the rights of others. ON Semiconductor products are not designed, intended, or authorized for use as a critical component in life support systems or any EDA Class 3 medical devices with a same or similar classification in a foreign jurisdiction or any devices intended for implantation in the human body. Should Buyer purchase or use ON Semiconductor products for any such unintended or unauthorized application, Buyer shall indemnify and hold ON Semiconductor and its officers, employees, emplo

# 应用笔记 AN-3008

## 晶闸管功率控制和瞬态抑制用 RC 缓冲电路

### 引言

RC 网络用于控制可能会误导通晶闸管的电压瞬态。这 类网络称为缓冲器。

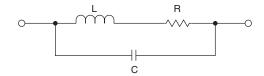

简单缓冲器由串联电阻和围绕晶闸管放置的电容组成。 这些元器件与负载电感一同形成串联 CRL 电路。缓冲 器理论的基础是电路的微分方程解。

许多 RC 组合都能提供可接受的性能。然而,若缓冲器使用不当,则会造成电路工作不稳定,并损坏半导体器件。

出于可靠性考虑,可能需同时采取导通和关断保护。有时,晶闸管必须要能在某个负载范围内工作。使用的晶闸管类型、电路配置和负载特性都有影响。

缓冲器设计时需要权衡取舍。这些权衡包括成本、额定 电压、峰值电压和导通应力。实际解决方案取决于器件 和电路的物理特性。

# 静态 dV dt

# 什么是静态 $\frac{dV}{dt}$ ?

静态  $\frac{dV}{dt}$  衡量的是晶闸管在电压瞬态下保持阻断状态的能力。

# $\left(\frac{dV}{dt}\right)_{S}$ 器件物理特性

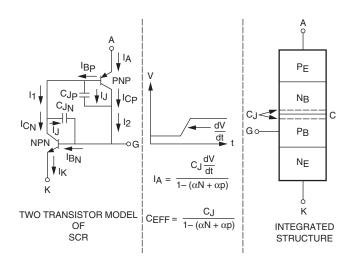

静态  $\frac{dV}{dt}$  导通是米勒效应和重新生成的结果(图 1)。结点电容两端的电压变化含有电流流过该结点的效应。该电流与电压变化率成比例  $\left(\frac{dV}{dt}\right)$ 。当其大至足以将 NPN 和 PNP 晶体管的  $\alpha$  参数之和提升到 1 个单位时,则触发器件。

图 1.  $\left(\frac{dV}{dt}\right)_S$ 模型

# 影响条件 $\left(\frac{dV}{dt}\right)_{S}$

线路交叉或晶闸管两端无初始电压时发生瞬变是最差情况。此时集电极结点电容最大,因为耗尽层在较高的电压下会变宽。

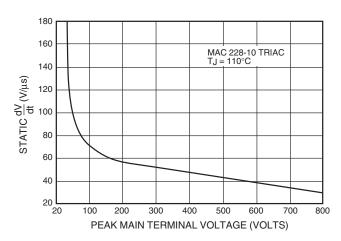

较小的瞬变无法对栅极层的固有电容充电至其正向偏置 阈值电压(图 2)。电容分压器位于集电极和栅极 - 阴 极结点之间,内置电阻从阴极 - 发射极分流,造成该效 应。

图 2. 指数  $\left(\frac{dV}{dt}\right)_S$  与峰值电压的关系

静态  $\frac{dV}{dt}$  在最大额定电压和额定温度以内工作时并不特别依赖电压。如果瞬变大致在 50V 的实际器件击穿电压以内雪崩倍增将增加漏电流,同时降低  $\frac{dV}{dt}$  能力。

额定电压较高的器件在较低电压下具有较高的保证  $\frac{dV}{dt}$ 。 这是使用指数级额定法的结果,额定值为  $50~V/\mu s$  的 400~V 器件具有较高的  $\frac{dV}{dt}$ ,为 200~V;而相同额定值的 200~V 器件其值较低。但是同样的扩散方法通常适用于 所有电压。因此,产品的实际能力差别不大。

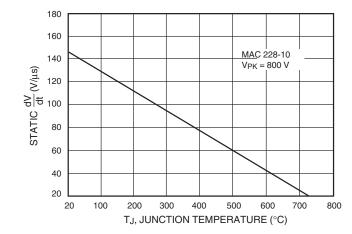

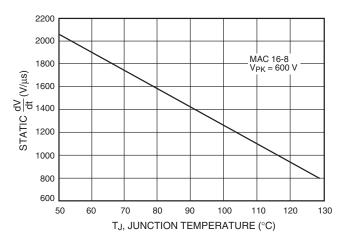

发热会增加电流增益和漏电流,降低 $\left(\frac{dV}{dt}\right)_s$ ,栅极触发电压和抗噪能力(图 3)。

图 3. 指数  $\left(\frac{dV}{dt}\right)_{S}$  与温度

# $\left(\frac{dV}{dt}\right)_S$ 故障模式

瞬变导致的偶尔一次误导通在加热器电路是可以接受的,但在防火喷淋系统或大型电机控制系统中不可以。 若后续的电流幅度或额定值过大,则导通具有破坏性。 若晶闸管短接电源线或充电电容,则它将被损坏。

静态  $\frac{dV}{dt}$  当串联阻抗能够限制浪涌时,导通不具有破坏性。晶闸管于半周期导通后关断。高  $\frac{dV}{dt}$  有助于电流在晶闸管内的流动,改善其耐受  $\frac{dI}{dt}$ 。击穿导通无此优点,应避免。

# 改善 $\left(\frac{dV}{dt}\right)_{S}$

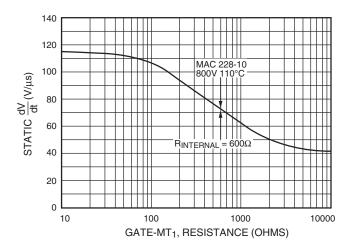

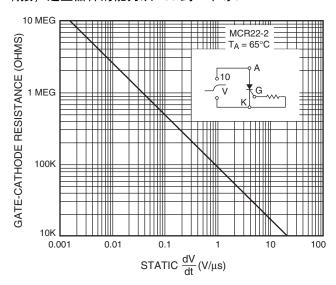

静态  $\frac{dV}{dt}$  可通过在栅极和 MT1 之间添加一个外部电阻加以改善(图 4)。电阻为漏电流提供路径,并且  $\frac{dV}{dt}$  产生的电流发源于驱动电路或晶闸管本身。

图 4. 指数(<del>dV</del>)<sub>S</sub> 与 栅极至 MT<sub>1</sub> 电阻的关系

非敏感器件 (图 5)具有分散在芯片整块阴极区域的内部短接电阻。这种设计特性改善抗噪能力和高温阻断稳定性,但代价是增加触发和保持电流。外部电阻在非敏感 SCR 和 TRIAC 中是可选器件。它们应当与器件内部的短接电阻尺寸相当( $20 \ge 100 \Omega$ ),以便最大程度改善性能。晶闸管的内部电阻应采用欧姆表,不会对二极管结点产生正向偏置。

图 5. 指数 $\left(\frac{dV}{dt}\right)_{S}$ 与结温

敏感的栅极 TRIACS 具有 100 至 1000 Ω电阻。采用外部电阻,其 $\frac{dV}{dt}$  能力依然较非敏感器件为差,因为栅极层的横向电阻降低了它的优势。

敏感型栅极 SCR ( $I_{GT}$  < 200  $\mu$ A) 无内置电阻。它们必须使用外部电阻。电阻推荐值为 1000  $\Omega$ 。更高的电阻值会降低最大工作温度。 $\left(\frac{dV}{dt}\right)_s$  (图 6)。根据栅极 - 阴极端接,这些器件的能力从 100 到 1 不等。

图 6. 指数 $\left(\frac{dV}{dt}\right)_S$ 与 栅极 - 阴极电阻的关系

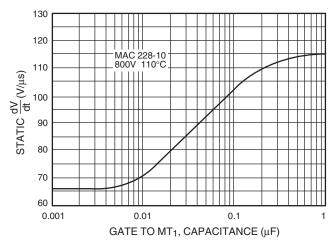

图 7. 指数 $\left(\frac{dV}{dt}\right)_S$ 与 栅极至 MT<sub>1</sub> 电容的关系

栅极 - 阴极电容(图 7)为瞬变电流提供分流路径,方式与电阻相同。它还会过滤来自驱动电路的噪声电流,并增强内置栅极 - 阴极电容分压器的效果。栅极驱动电路应能在无过多延迟的情况下对电容充电,但无需像对电阻一样提供持续电流,以将  $\frac{dV}{dt}$  提高相同的量。然而,电容无法增强静态热稳定性。

最大 $\left(\frac{dV}{dt}\right)_s$  在短接时得以改善。

由于晶闸管内存在扩散电阻,真正的改善便止步于此。 使用数值约为  $0.1~\mu F$  的外部电容可获得更高  $R_{GK}$  值的最大性能增强。

应当保持晶闸管冷却,以获得最高的 $\left(\frac{dV}{dt}\right)_s$ 。另外,器件应当在应用电路中,以尽可能高的温度使用具有最低测量触发电流的晶闸管进行测试。

# TRIAC 换向 $\frac{dV}{dt}$

# 什么是换向 $\frac{dV}{dt}$ ?

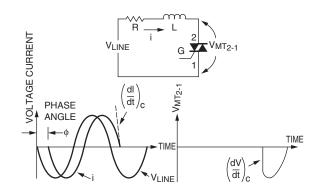

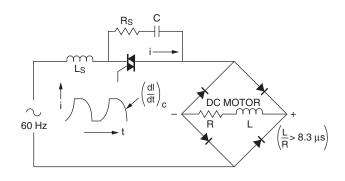

图 8. TRIAC 感性负载关断  $\left(\frac{dV}{dt}\right)_{c}$

# $\left(\frac{dV}{dt}\right)_{c}$ 器件物理特性

一个 TRIAC 工作特性与两个反向并联连接的 SCR 类似。因此,任意极性的瞬变均可导通该器件。

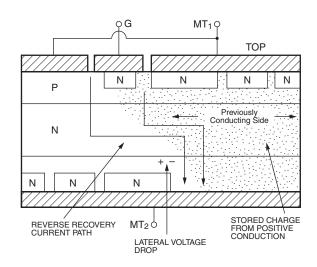

由于先前导通,晶振体内存在电荷 (图 9)。集电极结 点耗尽层边界处的电荷会影响 $\left(\frac{dV}{dt}\right)_s$  。 TRIACS 具有更低的 $\left(\frac{dV}{dt}\right)_s$  ,相比 $\left(\frac{dV}{dt}\right)_s$  而言,因为存在该额外电荷。

图 9. TRIAC 结构和 换向电流的流向

TRIAC 内存储的电荷量取决于关断前的峰值电流及其零交叉速率。 $\left(\frac{dI}{dt}\right)_c$  在经典电路中,负载阻抗和线路频率即可确定 $\left(\frac{dI}{dt}\right)_c$  正弦波电流的零交叉速率由 50% 和 0% 电平之间的割线斜率给出:

$$\left(\frac{dI}{dt}\right)_{0} = \frac{6fI_{TM}}{1000}A/ms$$

其中,f = 线路频率, $I_{TM} = TRIAC$  中的最大通态电流。

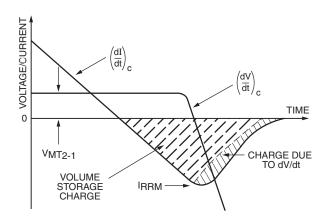

关断同时取决于米勒效应位移电流(由  $\frac{dV}{dt}$  在集电极电容两端产生)和器件内部存储的体电荷所产生的电流(图 10)。如果来自这两部分的反向恢复电流都很大,则 TRIAC 基层中的横向 IR 压降将正向偏置发射极,并导通 TRIAC。顺着电流传导的正方向关断时,因为受器件几何形状的影响,换向  $\frac{dV}{dt}$  的能力较差。栅极位于芯片顶部,阻碍电流流动。

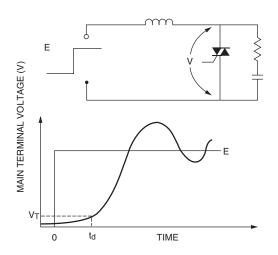

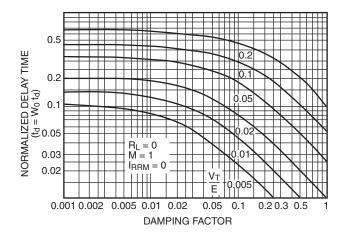

随着电流波形趋于零,在整个导通期间沿电流波形背面进行重组。关断能力取决于其形状。如果电流幅度较小且零交叉 $\left(\frac{dI}{dt}\right)_c$ 较低,则体电荷存储量较少,并且关断开始受限于 $\left(\frac{dV}{dt}\right)_s$ 中等电流幅度时,体电荷开始影响关断特性,此时应使用较大的缓冲器。当电流较大,或者具有快速零交叉时,对 $\left(\frac{dV}{dt}\right)_c$ 的影响很小。顺着电流传导的正方向关断时,因为受器件几何形状的影响,换向 $\frac{dI}{dt}$ 和电压重加延迟时间决定关断是否成功。(图 11、12)

图 10. 换向时的 TRIAC 电流和电压

图 11. 缓冲器延迟时间

图 12. 达到标准化电压的延迟时间

# 影响条件: $\left(\frac{dV}{dt}\right)_{C}$

顺着电流传导的正方向关断时,因为受器件几何形状的影响,换向 $\frac{dV}{dt}$  取决于电荷存储量和动态恢复时间,另外变量也会影响静态 $\frac{dV}{dt}$  高温增加少数载流子的存活时间以及恢复电流的大小,使关断更为困难。减慢电流零交叉速率的负载有助于关断。带有谐波的内容会阻碍关断。

图 13. 桥式电路中控制电机的相位

#### 电路示例

图 13 表示在桥式电路中使用 TRIAC 控制感性负载。感性负载的时间常数大于线路周期。这会使负载电流保持恒定,且 TRIAC 电流随线路电压的反向而快速开关。该应用由于会造成 TRIAC 关断困难而不受欢迎,因为存在较高的 $\left(\frac{dI}{dI}\right)$ 。

高电流导致高结温,电流零交叉速率也较高。电机在启动时的电流幅度可达正常工作电流的 5 到 6 倍。这同时增加了结温和电流零交叉速率,导致难以关断。

在 400 Hz 应用中,线路频率会造成电流零交叉速率过高。谐振变压器电路具有双倍周期,并且初级与次级谐振端都存在电流谐波。非正弦波电流会导致关断困难,即使零交叉之前电流幅度较低。

# $\left(\frac{\mathsf{dV}}{\mathsf{dt}}\right)_{\mathsf{C}}$ 故障模式

$\left(rac{d\,V}{dt}

ight)_c$  故障导致失去相位控制。可能发生暂时性导通故障,或出现完全关断故障。如果 TRIAC 非对称导通,则该故障将是破坏性的,因为会导致直流成分以及磁饱和。线圈电阻可限制该电流。故障是因为浪涌电流和结温过高。

# 改善 $\left(\frac{dV}{dt}\right)_{c}$

改善 $\left(\frac{dV}{dt}\right)_s$  的步骤同样有助于改善 $\left(\frac{dV}{dt}\right)_s$  ,存储电荷主导关断时除外。因此,有必要采取措施,减少存储电荷或软化换向电流。

给定负载的情况下,相比较小的 TRIACS,更大的 TRIACS 具有更佳的关断能力。较大 TRIACS 的电流密度较低,允许重加电荷在内部电荷中占有更大的比例。此外,结温也更低。

具有高栅极触发电流的 TRIACS 其关断能力较强,因为栅极层的扩散电阻较低,从而降低米勒效应或者缩短载流子的存活时间。

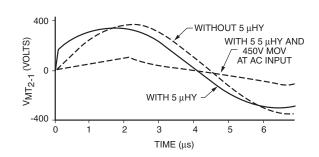

通过增加一个换向软化电感,使其与负载串联,即可调节电流零交叉速率。高磁导率 "方形环路" 小电感饱和使负载电流不存在严重干扰。电流过零后电感即复位,导致此时缓冲器电路产生大电感。这会减慢电流零交叉速率,延迟阻断电压的重加,有助于关断。

换向电感是电路的一部分,能使电路产生延时而非电感。它对器件所观察到的  $\frac{dV}{dt}$  几乎不产生影响。以下示例表明添加一个电感后得到的改善结果;电感由采用绕带磁芯的 33 匝 18 号导线绕组构成 (52000 -1A)。该磁芯极小,其外径为 3/4 英寸而厚度为 1/8 英寸。延迟时间可由下式计算得出:

$$t_s = \frac{(N A B 10^{-8})}{E}$$

where:

t<sub>s</sub> = 达到饱和的时间延迟,单位为秒。

B=饱和通量密度,单位为高斯。

A = 磁芯有效横截面积,单位为平方厘米。

N=绕组匝数。

对于上述电感,有:

$t_s = (33 \oplus )(0.076 \text{ 平方厘米})(28000 高斯)(1 \text{ x } 10^{-8})/(175 \text{ v}) = 4.0 \,\mu\text{s}$ 。

电感饱和电流无需比 TRIAC 触发电流高出很多。在恢复电流高于该值以前,就会发生关断故障。这一条件使电感可通过下式进行调节:

H<sub>S</sub> = MMF 至饱和 = 0.5 奥斯特

$$I_S = \frac{H_S M_L}{0.4 \pi N}$$

where:

ML = 有效磁路长度 = 4.99 cm。

$$I_S = \frac{(.5) (4.99)}{0.4 \pi 33} = 60 \text{ mA}.$$

### 缓冲器物理特性

#### 无阻尼自然谐振

$$\omega_0 = \frac{I}{\sqrt{LC}}$$

Radians/second

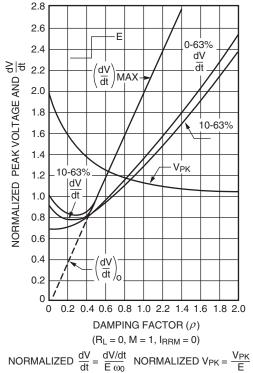

谐振决定  $\frac{dV}{dt}$  ,并且如果缓冲器电阻较小则会提升峰值电容电压。 C 和 L 通过  $\omega_0^2$  相互关联。  $\frac{dV}{dt}$  跟随  $\omega_0$  线性变化(阻尼系数不变)。若要让  $\frac{dV}{dt}$  以 10:1 的比例下降,需让其中一个参数以 100:1 的比例增加。

#### 阻尼系数

$$\rho = \frac{R}{2} \sqrt{\frac{C}{L}}$$

阻尼系数与电路损耗和浪涌阻抗之比成比例关系。它确定  $\frac{dV}{dt}$  和峰值电压之间的取舍。建议的阻尼系数范围为 0.01 至 1.0 。

#### 缓冲器电阻

# 阻尼与 dV dt

当  $\rho < 0.5$  时,缓冲器电阻较小,且  $\frac{dV}{dt}$  主要取决于谐振。阻尼系数小于 0.3 时, $\frac{dV}{dt}$  几乎没有改善,但峰值电压和缓冲器放电电流增加。电压波形为  $1\text{-}COS(\theta)$ ,并伴有过冲和振铃。最大值  $\frac{dV}{dt}$  出现在 t=0 以后。电压上升前存在时间延迟,峰值电压几乎翻倍。

当  $\rho > 0.5$  时,电压波形几乎呈指数变化。最大瞬时  $\frac{dV}{dt}$  出现在 t = 0 时刻。几乎没有时间延迟,并存在中等程度的电压过冲。

当  $\rho > 1.0$  时,缓冲器电阻较大,且  $\frac{dV}{dt}$  主要取决于其数值。电路存在一定程度的过冲,哪怕此时处于过阻尼状态。

高负载电感要求大缓冲器电阻和小缓冲器电容。低电感 要求小电阻和大电容。

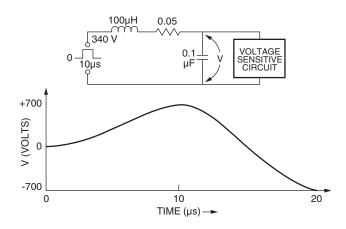

#### 阻尼与瞬变电压

图 14 显示串联电感和滤波器电容连接在交流市电线路 两端。瞬变干扰中的峰峰值电压上升幅度几乎达到了 4 倍。另外由于振铃,导致干扰持续时间延长,增加了电 压敏感型电路出现故障或损坏的风险。关断开关会造成 这一现象。添加一个阻尼电阻使其与电容串联,可缓解 该问题。

图 14. 无阻尼 LC 滤波器 放大并延长瞬变

#### dl dt

#### 非感性电阻

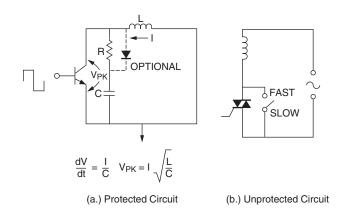

缓冲器电阻可限制电容的放电电流,并减少 $\frac{dI}{dt}$  应力。高 $\frac{dI}{dt}$  会损坏晶闸管,哪怕脉冲持续时间非常短。电流上升速率直接与电路电压成正比,与串联电感成反比。缓冲器通常是损坏晶闸管的主要原因,因为它具有低电感,且位置靠近晶闸管。

若没有瞬态抑制器,电容两端的最大电压值就是晶闸管的击穿电压。它可能超过多个器件的最高额定电压值, 因为高压器件经常用于为低电压规格供电。

缓冲器电阻最小值取决于晶闸管类型、触发象限、栅极电流幅度、电压、重复或非重复操作和所需预期寿命。电流上升速率无法简单预测,因为它取决于晶闸管的导通速度、电路布局、缓冲器电容的类型和大小,以及缓冲器电阻中的电感值。附录 D 中的等式描述了该电路。然而,模型所需的数值除通过测试外,无法轻易获取。因此,应在实际应用电路中验证可靠性。

表 1 显示建议的最小电阻值;这些数值通过测试四种不同 TRIAC 芯片尺寸的 20 个样片来估算 (附录 A)。

表 1. 四象限触发的最小非感性缓冲器电阻。

| TRIAC 类型                                              | 峰值 V <sub>C</sub><br>电压 | R <sub>S</sub> (Ω) | <u>dl</u><br>dt<br>Α/μS |

|-------------------------------------------------------|-------------------------|--------------------|-------------------------|

| 非敏感栅极                                                 | 200                     | 3.3                | 170                     |

|                                                       | 300                     | 6.8                | 250                     |

| (I <sub>GT</sub> > 10mA)<br>8 至 40 A <sub>(RMS)</sub> | 400                     | 11                 | 308                     |

| (rime)                                                | 600                     | 39                 | 400                     |

|                                                       | 800                     | 51                 | 400                     |

## 降低 dl

$TRIAC_{dl}^{dI}$  可通过避免四象限触发而加以改善。大部分光电耦合器电路在第一和第三象限操作 TRIAC。集成电路驱动器则使用象限二和象限三。零交叉触发器件很有用,因为它们可在电压过高时禁止触发。

以高幅度快速上升的脉冲驱动栅极可提高  $\frac{dI}{dt}$  能力。栅极额定值部分定义允许的最大电流。

$10~\Omega$  、  $0.33~\mu F$  缓冲器充电至 650~V,可获得  $1000~A/\mu s~\frac{dI}{dt}$  以 20~W 绕线单元替换非感性缓冲器电阻可将上升速率降低至不具有破坏性的  $170~A/\mu s~(800~V)$ 。使用非感性电阻,电感在 800~V 时具有  $80~A/\mu s~$ 的上升速率。

#### 缓冲器电容

0.3 的阻尼系数可最大程度降低缓冲器电容值 (给定的  $rac{dV}{dt}$ 。它可降低成本和电容的物理尺寸。然而,它会升高电压,增加平衡成本。

缓冲器操作依赖于缓冲器电容的充电。关断缓冲器要求最小导通角度足够长,以便对电容放电。它至少应是 $(R_S\ C_S)$ 常数的数倍。

#### 存储电能

#### 感性开关瞬变

$$E = \frac{1}{2} L I_O^2$$

Watt-seconds or Joules

$I_0 =$ 流过电感并以安培表示的电流 (t = 0)。

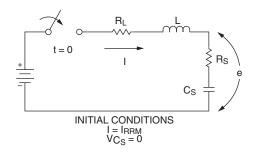

关断时,谐振充电无法对电源增压至 2 倍以上。如果关断时负载电感内有初始电流流过,则有可能可以获得高得多的电压。TRIAC 关断时可忽略电能存储,因为它具有低维持或恢复电流。

额外的开关 (如继电器、恒温器或断路器)允许在开关 打开时打断负载电流并产生高尖峰电压。电感内的电能 转换为电路电容,并确定峰值电压 (图 15)。

图 15. 中断感性负载电流

#### 电容放电

存储在缓冲器电容中的电能  $\left(E_C = \frac{1}{2}CV^2\right)$  在每次导通时传送至缓冲器电阻和晶闸管。功耗与频率成正比  $\left(P_{AV} = 120 \; E_C \; @ \; 60 \; H_Z\right)$ 。

#### 电流引导

负载电感内流过的电流无法即刻改变。该电流导入缓冲器电阻,理论上导致无穷大的  $\frac{dV}{dt}$  尖峰,幅度等于  $(I_{RRM}R)$  或  $(I_{H}R)$ 。

#### 负载相位角度

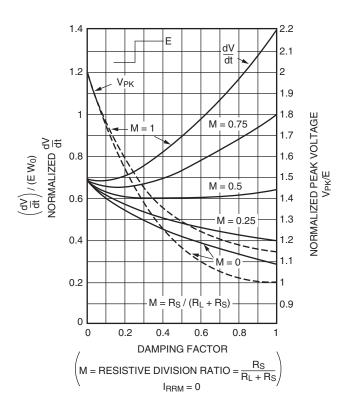

高度感性负载导致关断时电压和 $\left(\frac{dV}{dt}\right)_c$  上升。然而,它们有助于保护晶闸管免受瞬变影响,以及 $\left(\frac{dV}{dt}\right)_s$  若器件确实导通,则负载可用作缓冲器电感,限制涌入电流的速率。负载电阻降低  $\frac{dV}{dt}$  和  $V_{PK}$  (图 16)。

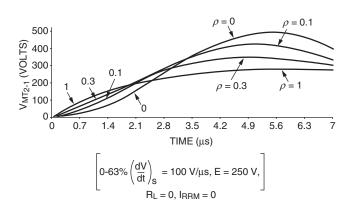

图 16. 0 至 63% dV

## 电压波形特性

阻尼系数和反相恢复电流确定电压波形。缓冲器阻尼系数低于 0.5 或存在极高恢复电流时,波形不呈指数变化(图 17)。

图 17. 不同阻尼系数下的电压波形

图 18. 权衡取舍: V<sub>PK</sub> 与<mark>dV</mark>

各种波形参数(图 18)可描述  $\frac{dV}{dt}$  某些参数容易求解,而且有助理解。这些参数包括:初始  $\frac{dV}{dt}$  、最大瞬时  $\frac{dV}{dt}$  以及到达峰值重加电压的平均  $\frac{dV}{dt}$  。  $0 \cong 63\% \left(\frac{dV}{dt}\right)_s$  以及  $10 \cong 63\% \left(\frac{dV}{dt}\right)_c$  的定义参见器件数据手册,它们很容易测得,但难以计算。

## 非理想特性

#### 磁芯损耗

在缓冲器的自然频率下,典型 60~Hz 负载的磁芯材料会产生损耗。它们表现为负载电感和绕组直流电阻的串联电阻(图 19)。这使得实际的  $\frac{dV}{dt}$  低于理论值。

- L DEPENDS ON CURRENT AMPLITUDE, CORE SATURATION

- R INCLUDES CORE LOSS, WINDING R. INCREASES WITH FREQUENCY

- C WINDING CAPACITANCE. DEPENDS ON INSULATION, WIRE SIZE, GEOMETRY

#### 图 19. 电感模型

#### 复杂负载

现实中,很多电感都是非线性的。它们的磁芯材料不是 有隙的,这导致电感随电流幅度而改变。很难通过小信 号测量对它们进行特性化。出于建模的需要,最好的方 法是在实际应用中对它们进行测量。

应检查复杂负载电路在导通和关断时的瞬变电压和电流。使用容性负载,在峰值输入电压下导通时会产生最大浪涌电流。电机起始电流比稳态值要高 4 至 6 倍。发生器可将电压提升至线路值之上。白炽灯的冷启动电流比稳态值高 10 至 20 倍。变压器通电时产生电压尖峰。功率因数校正电路和开关器件会产生复杂的负载。大部分情况下,简单 CRL 模型允许对缓冲器进行近似设计。然而,测试与测量最差情况的负载条件却是无可取代的。

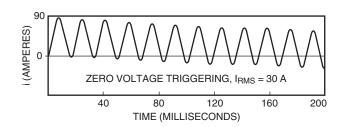

#### 感性电路中的浪涌电流

启动时,具有较长 L/R 时间常数的感性负载会产生非对称多周期浪涌 (图 20)。电压过零点触发是最差情况。可利用电流过零点触发抑制浪涌。

图 20. 感性电路的启动浪涌

磁芯的剩余磁通量和饱和会引起浪涌电流。浪涌电流大小取决于触发角度、线路阻抗、磁芯特性和残余磁化方向。例如, 2.8 kVA 120 V 1:1 变压器在 1.0 A 负载下会产生 160 A 的启动电流。以较小的导通角度软启动电路可减少浪涌电流。

变压器磁芯一般都不是有隙的,因此很容易饱和。导通 角度的微小非对称性就会导致磁饱和以及多周期电流浪 涌。

获得可靠操作的步骤包括:

- 1. 提供足够的触发电流幅度。 TRIAC 的触发电流各不相同,具体取决于它们的工作象限。临界栅极电流或光电耦合器 LED 电流导致半波工作。

- 提供足够的栅极电流持续时间,以便达到闩锁要求。感性负载减慢主端电流的上升速度。栅极电流必须保持在 I<sub>GT</sub> 额定值以上,直到主端电流超过闩锁值。负载和缓冲器附近的两个泄放电阻可放电,有助于闩锁。

- 3. 使用缓冲器防止  $TRIAC\left(\frac{dV}{dt}\right)_c$  故障。

- 4. 尽量减少设计导入的触发器非对称性。每半个周期都必须正确触发,包括第一个周期。使用存储示波器查看导通中前几个周期的电路特性。或者,对负载通电前启动栅极电路。

- 5. 从线路 (而非 TRIAC 主端电压)获取触发器同步信号。这可避免磁芯滞后和触发角度之间的再生交互,防止触发失控、半波操作和磁芯饱和。

- 6. 启动时避免高浪涌电流。使用电流探针确定浪涌幅度。使用软启动电路降低浪涌电流。

#### 分布式绕组电容

线圈的圈与层之间存在小电容。这些小电容汇总后,可 视为单个分流电容。在频率高于它自谐振频率时,负载 电感变现的像电容。当发生快速瞬变时 (比如开关关断 时产生的瞬变),控制  $\frac{dV}{dt}$  和  $V_{PK}$  就会变得低效率。通 过在线路上增加一个小型缓冲器即可解决该问题。

#### 自电容

晶闸管具有自电容,当负载电感较大时会限制 $\frac{dV}{dt}$ 。大负载电感、高功率因数和低电压可允许无缓冲器工作。

### 缓冲器示例

#### 无电感

#### 功率 TRIAC 示例

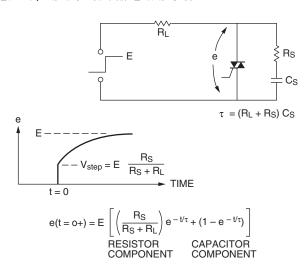

图 21 显示瞬变电压施加于 TRIAC,控制阻性负载。理论上,TRIAC 两端将会立即产生一个阶跃电压。减慢该速率的两个因素是绕组的电感和晶闸管的自电容。由于缓冲器电阻中存在 IR 压降,因此加入了一个指数电容充电元器件以及衰减元器件。当负载电阻远高于缓冲器电阻时,非感性缓冲器电路非常有用。

图 21. 非感性缓冲器电路

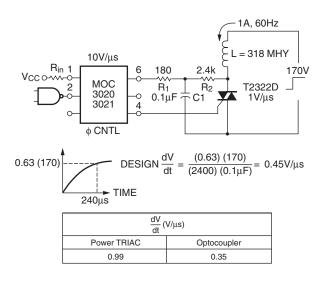

## 光电 TRIAC 示例

#### 单缓冲器, 时间不变设计

图 22 表示采用 RC 时间常数的设计方法。对于光电耦合器而言,仅存在通过缓冲器电容的电压。电阻  $R_1$  提供功率 TRIAC 的触发电流。针对最差情况的设计假定功率 TRIAC 的电压瞬时改变。电容电压在一个时间常数的时间内上升至最大值的 63%。因此有:

$$R_1 C_S = \tau = \frac{0.63 \ E}{\left(\frac{dV}{dt}\right)_s} \text{ where } \left(\frac{dV}{dt}\right)_s \text{ is the rated static } \frac{dV}{dt}$$

对于光电耦合器而言。

图 22. 用于敏感型栅极 TRIAC 和相位可控型光电耦合器的单 缓冲器 (p = 0.67)

光电耦合器导通电流的时间仅够触发功率器件。导通时,MT2 和栅极之间的电压会下降至光电 TRIAC 正向阈值电压以下,导致关断。当功率 TRIAC 在稍后的零电流交叉导通周期中关断时,对于光电耦合器而言,只存在 $\left(\frac{dV}{dt}\right)$ 。因此,无需针对更低的光电耦合器 $\left(\frac{dV}{dt}\right)$ 。每定值进行设计。本例中,针对光电耦合器设计的单个缓冲器即可同时保护两个器件。

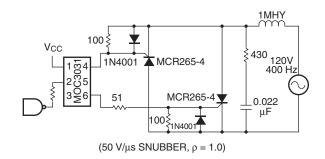

图 23. 反并联 SCR 驱动器

#### 带 SCR 的光电耦合器

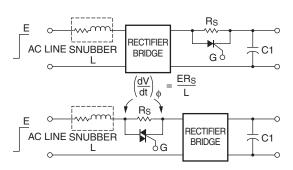

反并联 SCR 电路在光电耦合器和 SCR 上分别具有相同的  $\frac{dV}{dt}$  (图 23)。相位可控型光电耦合器要求 SCR 缓冲至较低的  $\frac{dV}{dt}$  额定值进行设计。反并联 SCR 电路无电荷存储特性——该特性会降低 TRIAC 的关断能力。所有 SCR 都导通半周期,下半个周期用于交流线路恢复。传导 SCR 的关断  $\frac{dV}{dt}$  对其他器件而言变为静态正向阻断  $\frac{dV}{dt}$  。在缓冲器设计中使用 SCR 数据手册中的  $\left(\frac{dV}{dt}\right)_s$  额定值。

整流电桥内的 SCR 用于控制交流负载;该 SCR 将无用于恢复的半周期。可用时间随线路电压的上升而减少。这使得该电路不那么好用了。可利用输入至电桥或横跨 SCR 的缓冲器抑制感性瞬变。但是,时间限制依然适用。

# 光电 $\left(\frac{dV}{dt}\right)_{C}$

电流低于 100 mA 时,可使用过零光电耦合器来开关感性负载 (图 24)。然而,若要获得更高的负载电流,可将功率 TRIAC 搭配光电耦合器使用。

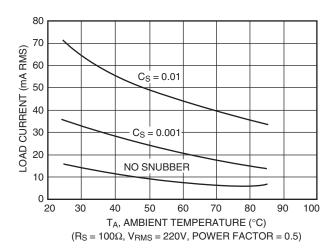

#### 图 24. MOC3062 感性负载电流与 TA 的关系

配合功率器件时,建议使用相位可控型光电耦合器。当负载电流较小时,适合使用 MAC97 TRIAC。

异常电路条件有时会导致光电耦合器在 $\left(\frac{dV}{dt}\right)_{c}$ 模式中的误操作。功率器件中极高的电流导致 MT2 和栅极之间的电压上升,并使栅极保持光电耦合器导通状态。使用较大的 TRIAC 或采取其他手段限制浪涌电流即可解决这一问题。

极短的导通时间使光电耦合器中存在残留电荷。微小的 导通角度允许在电压重加前进行恢复。

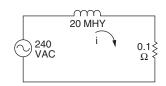

#### 带电感的缓冲器

考虑一个使用大电容的过阻尼缓冲器,其电容电压在考察期间变化不大,则电路简化为等效 L/R 串联充电电路。

流过缓冲器电阻的电流为:

$$i = \frac{V}{R_{\tau}} \left( 1 - e^{-\frac{t}{\tau}} \right),$$

并且, TRAIC 两端的电压为:

$e = i R_S$

在 t=0 时, TRIAC 两端的电压波形随最大额定值呈指数上升。经推导,可得:

$$\left(\frac{dV}{dt}\right)_0 = \frac{VR_S}{L}$$

高度过阻尼缓冲器电路是不实用的设计。该例说明几个 问题:

- 初始电压看似完全施加在电路电感上。因此,它决定了流过缓冲器电阻的电流变化速率,以及初始 dV dt。当负载中存在电阻时,该结果不变,并对所有阻尼系数都为真。

- 2. 缓冲器能够起到作用,因为电感控制通过电阻的电流变化速率和电容充电速率。缓冲器设计无法绕过电感。这种方法暗示,缓冲器电容无关紧要,但仅在这种假设性条件下适用。不存在电容时,缓冲器电阻分流晶闸管,造成无法接受的漏电流。若功率损耗是可以接受的,则 dV 可以不通过电容直接控制。一个示例是软启动电路,用于限制开关电源中的浪涌电流(图 25)。

Snubber with no C

图 25. 开关电源中的 浪涌电流限制

# TRIAC 设计步骤 $\left(\frac{dV}{dt}\right)_{c}$

1. 参考图 18 选择特定的阻尼系数 (ρ),实现这两个参数的权衡取舍: $V_{PK}$  和  $\frac{dV}{dt}$  。确定与所选阻尼系数相应的标准化  $\frac{dV}{dt}$  。

电压 E 取决于负载相位角度:

$$E = \sqrt{2} V_{RMS} Sin (\phi) where \phi = tan^{-1} \left(\frac{X_L}{R_L}\right) where$$

$\phi$  = 线路 V 和负载 I 之间测得的相位角度  $R_L$  = 测得的负载直流电阻。

然后

$$Z = \frac{V_{RMS}}{I_{RMS}} \sqrt{R_L^2 + X_L^2} X_L = \sqrt{Z^2 - R_L^2}$$

and

$$L = \frac{X_L}{2 \pi f_{Line}}$$

若仅已知负载电流,则假设纯电感。这便给出了一个保守设计。因此有:

$$L = \frac{V_{RMS}}{2 \pi f_{LINE} I_{RMS}} \text{ where } E = \sqrt{2} V_{RMS}$$

例如:

$$E = \sqrt{2} 120 = 170 \text{ V}; L = \frac{120}{(8 \text{ A})(377 \text{ rps})} = 39.8 \text{ mH}$$

查看图中  $\rho = 0.6$ ,  $V_{PK} = (1.25) 170 = 213V$  的位置。

选择 400V TRIAC。读  $\frac{dV}{dt}_{(\rho = 0.6)} = 1.0$

2. 施加谐振条件:

$$\omega_0 = \frac{5 \times 10^6 \text{ V/S}}{(1)(170 \text{ V})} = 29.4 \times 10^3 \text{rps}$$

$$\omega_0 = \left(\text{spec} \frac{\text{dV}}{\text{dt}}\right) / \left(\frac{\text{dV}}{\text{dt}}\right) = E$$

$$C = \frac{1}{\omega_0^2 L} = 0.029 \,\mu\text{F}$$

3. 施加阻尼条件:

$$R_S = 2\rho \sqrt{\frac{L}{C}} = 2(0.6) \sqrt{\frac{39.8 \times 10^{-3}}{0.029 \times 10^{-6}}} = 1400 \text{ ohms}$$

# $\left(\frac{dV}{dt}\right)_{c}$ 安全区域曲线

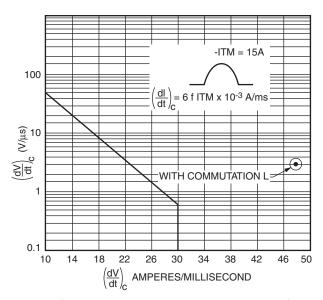

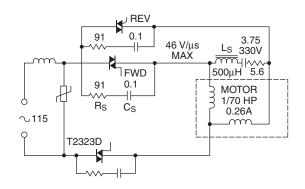

图 26 显示 MAC16 TRIAC 的关断安全工作区域曲线。在该曲线下方进行关断则不会有任何问题。该区域以静态  $\frac{dV}{dt}$  在低数值  $\left(\frac{dI}{dt}\right)_c$  以及高电流时的延迟时间为边界。减少峰值电流可允许电路工作在更高的线路频率下。该TRIAC 工作在 f=400 Hz、 $T_J=125$  °C 和  $I_{TM}=6.0$  A下,使用 30  $\Omega$ 和 0.068  $\mu$ F 缓冲器。低阻尼系数可扩展器件的工作范围至更高的  $\left(\frac{dI}{dt}\right)_c$ ,但电容大小会增加。加入小数值可饱和换向电感将引入恢复延迟时间,扩展允许的额定电流值。

$\left( \begin{array}{c} \text{MAC 16-8, COMMUTATIONAL L} = 33 \text{ TURNS #18,} \\ \text{52000-1A TAPE WOUND CORE 3/4 INCH OD} \end{array} \right)$

图 26.

$$\left(\frac{dV}{dt}\right)_C$$

与  $\left(\frac{dI}{dt}\right)_C$  T<sub>J</sub> = 125 °C

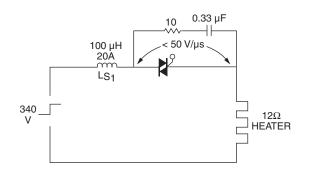

# 静态 dV 设计

通常在交流市电和电源绕组中存在一定量的电感。如果电路中有变压器的话,则电感可能大于  $100~\mu H$ ; 如果存在分流功率因数校正电容的话则电感接近零。一般线路电感约为数  $\mu H$ 。最小电感值必须是已知的,或通过增加一个串联电感加以定义,以确保可靠性(图 27)。

开始设计时建议使用  $100~\mu H$ 。将假定的电感值代入等式中的 C。更大的电感值会使缓冲器电阻更高,并降低  $\frac{dI}{dt}$ 。例如:

图 27. 缓冲阻性负载

Given E =

$$240 \sqrt{2} = 340 \text{ V}$$

Pick  $\rho = 0.3$

然后根据图 18,  $V_{PK} = 1.42(340) = 483 V$ 。

因此,有必要使用 600~V 器件。使用前文中的等式计算  $\omega_0$ 、 C 和 R ,可得:

$$\omega_0 = \frac{50 \times 10^6 \text{ V/S}}{(0.73)(340 \text{ V})} = 201450 \text{ rps}$$

$$C = \frac{1}{(201450)^2 (100 \times 10^{-6})} = 0.2464 \mu\text{F}$$

$$R = 2(0.3) \sqrt{\frac{100 \times 10^{-6}}{0.2464 \times 10^{-6}}} = 12 \text{ohms}$$

## 可变负载

缓冲器应当设计为具有最小的负载电感,因为  $\frac{dV}{dt}$  将由于对  $\omega_0$  的依赖关系而达到最高值。这就需要使用电压更高的器件在最大电感情况下工作,因为相应的阻尼系数较低。

图 28 描述了各种功率因数下用于 8.0 A 负载的  $\frac{dV}{dt}$  。最 小电感是为了防止阻性负载  $\frac{dV}{dt}$  静态点火而增加的元器件。

| ρ    | R    | L    | V <sub>step</sub> | V <sub>PK</sub> | dV<br>dt             |

|------|------|------|-------------------|-----------------|----------------------|

|      | Ω    | MHY  | V                 | V               | <b>V/</b> μ <b>s</b> |

| 0.75 | 15   | 0.1  | 170               | 191             | 86                   |

| 0.03 | 0    | 39.8 | 170               | 325             | 4.0                  |

| 0.04 | 10.6 | 28.1 | 120               | 225             | 3.3                  |

| 0.06 | 13.5 | 17.3 | 74                | 136             | 2.6                  |

图 28. 可变负载的缓冲器

### 缓冲器设计示例

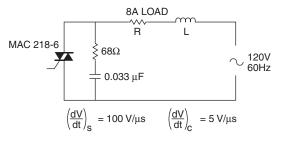

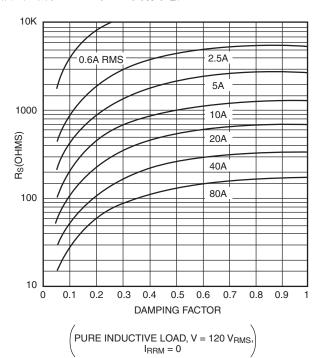

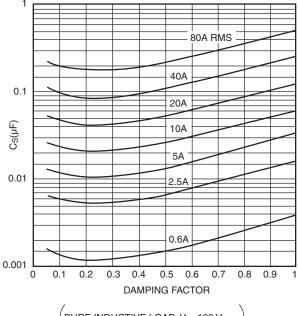

表 2 描述了缓冲器的 RC 值,用于  $\left(\frac{dV}{dt}\right)_s$  图 31 和 32 显示可能的 R 和 C 值,用于 5.0 V/ $\mu s$   $\left(\frac{dV}{dt}\right)_c$  ,假定纯感性负载。

表 2. 静态  $\frac{dV}{dt}$  设计 (E = 340 V,  $V_{peak}$  = 500 V,  $\rho$  = 0.3)

|     | 5.0V/µs |    | 50V/µs |     | 100V/µs |     |

|-----|---------|----|--------|-----|---------|-----|

| L   | С       | R  | С      | R   | С       | R   |

| μΗ  | μF      | Ω  | μF     | Ω   | μF      | Ω   |

| 47  |         |    |        |     | 0.15    | 10  |

| 100 |         |    | 0.33   | 10  | 0.1     | 20  |

| 220 |         |    | 0.15   | 22  | 0.03    | 47  |

|     |         |    |        |     | 3       |     |

| 500 |         |    | 0.06   | 51  | 0.01    | 110 |

|     |         |    | 8      |     | 5       |     |

| 100 | 3.0     | 11 | 0.03   | 100 |         |     |

| 0   |         |    | 3      |     |         |     |

## 瞬变与噪声抑制

瞬变可通过正常的电路工作从内部发生,或由外部环境引起。后一种情况特别令人烦恼,因为瞬变特性未定义。可应用静态描述。更高或更低的应力都有可能。相比持续时间长、电压高的瞬变,更有可能发生幅度更小、频率更高的瞬变。环境中不常发生的照明和负载切换会造成 3.0 kV 以下的瞬变电压。

图 29. 缓冲器电阻,用于 $\left(\frac{dV}{dt}\right)_{C} = 5.0 \text{ V/}\mu\text{s}$

PURE INDUCTIVE LOAD, V = 120 V<sub>RMS</sub>, I<sub>RRM</sub> = 0

图 30. 缓冲器电容,用于 $\left(\frac{dV}{dt}\right)_{c} = 5.0 \text{ V/}\mu\text{s}$

室内交流线路的自然频率和阻抗产生典型频率范围为 30 kHz 至 1.5 MHz 的阻尼振荡浪涌。浪涌幅度取决于线路和浪涌能量源。在远离源端的地方则几乎不会造成任何干扰。不存在瞬变抑制器时,以火花放电电压(室内交流线路上 6.0 kV)作为最大电压值。靠近进线口或重型布线中的瞬变具有较高的幅度、较长的持续时间和更多阻尼,因为这些位置电感较低。

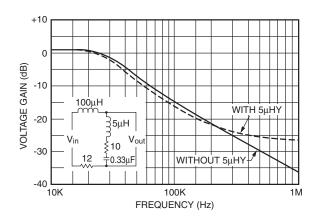

简单的 CRL 缓冲器是一个低通滤波器,可衰减高于其自然谐振的频率。稳态正弦波输入电压能够以同样的频率产生正弦波输出。无缓冲器电阻的情况下,下降速率接近每倍频程 12 dB。转角频率为衰减器的自然谐振频率。若阻尼系数较低,则峰值响应频率即为该频率。缓冲器电阻降低滤波器特性,在 ω = 1/(RC) 处产生一个向上的趋势。在频率高于此数值时,下降接近每倍频程6.0 dB。缓冲器电阻中的电感进一步降低了下降速率。

图 32 描述了图 27 中电路的频率响应。图 31 给出  $3.0~\rm{kV}~100~\rm{kHz}$  振铃波的理论响应。缓冲器降低晶闸管上的峰值电压。然而,将电感与缓冲器电阻串联时,快速上升的输入导致高  $\frac{\rm{dV}}{\rm{dt}}$  阶跃。利用瞬变抑制器限制输入电压可减少此阶跃。

图 31. 图 33 电路对 3.0 kV IEEE 587 振铃波的理论响应 (R<sub>SC</sub> = 27.5 Ω)

图 32. 缓冲器频率响应  $\left(\frac{V_{\text{out}}}{V_{\text{in}}}\right)$

若通过杂散电容进行耦合,则电路内的感应噪声与 $\frac{\mathrm{d}V}{\mathrm{d}t}$ 成比例;若通过互感进行耦合,则感应噪声与 $\frac{\mathrm{d}I}{\mathrm{d}t}$ 成比例。若要获得最好的抑制效果,则需使用限压器件以及限额 CRL 缓冲器。通过防止 $\frac{\mathrm{d}V}{\mathrm{d}t}$ 导通或击穿,晶闸管得到了良好的保护。应针对可能发生的情况设计电路,而非一般情况。

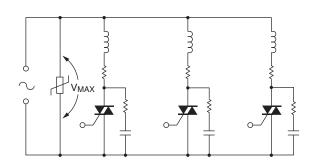

图 30 中,线路上的 MOV 保护大量并联电路分支及其负载。 MOV 定义最大输入电压以及负载上的  $\frac{dI}{dt}$  。通过缓冲器,它便可确定晶闸管上的最大  $\frac{dV}{dt}$  和峰值电压。 MOV 必须足够大,因为电路中几乎无浪涌限制阻抗可防止器件烧毁。

图 33. 限制线路电压

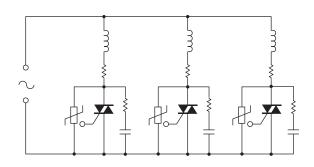

图 32 中,每个晶闸管两端都有一个独立的抑制器。负载阻抗限制来自线路的浪涌电能。它允许使用额定值较小的器件,但无负载保护。当晶闸管的负载是潜在的瞬变源时,这种配置能够保护每一个晶闸管。

图 34. 限制晶闸管电压

有必要将抑制器件直接放置在瞬变电能的源端,以防电能通过感应进入其它电路中。然而,针对负载与其控制晶闸管之间的电能注入却不存在任何保护。将抑制器直接放置在每个晶闸管两端可主动限制最大电压和缓冲器放电 $\frac{\mathrm{dI}}{\mathrm{dt}}$ 。

## 缓冲器应用示例

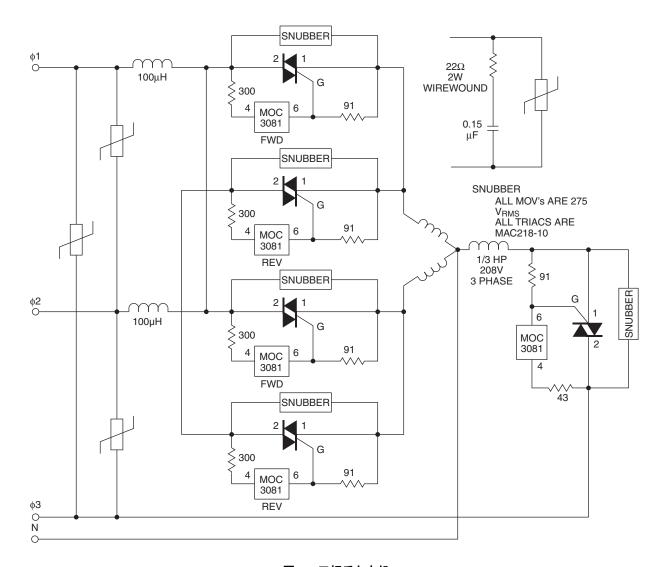

图 35 中, TRIAC 开关一个三相电机,并使其反向旋转。每对 TRIAC 都用作 SPDT 开关。 TRIAC 的导通动作会将线路相位之间的差分电压施加到阻断器件上,却不会带来电机阻抗限制电压上升速率的好处。加入电感,防止静态  $\frac{dV}{dt}$  引燃和线路间短路。

图 36 显示通过开关与其中一个绕组串联的电容,可实现裂相电容的反向驱动电机。正向和反向 TRIAC 用作 SPDT 开关。反向旋转电机可将电容上的电压急剧施加到阻断晶闸管。此处再次添加电感 L,防止 $\left(\frac{dV}{dt}\right)_s$  引燃阻断 TRIAC。若发生导通,正向和反向 TRIAC 使电容  $(C_S)$  短路并造成损坏。明智的做法是加入电阻  $R_S$  限制放电电流。

图 36. 裂相反向电机

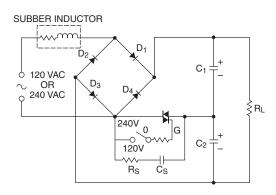

图 37 是一个 "抽头转换器"。该电路允许开关 120 或 240 vac 线路电压的电源。 TRIAC 导通时,该电路用作 传统倍压器,  $D_1$  和  $D_2$  交替导通半周期。在这种工作模式下,浪涌电流和  $\frac{dI}{dt}$  对 TRIAC 的可靠性产生不利影响。有必要使用串联阻抗防止损坏 TRIAC。

图 35. 三相反向电机

电路未倍压时, TRIAC 关断。在关断状态下,对 TRIAC 而言,线路与 CI 和 C2 交点处具有不同的电压 值。线路瞬变导致 $\left(\frac{dV}{dt}\right)_s$  引燃 TRIAC。高浪涌电流、 $\frac{dI}{dt}$  和过压可能损坏滤波器电容。为了保护器件,要求在 TRIAC 两端添加一个 RC 缓冲器,并在线路上串联一个电感。

图 37. 用于双路电压开关的抽头转换器

## 晶闸管类型

敏感的栅极晶闸管很容易导通,因为它们的触发电流要求较低。但是,相对类似的非敏感器件,它们的 $\frac{dV}{dt}$ 能力较差。应使用非敏感晶闸管,以获得较高的 $\frac{dV}{dt}$ 。

TRIAC 换向  $\frac{dV}{dt}$  额定值相比静态时的额定值低 5 至 20 倍。 $\frac{dV}{dt}$  额定值。

相位可控型光电耦合器相比过零光电耦合器和功率 TRIAC 具有更低的  $\frac{dV}{dt}$  额定值。如果存在直流电压元器件,或者要防止导通延迟,则需使用这些器件。

过零光电耦合器相比功率晶闸管具有更高的 $\frac{dV}{dt}$ 能力;并且在静态开关应用中,它们应代替相位可控型器件使用。

### 附录 A

### 测试缓冲器放电<u>dI</u> dt

附录 D 中的等式未考虑晶闸管的导通时间或通态电阻,因此等式预测了一个较高的 $\frac{dI}{dt}$ 。

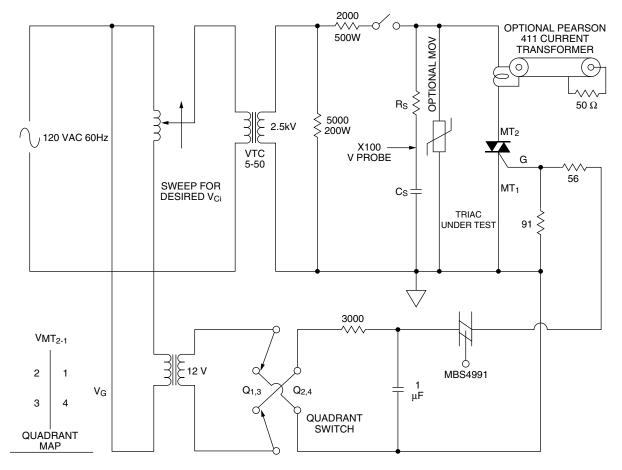

图 38 显示电路用于测试缓冲器放电 $\frac{dI}{dt}$ 。采用 MBS4991 提供触发脉冲,而工作象限是可以切换的。缓冲器安装在尽量靠近待测 TRIAC 的位置以减少电感,并保留电路中的电流变压器,以便将结果与测得的 $\frac{dI}{dt}$  值进行比较。

峰值电容电压应为多少?保守的做法是在最大额定 V<sub>DRM</sub>下进行测量,或在MOV的钳位电压下测量。

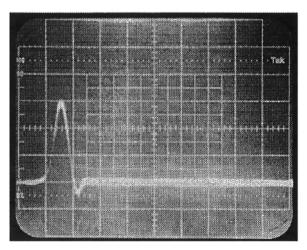

在不限制电阻的条件下,可用的最大电容是多少?图 39显示来自  $0.001 \mu F$  电容充电至 800 V 的电流脉冲。

1200 A/μs dI 损坏了 TRIAC。

MOV 自电容会不会损坏 TRIAC? 测试较大的  $40 \, J_{\rm A}$  2200 A 额定峰值电流 MOV。MOV 测量值为  $440 \, pF$ ,具有  $878 \, V$  击穿电压。其峰值放电电流  $(12 \, A)$  为  $470 \, pF$  电容的一半。这种情况是安全的。

图 38. 缓冲器放电 dI 测试

$\begin{aligned} &\text{HORIZONTAL SCALE} - 50 \text{ ms/DIV.} \\ &\text{VERTICAL SCALE} - 10 \text{ A/DIV.} \\ &\text{C}_S = 0.001 \text{ } \mu\text{F, V}_{Ci} = 800 \text{ V, R}_S = 0, L = 250 \text{ mH, R}_{TRIAC} = 10 \text{ OHMS} \end{aligned}$

图 39. 0.001 µF 电容的放电电流

## 附录 B

# 测量 $\left(\frac{dV}{dt}\right)_{S}$

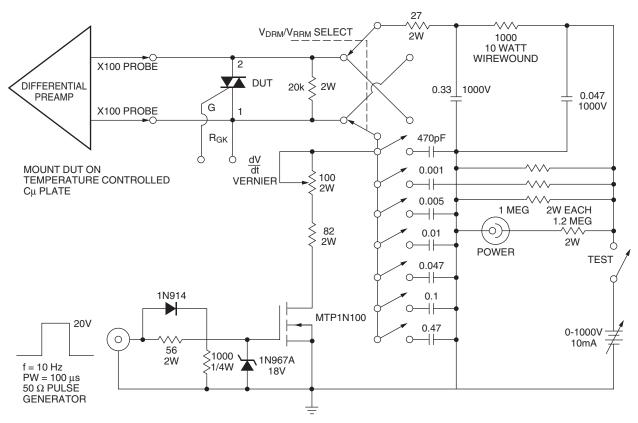

图 40 显示测量功率晶闸管静态  $\frac{dV}{dt}$  的测试电路。 1000 V FET 开关确保待测器件 (D.U.T.) 两端的电压从零快速上升。差分前置放大器允许使用 N 沟道器件,同时出于安全起见,保持存储示波器外壳接地。电压上升的速率可通过可变 RC 时间常数进行调节。充电电阻较低,以防晶闸管自电容导致的波形失真,但又足够大,可防止导通 损坏 D.U.T。  $\frac{dI}{dt}$  。 将微型范围开关、电容和 G-K 网络靠近待测器件安装可减少杂散电感,允许以高于  $10~kV/\mu s$  进行测试。

ALL COMPONENTS ARE NON-INDUCTIVE UNLESS SHOWN

图 40. 功率晶闸管的静态 dV dt 测量电路

### 附录 C

# 测量 $\left(\frac{dV}{dt}\right)_{c}$

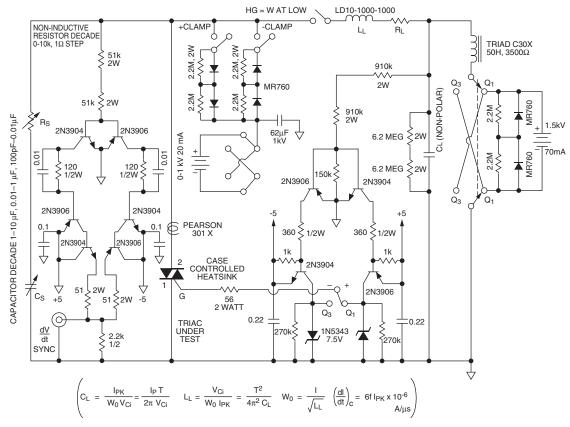

测量换向  $\frac{dV}{dt}$  的测试夹具如图 41 所示。它是一个电容放电电路,带有串联负载谐振。单脉冲测试有助于温度控制,并允许使用功率更低的元器件。负载电容中的限制电能降低烧伤与触电危险。传统负载和缓冲器电路提供恢复和阻尼性能,与在应用中相同。

负载电容上的电压触发 D.U.T。当负载电容电压过零且 TRIAC 电流达到峰值时,它可端接栅极电源。

每种  $V_{DRM}$ 、  $I_{TM}$  组合都需要不同的元器件。利用图 41 中的等式计算它们的数值。

商用扼流圈简化所需电感的构建。应当通过增加磁芯中的气隙调节电感值。移除磁级片可降低4到6的电感,但会扩展不饱和电流。

负载电容由一组平行的 1500 V 直流非极性单元组成,单个泄放电阻搭配单个电容安装,保证安全性。

可选的可调节电压钳位防止 TRIAC 击穿。

若要测量 $\left(\frac{dV}{dt}\right)$ ,将存储示波器与电流波形同步,并验证正确的电流幅度和周期。必要的话,可以增加电容上的初始电压以补偿线圈中的损耗。调节缓冲器,直到第一个半周期后器件无法关断。在最快通流条件下检查电压上升的速率。

图 41.  $\left(\frac{dV}{dt}\right)_{C}$  测试电路,用于功率 TRIAC

## 附录 D

# dV 推导

#### 定义

1.0

$$R_T = R_L + R_S = Total Resistance$$

1.1

$$M = \frac{R_S}{R_T}$$

Snubber Divider Ratio

1.1

$$M = \frac{R_S}{R_T} = \text{Snubber Divider Ratio}$$

1.2  $\omega 0 = \frac{1}{\sqrt{LC_S}} = \text{Undamped Natural Frequency}$

$\omega$  = Damped Natural Frequency

1.3

$$\alpha = \frac{R_T}{2L}$$

Wave Decrement Factor

1.4

$$\chi^2 = \frac{1/2LI^2}{1/2CV^2} = \frac{Initial\ Energy\ In\ Inductor}{Final\ Energy\ In\ Capaitor}$$

1.5

$$\chi = \frac{I}{E} \sqrt{\frac{L}{C}} = Initial Current Factor$$

1.6

$$\rho = \frac{R_T}{2} \sqrt{\frac{C}{L}} = \frac{\alpha}{\omega 0} = Damping Factor$$

1.7

$$V_{O_L} = E - R_S I$$

= Initial voltage drop at t = 0 across the load

1.8

$$\xi = \frac{I}{C_s} - \frac{ER_L}{L}$$

$$\left(\frac{dV}{dt}\right)_0$$

= initial instantaneous  $\frac{dV}{dt}$  at  $t=0$ , ignoring any instantaneous voltage step at

$$t=0$$

, 因为  $I_{RRM}$

2.0 When

$$I = 0$$

,  $\left(\frac{dV}{dt}\right)_0 = \frac{ER_S}{L}$

$$\left(\frac{dV}{dt}\right)_{max}$$

= Maximum Instantaneous  $\frac{dV}{dt}$

$$t_{max}$$

= Time of maximum instantaneous  $\frac{dV}{dt}$

$t_{peak}$  = Time of maximum instantaneous peak voltage across thyristor

Average

$$\frac{dV}{dt} = V_{PK}/t_{PK} =$$

Slope of the secant line from  $t=0$  through  $V_{PK}$

$V_{PK}$  = Maximum instantaneous voltage across the thyristor.

#### (取决于阻尼系数): 常数

2.1 No Damping

$$(\rho = 0)$$

$$\omega = \omega_0$$

$$R_T = \alpha = \rho = 0$$

2.2 Underdamped

$$(0 < \rho < 1)$$

$$\omega = \sqrt{\omega 0^2 - \alpha^2} = \omega 0 \sqrt{1 - \rho^2}$$

2.3 Critial Damped (

$$\rho = 1$$

)

$$\alpha = \omega 0, \omega = 0, R = 2\sqrt{\frac{L}{C}}, C = \frac{2}{\alpha R_T}$$

2.4 Overdamped

$$(\rho > 1)$$

$$\omega = \sqrt{\alpha^2 - \omega 0^2} = \omega 0 \sqrt{\rho^2 - 1}$$

#### 图 42 中电流和电压的拉普拉斯变换为:

$$3.0 \qquad i_{(S)} = \frac{E/L + SI}{S^2 + S\frac{R_T}{L} + \frac{1}{LC}}; \ e = \frac{E}{S} - \frac{SV_{O_L} - \xi}{S^2 + \frac{R_T}{L}S + \frac{1}{LC}}$$

#### 图 42. 负载和缓冲器的等效电路

#### 所有条件下的拉普拉斯逆变换:

#### 欠阻尼 (典型缓冲器设计)

4.0

$$e = E - V_{O_L} \left[ Cos(\omega t) - \frac{\alpha}{\omega} sin(\omega t) \right] e^{-\alpha t} + \frac{\xi}{\omega} sin(\omega t) e^{-\alpha t}$$

$$4.1 \qquad \frac{de}{dt} = V_{O_L} \left[ 2\alpha Cos(\omega t) + \frac{(\omega^2 - \alpha^2)}{\omega} sin(\omega t) \right] e^{-\alpha t} + \xi \left[ Cos(\omega t) - \frac{\alpha}{\omega} sin(\omega t) \right] e^{-\alpha t}$$

4.2

$$t_{PK} = \frac{1}{\omega} tan^{-1} \left[ -\frac{2\alpha V_{O_L + \xi}}{V_{O_L} \left(\frac{\omega^2 - \alpha^2}{\omega}\right) - \frac{\xi \alpha}{\omega}} \right]$$

When

$$M = 0$$

,  $R_S = 0$ ,  $I = 0$ ;  $\omega t_{PK} = \pi$

$$V_{PK} = E + \frac{\alpha}{\omega_0} - \alpha t_{PK} \sqrt{{\omega_0}^2 {V_{O_L}}^2 + 2\alpha \xi V_{O_L} + \xi^2}$$

When I = 0, R<sub>L</sub> = 0, M = 1:

$$4.4 \qquad \frac{V_{PK}}{E} = (1 + e^{-\alpha} t_{PK})$$

$$Average \frac{dV}{dt} = \frac{V_{PK}}{t_{PK}}$$

$$4.5 \qquad t_{\text{max}} = \frac{1}{\omega} ATN \left[ \frac{\omega(2\alpha\xi - V_{O_L}(\omega^2 - 3\alpha^2))}{V_{O_L}(\alpha^3 - 3\alpha\omega^2) + \xi(\alpha^2 - \omega^2)} \right]$$

4.6

$$\left(\frac{dV}{dt}\right)_{max} = \sqrt{V_{O_L}^2 \omega_0^2 + 2\alpha\xi \ V_{O_L} + \xi^2} e^{-\alpha t \ max}$$

#### 无阻尼

5.0

$$e = E(1 - Cos(\omega_0 t)) + \frac{I}{C\omega_0} sin(\omega_0 t)$$

5.1

$$\frac{de}{dt} = E\omega_0 \sin(\omega_0 t) + \frac{I}{C} \cos(\omega_0 t)$$

5.2

$$\left(\frac{dV}{dt}\right)_0 = \frac{I}{C} = 0 \text{ when } I = 0$$

$$t_{PK} \, = \, \frac{\pi - \tan^{-1}\!\!\left(\!\frac{I}{CE\omega_0}\!\right)}{\omega_0} \label{eq:tpk}$$

5.4

$$V_{PK} = E + \sqrt{E^2 + \frac{I^2}{\omega_0^2 C^2}}$$

$$5.5 \qquad \left(\frac{\mathrm{dV}}{\mathrm{dt}}\right)_{\mathrm{AVG}} = \frac{\mathrm{V}_{\mathrm{PK}}}{\mathrm{t}_{\mathrm{PK}}}$$

$$5.6 \hspace{1cm} t_{max} = \frac{I}{\omega_0} \bigg[ tan^{-1} \bigg( \frac{\omega_0 EC}{I} \bigg) \bigg] = \frac{I}{\omega_0} \, \frac{\pi}{2} \hspace{1cm} when \hspace{1cm} I = 0$$

5.7

$$\left(\frac{dV}{dt}\right)_{max} = \frac{I}{C} \sqrt{E^2 \omega_0^2 C^2 + I^2} = \omega_0 E \text{ when } I = 0$$

### 关键阻尼

6.0

$$e = E - V_{O_L} (1 - \alpha t) e^{-\alpha t} + \xi t e^{-\alpha t}$$

6.1

$$\frac{de}{dt} = \left[\alpha V_{O_L}(2 - \alpha t) + \xi (1 - \alpha t)\right] e^{-\alpha}$$

6.1

$$\frac{de}{dt} = \left[\alpha V_{O_L} (2 - \alpha t) + \xi (1 - \alpha t)\right] e^{-\alpha t}$$

6.2

$$t_{PK} = \frac{2 + \frac{\xi}{2V_{OL}}}{\alpha + \frac{\xi}{V_{OL}}}$$

6.3

$$V_{PK} = E - [V_{O_L}(1 - \alpha t_{PK}) - \xi t_{PK}]e^{-\alpha} t_{PK}$$

6.4 Average

$$\frac{dV}{dt} = \frac{V_{PK}}{t_{PK}}$$

When

$$I = 0, R_S = 0, M = 0$$

e(t) rises asymptotically to E.  $t_{PK}$  and average  $\frac{dV}{dt}$  do not exist.

6.5

$$t_{\text{max}} = \frac{3\alpha V_{O_L} + 2\xi}{\alpha^2 V_{O_L} + \alpha \xi}$$

When

$$I = 0$$

,  $t_{max} = 0$

For

$$\frac{R_S}{R_T} \ge 3/4$$

then

$$\frac{dV}{dt}_{max} = \left(\frac{dV}{dt}\right)_0$$

$$6.6 \qquad \left(\frac{dV}{dt}\right)_{max}$$

$$= \left[\alpha V_{O_L} (2 - \alpha t_{max}) + \xi (1 - \alpha t_{max})\right] e^{-\alpha t_{max}}$$

## 附录 E

# 缓冲器放电 dI 推导

### 过阻尼

1.0

$$i = \frac{V_{CS}}{\omega L_S} \alpha^{-\alpha t} \sinh(\omega t)$$

$$1.1 \qquad i_{PK} = V_{C_S} \sqrt{\frac{C_S}{L_S}} e^{-\alpha} t_{PK}$$

1.2

$$t_{PK} = \frac{1}{\omega} tanh^{-1} \left[\frac{\omega}{\alpha}\right]$$

### 关键阻尼

$$i = \frac{V_{C_S}}{L_S} t e^{-\alpha t}$$

$$2.1 i_{PK} = 0.736 \frac{V_{C_s}}{R_s}$$

$$2.2 t_{PK} = \frac{1}{\alpha}$$

#### 欠阻尼

3.0

$$i = \frac{V_{C_s}}{\omega L_s} e^{-\alpha t} \sin(\omega t)$$

$$3.1 i_{PK} = V_{C_S} \sqrt{\frac{C_S}{L_S}} e^{-\alpha} t_{PK}$$

3.2

$$t_{PK} = \frac{1}{\omega} tan^{-1} \left[ \frac{\omega}{\alpha} \right]$$

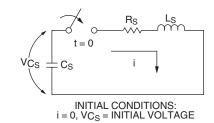

图 43. 缓冲器放电等效电路

#### 无阻尼

$$4.0 i = \frac{V_{C_s}}{\omega L_s} \sin(\omega t)$$

$$4.1 i_{PK} = V_{C_S} \sqrt{\frac{C_S}{L_S}}$$

$$4.2 t_{PK} = \frac{\pi}{2\omega}$$

## 参考文献

Bird, B. M. and K. G. King. *An Introduction To Power Electronics*. John Wiley & Sons, 1983, pp.250 - 281.

Blicher, Adolph. Thyristor Physics. Springer-Verlag, 1976.

Gempe, Horst. "Applications of Zero Voltage Crossing Optically Isolated TRIAC Drivers," AN982, Motorola Inc., 1987

"Guide for Surge Withstand Capability (SWC) Tests," ANSI 337.90A-1974, IEEE Std 472 - 1974.

"IEEE Guide for Surge Voltages in Low-Voltage AC Power Circuits," ANS1/IEEE C62.41 -1980, IEEE Std 587 - 1980

Ikeda, Shigeru and Tsuneo Araki. "The  $\frac{dI}{dt}$  Capability of Thyristors," *Proceedings of the IEEE*, Vol.53, No.8, August 1967.

Kervin, Doug."The MOC3011 and MOC3021," EB-101, Motorola Inc., 1982.

McMurray, William. "Optimum Snubbers For Power Semicondutors," *IEEE Transactions On Industry Applications*, Vol.1A-8, September/October 1972.

Rice, L. R. "Why R-C Networks And Which One For Your Converter," Westinghouse Tech Tips 5-2.

"Saturable Reactor For Increasing Turn-On Switching Capability," SCR Manual Sixth Edition, General Electric, 1979.

Zell, H. P. "Design Chart For Capacitor-Discharge Pulse Circuits," *EDN Magazine*, June 10, 1968.

#### **DISCLAIMER**

FAIRCHILD SEMICONDUCTOR RESERVES THE RIGHT TO MAKE CHANGES WITHOUT FURTHER NOTICE TO ANY PRODUCTS HEREIN TO IMPROVE RELIABILITY, FUNCTION OR DESIGN.FAIRCHILD DOES NOT ASSUME ANY LIABILITY ARISING OUT OF THE APPLICATION OR USE OF ANY PRODUCT OR CIRCUIT DESCRIBED HEREIN; NEITHER DOES IT CONVEY ANY LICENSE UNDER ITS PATENT RIGHTS, NOR THE RIGHTS OF OTHERS.

#### LIFE SUPPORT POLICY

FAIRCHILD'S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF THE PRESIDENT OF FAIRCHILD SEMICONDUCTOR CORPORATION. As used herein:

- Life support devices or systems are devices or systems which, (a) are intended for surgical implant into the body, or (b) support or sustain life, or (c) whose failure to perform when properly used in accordance with instructions for use provided in the labeling, can be reasonably expected to result in significant injury to the user.

- A critical component is any component of a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system, or to affect its safety or effectiveness.

ON Semiconductor and in are trademarks of Semiconductor Components Industries, LLC dba ON Semiconductor or its subsidiaries in the United States and/or other countries. ON Semiconductor owns the rights to a number of patents, trademarks, copyrights, trade secrets, and other intellectual property. A listing of ON Semiconductor's product/patent coverage may be accessed at <a href="www.onsemi.com/site/pdt/Patent-Marking.pdf">www.onsemi.com/site/pdt/Patent-Marking.pdf</a>. ON Semiconductor reserves the right to make changes without further notice to any products herein. ON Semiconductor assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. Buyer is responsible for its products and applications using ON Semiconductor products, including compliance with all laws, regulations and safety requirements or standards, regardless of any support or applications information provided by ON Semiconductor. "Typical" parameters which may be provided in ON Semiconductor data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. ON Semiconductor does not convey any license under its patent rights nor the rights of others. ON Semiconductor products are not designed, intended, or authorized for use as a critical component in life support systems or any FDA Class 3 medical devices or medical devices with a same or similar classification in a foreign jurisdiction or any devices intended for implantation in the human body. Should Buyer purchase or use ON Semiconductor products for any such unintended or unauthorized application, Buyer shall indemnify and hold ON Semiconductor and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and exp

#### **PUBLICATION ORDERING INFORMATION**

#### LITERATURE FULFILLMENT:

Literature Distribution Center for ON Semiconductor 19521 E. 32nd Pkwy, Aurora, Colorado 80011 USA Phone: 303-675-2175 or 800-344-3860 Toll Free USA/Canada Fax: 303-675-2176 or 800-344-3867 Toll Free USA/Canada Email: orderlit@onsemi.com N. American Technical Support: 800-282-9855 Toll Free USA/Canada

Europe, Middle East and Africa Technical Support:

Phone: 421 33 790 2910

Japan Customer Focus Center

Phone: 81-3-5817-1050

ON Semiconductor Website: www.onsemi.com

Order Literature: http://www.onsemi.com/orderlit

For additional information, please contact your local Sales Representative