|                                   |                  |        |                   | Lī                      | ΓR                |                     |                           |           | DESC | RIPTI | ON                        |                             |                             |                                                    | D                                                | ATE                                  |                                | -                               | APPR        | OVED          | )         |

|-----------------------------------|------------------|--------|-------------------|-------------------------|-------------------|---------------------|---------------------------|-----------|------|-------|---------------------------|-----------------------------|-----------------------------|----------------------------------------------------|--------------------------------------------------|--------------------------------------|--------------------------------|---------------------------------|-------------|---------------|-----------|

|                                   |                  |        |                   |                         |                   |                     |                           |           |      |       |                           |                             |                             |                                                    |                                                  |                                      |                                |                                 |             |               |           |

|                                   |                  |        |                   |                         |                   |                     |                           |           |      |       |                           |                             |                             |                                                    |                                                  |                                      |                                |                                 |             |               |           |

|                                   |                  |        |                   | I                       |                   | I                   |                           |           |      |       |                           |                             |                             | I                                                  |                                                  |                                      | ı                              |                                 |             |               |           |

|                                   |                  |        |                   |                         |                   |                     |                           |           |      |       |                           |                             |                             |                                                    |                                                  |                                      |                                |                                 |             |               |           |

|                                   |                  |        |                   |                         |                   |                     |                           |           |      |       |                           |                             |                             |                                                    |                                                  |                                      |                                |                                 |             |               |           |

|                                   |                  |        |                   |                         |                   |                     |                           |           |      |       |                           |                             |                             |                                                    |                                                  |                                      |                                |                                 |             |               |           |

|                                   |                  |        |                   |                         |                   |                     |                           |           |      |       |                           |                             |                             |                                                    |                                                  |                                      |                                |                                 |             |               |           |

|                                   |                  |        |                   |                         |                   |                     |                           |           |      |       |                           |                             |                             |                                                    |                                                  |                                      |                                |                                 |             |               |           |

|                                   |                  |        |                   |                         |                   |                     |                           |           |      |       |                           |                             |                             |                                                    |                                                  |                                      |                                |                                 |             |               |           |

|                                   |                  |        |                   |                         |                   |                     |                           |           |      |       |                           |                             |                             |                                                    |                                                  |                                      |                                |                                 |             |               |           |

|                                   |                  |        |                   |                         |                   |                     |                           |           |      |       |                           |                             |                             |                                                    |                                                  |                                      |                                |                                 |             |               |           |

|                                   |                  |        |                   |                         |                   |                     |                           |           |      |       |                           |                             |                             |                                                    |                                                  |                                      |                                |                                 |             |               |           |

|                                   |                  |        |                   |                         |                   |                     |                           |           |      |       |                           |                             |                             |                                                    |                                                  |                                      |                                |                                 |             |               |           |

|                                   |                  |        |                   |                         |                   |                     |                           |           |      |       |                           |                             |                             |                                                    |                                                  |                                      |                                |                                 |             |               |           |

|                                   |                  |        |                   |                         |                   |                     |                           |           |      |       |                           |                             |                             |                                                    |                                                  |                                      |                                |                                 |             |               |           |

|                                   |                  |        |                   |                         |                   |                     |                           |           |      |       |                           |                             |                             |                                                    |                                                  |                                      |                                |                                 |             |               |           |

|                                   |                  |        |                   |                         |                   |                     |                           |           |      |       |                           |                             |                             |                                                    |                                                  |                                      |                                |                                 |             |               |           |

|                                   |                  |        |                   |                         |                   |                     |                           |           |      |       |                           |                             |                             |                                                    |                                                  |                                      |                                |                                 |             |               |           |

|                                   |                  |        |                   |                         |                   |                     |                           |           |      |       |                           |                             |                             |                                                    |                                                  |                                      |                                |                                 |             |               |           |

|                                   |                  |        |                   |                         |                   |                     |                           |           |      |       |                           |                             |                             |                                                    |                                                  |                                      |                                |                                 |             |               |           |

|                                   |                  |        |                   |                         |                   |                     |                           |           |      |       |                           |                             |                             |                                                    |                                                  |                                      |                                |                                 |             |               |           |

| enareo                            | d in acco        | rdance | with AS           | ME Y1                   | 4 24              |                     |                           |           |      |       |                           |                             |                             |                                                    |                                                  |                                      | Ve                             | ndor it                         | em di       | rawing        |           |

|                                   | d in accoi       | rdance | with AS           | ME Y1                   | 4.24              |                     |                           |           |      |       |                           |                             |                             |                                                    |                                                  |                                      | Ve                             | ndor it                         | em dı       | rawing        | <u> </u>  |

| EV                                | d in accor       | rdance | with AS           | ME Y1                   | 4.24              |                     |                           |           |      |       |                           |                             |                             |                                                    |                                                  |                                      | Ve                             | ndor it                         | em di       | rawing        | l         |

| EV<br>AGE                         | d in accor       | rdance | with AS           | ME Y1                   | 4.24              |                     |                           |           |      |       |                           |                             |                             |                                                    |                                                  |                                      | Ve                             | ndor it                         | em di       | rawing        | 1         |

| EV<br>AGE<br>EV                   | d in accor       | rdance | with AS           | ME Y1                   | 4.24              |                     |                           |           |      |       |                           |                             |                             |                                                    |                                                  |                                      | Ve                             | ndor it                         | em di       | rawing        |           |

| EV<br>AGE<br>EV<br>AGE            |                  |        | with AS           | ME Y1                   | 4.24              |                     |                           |           |      |       |                           |                             |                             |                                                    |                                                  |                                      | Ve                             | ndor it                         | em di       | rawing        |           |

| EV<br>AGE<br>EV<br>AGE            | ATUS             | F      |                   | ME Y1                   | 4.24              | 2                   | 3                         | 4         | 5    | 6     | 7                         | 8                           | 9                           | 10                                                 | 11                                               | 12                                   | Ve                             | ndor it                         | em di       | rawing        |           |

| EV AGE EV AGE EV ST/F PAG         | ATUS<br>ES       | F      | REV               |                         | 1                 |                     | 3                         | 4         | 5    | 6     | 7                         | 8                           | 9                           |                                                    |                                                  |                                      | 13                             | 14                              | em di       | rawing        |           |

| EV AGE EV AGE EV ST/F PAG         | ATUS<br>ES       | F      | REV               | ME Y1                   | 1<br>ED BY        | ,                   | 3<br>Nguy                 |           | 5    | 6     | 7                         | 8                           | C                           | DLA<br>OLUN                                        | LAND<br>IBUS,                                    | AND<br>OHIC                          | 13<br>MARI<br>0 432            | 14<br>TIME<br>18-399            | 90          | rawing        |           |

| EV AGE EV AGE EV ST/F PAG         | ATUS<br>ES       | F      | REV<br>PAGE<br>PR | EPARE                   | 1<br>ED BY        | ,                   |                           |           | 5    | 6     |                           |                             | C                           | DLA<br>OLUN                                        | LAND<br>IBUS,                                    | AND                                  | 13<br>MARI<br>0 432            | 14<br>TIME<br>18-399            | 90          | rawing        |           |

| EV AGE EV AGE EV ST/F PAG MIC N/  | ATUS<br>ES       | F      | REV<br>PAGE<br>PR |                         | 1 ED BY           | Phu H.              | Nguy                      | en        | 5    | 6     | TIT                       | LE                          | C<br>http                   | DLA<br>OLUN                                        | LAND<br>IBUS,<br>w.land                          | AND<br>OHIC                          | 13<br>MARI<br>0 432            | 14<br>ITIME<br>18-399<br>ne.dla | 90<br>.mil/ |               |           |

| EV AGE EV ST/F PAG MIC N//        | ATUS<br>ES<br>ZA | F F    | REV<br>PAGE<br>PR | EPARE                   | 1 ED BY           | Phu H.<br>Phu H.    |                           | en        | 5    | 6     | TITI<br>MIC               | L <b>E</b>                  | c<br>http                   | DLA<br>OLUN<br>:://ww                              | LAND<br>IBUS,<br>w.land                          | AND<br>OHIC<br>dandm                 | 13<br>MARI<br>0 432            | 14<br>TIME<br>18-399<br>ne.dla  | 90<br>.mil/ | D, 14         | 1-        |

| EV AGE EV AGE EV ST/F PAG MIC N// | ATUS<br>ES       | F F    | REV<br>PAGE<br>PR | EPARE                   | 1 ED BY FED BY    | Phu H.<br>Phu H.    | Nguy                      | en<br>en  | 5    | 6     | TITI<br>MIC<br>BIT        | L <b>E</b><br>CROC<br>, 125 | http<br>SIRCU               | DLA<br>OLUN<br>O://ww<br>JIT, [                    | LAND<br>MBUS,<br>w.land                          | AND<br>OHIC<br>dandm                 | 13<br>MARI<br>9 432<br>naritin | 14<br>TIME<br>18-399<br>ne.dla  | eo<br>.mil/ | D, 14<br>LOG- | 4-<br>-TC |

| EV AGE EV AGE EV ST/F PAG MIC N// | ATUS<br>ES<br>ZA | F F    | REV<br>PAGE<br>PR | EPARE                   | 1 ED BY FED BY    | Phu H.<br>Phu H.    | Nguy                      | en<br>en  | 5    | 6     | TITI<br>MIC<br>BIT        | L <b>E</b><br>CROC<br>, 125 | http<br>SIRCU               | DLA<br>OLUN<br>O://ww<br>JIT, [                    | LAND<br>MBUS,<br>w.land                          | AND<br>OHIC<br>dandm                 | 13<br>MARI<br>9 432<br>naritin | 14<br>TIME<br>18-399<br>ne.dla  | eo<br>.mil/ | D, 14         | 4-<br>-TC |

| AGE EV STAGE EV STAGE MIC NA      | ATUS<br>ES<br>ZA | F F    | PAGE PR           | EPARE                   | 1 D BY F ED BY Th | Phu H. Phu H. homas | Nguy                      | en<br>en  | 5    | 6     | TITI<br>MIC<br>BIT<br>DIG | L <b>E</b><br>CROC<br>, 125 | http<br>SIRCU               | DLA<br>COLUN<br>D://www<br>JIT, [<br>PS SI<br>NVER | LAND<br>IBUS,<br>w.land<br>DIGIT<br>ERIA<br>RTER | AND<br>OHIC<br>dandm<br>AL-L<br>L LV | 13 MARI 0 4320 naritin         | 14<br>TIME<br>18-399<br>ne.dla  | eo<br>.mil/ | D, 14<br>LOG- | 1-<br>-TC |

| AGE EV STAGE EV STAGE MIC NA      | ATUS<br>ES<br>ZA | F F    | PAGE PR CH        | EPARE                   | 1 D BY F ED BY Th | Phu H. Phu H. homas | Nguyo<br>Nguyo<br>s M. Ho | en<br>en  | 5    | 6     | TITI<br>MIC<br>BIT<br>DIG | LE<br>CROC<br>, 125         | http<br>SIRCU               | DLA<br>COLUN<br>D://www<br>JIT, [<br>PS SI<br>NVER | LAND<br>IBUS,<br>w.land<br>DIGIT<br>ERIA<br>RTER | AND<br>OHIC<br>dandm                 | 13 MARI 0 4320 naritin         | 14<br>TIME<br>18-399<br>ne.dla  | eo<br>.mil/ | D, 14<br>LOG- | 1-<br>-TO |

| EV AGE EV AGE EV STAFF PAG MIC NA | ATUS<br>ES<br>ZA | F F    | PAGE PR CH        | EPARE<br>ECKEI<br>PROVE | 1 D BY F ED BY Th | Phu H. Phu H. homas | Nguyo<br>Nguyo<br>s M. Ho | en en ess | 5    | 6     | TITI<br>MIC<br>BIT<br>DIG | LE<br>CROC<br>, 125         | c<br>http<br>CIRCU<br>5 MSI | DLA<br>COLUM<br>:://ww<br>JIT, [<br>PS SI<br>NVER  | LAND<br>IBUS,<br>w.land<br>DIGIT<br>ERIA<br>RTER | AND<br>OHIC<br>dandm<br>AL-L<br>L LV | 13 MARI 0 4320 naritin         | 14<br>TIME<br>18-399<br>ne.dla  | eo<br>.mil/ | D, 14<br>LOG- | 1-<br>-TC |

**REVISIONS**

### 1. SCOPE

- 1.1 <u>Scope</u>. This drawing documents the general requirements of a high performance quad, 14-bit, 125 MSPS serial LVDS 1.8 V analog-to-digital converter microcircuit, with an operating temperature range of -55°C to +125°C.

- 1.2 <u>Vendor Item Drawing Administrative Control Number</u>. The manufacturer's PIN is the item of identification. The vendor item drawing establishes an administrative control number for identifying the item on the engineering documentation:

| V62/13627 | - | <u>01</u><br> | X<br>T       | 투           |

|-----------|---|---------------|--------------|-------------|

| Drawing   |   | Device type   | Case outline | Lead finish |

| number    |   | (See 1.2.1)   | (See 1.2.2)  | (See 1.2.3) |

1.2.1 Device type(s).

| Device type | <u>Generic</u> | Circuit function                                                     |  |  |  |  |

|-------------|----------------|----------------------------------------------------------------------|--|--|--|--|

| 01          | AD9253-EP      | Quad, 14-bit, 125 MSPS serial LVDS 1.8 V analog-to-digital converter |  |  |  |  |

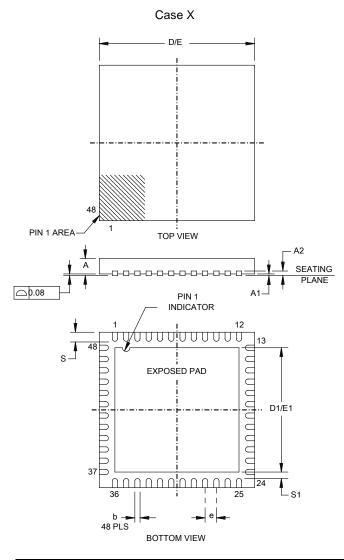

1.2.2 <u>Case outline(s)</u>. The case outlines are as specified herein.

| Outline letter | Number of pins | JEDEC PUB 95      | Package style                      |

|----------------|----------------|-------------------|------------------------------------|

| Χ              | 48             | JEDEC MO-220-WKKD | Lead Lead Frame Chip Scale Package |

1.2.3 <u>Lead finishes</u>. The lead finishes are as specified below or other lead finishes as provided by the device manufacturer:

| Finish designator | <u>Material</u>      |  |  |  |

|-------------------|----------------------|--|--|--|

| Α                 | Hot solder dip       |  |  |  |

| В                 | Tin-lead plate       |  |  |  |

| С                 | Gold plate           |  |  |  |

| D                 | Palladium            |  |  |  |

| E                 | Gold flash palladium |  |  |  |

| Z                 | Other                |  |  |  |

| DLA LAND AND MARITIME | SIZE | CODE IDENT NO. | DWG NO.          |

|-----------------------|------|----------------|------------------|

| COLUMBUS, OHIO        | A    | <b>16236</b>   | <b>V62/13627</b> |

|                       |      | REV            | PAGE 2           |

# 1.3 Absolute maximum ratings. 1/

| AVDD to AGND                                                 | -0.3 V to +2.0 V |

|--------------------------------------------------------------|------------------|

| DRVDD to AGND                                                | -0.3 V to +2.0 V |

| Digital outputs (D0±x, D1±x, DCO+, DCO-, FCO+, FCO-) to AGND | -0.3 V to +2.0 V |

| CLK+, CLK- to AGND                                           |                  |

| VIN+x, VIN-x to AGND                                         | -0.3 V to +2.0 V |

| SCLK/DTP, SDIO/OLM, CSB to AGND                              | -0.3 V to +2.0 V |

| SYNC, PDWN to AGND                                           | -0.3 V to +2.0 V |

| RBIAS to AGND                                                | -0.3 V to +2.0 V |

| VREF, SENSE to AGND                                          | -0.3 V to +2.0 V |

| Operating temperature range (Ambient)                        | -55°C to +125°C  |

| Maximum junction temperature                                 | 150°C            |

| Lead temperature (Soldering, 10 sec)                         | 300°C            |

| Storage temperature range (Ambient)                          | -65°C to 150°C   |

#### 1.5 Thermal characteristics.

#### Thermal resistance

| Case outline | Air flow<br>velocity<br>(m/sec) | θ <sub>JA</sub> <u>2</u> / | Ψυτ  | Ψлв            | θ <sub>JC</sub><br>TOP | θ <sub>ЈС</sub><br>воттом | Unit |

|--------------|---------------------------------|----------------------------|------|----------------|------------------------|---------------------------|------|

| Case X       | 0.0                             | 20.3                       | 0.10 | 5.9            | 6.1                    | 1.0                       | °C/W |

|              | 1.0                             | 17.6                       | 0.16 | N/A <u>3</u> / | N/A <u>3</u> /         | N/A <u>3</u> /            | °C/W |

|              | 2.5                             | 16.5                       | 0.20 | N/A <u>3</u> / | N/A <u>3</u> /         | N/A <u>3</u> /            | °C/W |

## 2. APPLICABLE DOCUMENTS

JEDEC - SOLID STATE TECHNOLOGY ASSOCIATION (JEDEC)

JEP95 - Registered and Standard Outlines for Semiconductor Devices

(Copies of these documents are available online at <a href="http://www.jedec.org">http://www.jedec.org</a> or from JEDEC – Solid State Technology Association, 3103 North 10th Street, Suite 240–S, Arlington, VA 22201-2107).

| DLA LAND AND MARITIME | SIZE | CODE IDENT NO. | DWG NO.          |

|-----------------------|------|----------------|------------------|

| COLUMBUS, OHIO        | A    | <b>16236</b>   | <b>V62/13627</b> |

|                       |      | REV            | PAGE 3           |

Stresses above those listed under "Absolute maximum ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions above those beyond indicated in the operational section of this specifications is not implied. Exposure to absolute maximum rated conditions for extended periods may affect device reliability.

$<sup>\</sup>underline{2}/$   $\theta_{JA}$  for a 4-layer printed circuit board (PCB) with solid ground plane (simulated). Exposed pad soldered to PCB.

$<sup>\</sup>frac{1}{3}$ / N/A = not applicable.

### 3. REQUIREMENTS

- 3.1 <u>Marking</u>. Parts shall be permanently and legibly marked with the manufacturer's part number as shown in 6.3 herein and as follows:

- A. Manufacturer's name, CAGE code, or logo

- B. Pin 1 identifier

- C. ESDS identification (optional)

- 3.2 <u>Unit container</u>. The unit container shall be marked with the manufacturer's part number and with items A and C (if applicable) above.

- 3.3 <u>Electrical characteristics</u>. The maximum and recommended operating conditions and electrical performance characteristics are as specified in 1.3, 1.4, and table I herein.

- 3.4 Design, construction, and physical dimension. The design, construction, and physical dimensions are as specified herein.

- 3.5 Diagrams.

- 3.5.1 <u>Case outline</u>. The case outline shall be as shown in 1.2.2 and figure 1.

- 3.5.2 Terminal connections. The terminal connections shall be as shown in figure 2.

- 3.5.3 <u>Terminal function description</u>. The Terminal function description shall be as shown in figure 3.

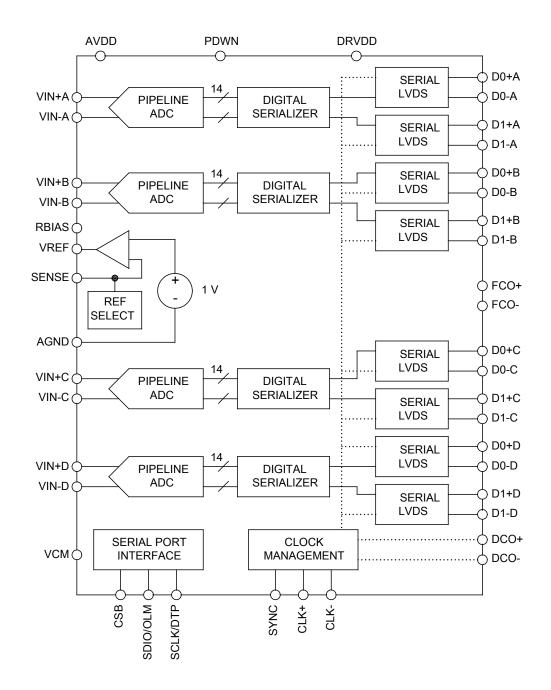

- 3.5.4 Functional block diagram. The functional block diagram shall be as shown in figure 4.

| DLA LAND AND MARITIME | SIZE | CODE IDENT NO. | DWG NO.          |  |  |

|-----------------------|------|----------------|------------------|--|--|

| COLUMBUS, OHIO        | A    | <b>16236</b>   | <b>V62/13627</b> |  |  |

|                       |      | REV            | PAGE 4           |  |  |

TABLE I. Electrical performance characteristics. 1/

| Test <u>2</u> /                                                             | Test conditions | Temp | Limits   |          |      | Unit   |

|-----------------------------------------------------------------------------|-----------------|------|----------|----------|------|--------|

|                                                                             | <u>3</u> /      |      | Min      | Тур      | Max  |        |

| DO                                                                          | SPECIFICATIONS  | _    |          |          |      |        |

| Resolution                                                                  |                 |      | 14       |          |      | Bits   |

| Accuracy                                                                    |                 | _    |          |          |      |        |

| No missing codes                                                            |                 | Full | G        | uarantee | d    |        |

| Offset error                                                                |                 | Full | -0.8     | -0.3     | +0.1 | % FSR  |

| Offset matching                                                             |                 | Full | -0.6     | +0.2     | +0.6 | % FSF  |

| Gain error                                                                  |                 | Full | -12      | -3       | +2   | % FSF  |

| Gain matching                                                               |                 | Full |          | 1.1      | 1.6  | % FSF  |

| Differential Nonlinearity (DNL)                                             |                 | Full | -0.8     |          | +1.9 | LSB    |

| Differential Norminearity (DNE)                                             |                 | 25°C |          | ±0.8     |      | LSB    |

| Integral Nonlinearity (INL)                                                 |                 | Full | -4.5     |          | +4.5 | LSB    |

| mogramonimeanty (mic)                                                       |                 | 25°C |          | ±2.0     |      | LSB    |

| Temperature drift                                                           |                 |      |          |          |      |        |

| Offset error                                                                |                 | Full |          | ±2       |      | ppm/°C |

| Gain error                                                                  |                 | Full |          | ±50      |      | ppm/°C |

| Internal voltage reference                                                  |                 |      |          |          |      |        |

| Output voltage (1 V Mode)                                                   |                 | Full | 0.98     | 1.0      | 1.02 | V      |

| Load regulation at 1.0 mA (V <sub>REF</sub> = 1 V)                          |                 | Full | 0.00     | 2        |      | mV     |

| Input resistance                                                            |                 | Full |          | 7.5      |      | kΩ     |

| Input referred noise                                                        |                 |      |          | 1 10     |      | 1      |

| V <sub>REF</sub> = 1.0 V                                                    |                 | 25°C |          | 0.94     |      | LSB rm |

| Analog inputs                                                               |                 |      |          |          |      |        |

| Differential input voltage (V <sub>REF</sub> = 1 V)                         |                 | Full |          | 2        |      | V p-p  |

| Common mode voltage                                                         |                 | Full |          | 0.9      |      | V      |

| Differential input resistance                                               |                 |      |          | 5.2      |      | kΩ     |

| Differential input capacitance                                              |                 | Full |          | 3.5      |      | pF     |

| Power supply                                                                |                 |      | ı        | 1 0.0    |      | J 6.   |

| AVDD                                                                        |                 | Full | 1.7      | 1.8      | 1.9  | V      |

| DRVDD                                                                       |                 | Full | 1.7      | 1.8      | 1.9  | V      |

| I <sub>AVDD</sub> <u>4</u> /                                                |                 | Full |          | 183      | 205  | mA     |

| I <sub>DRVDD</sub> (ANSI-644 mode) <u>4</u> /                               |                 | Full |          | 61       | 63   | mA     |

| I <sub>DRVDD</sub> (Reduce range mode) 4/                                   |                 | 25°C |          | 53       |      | mA     |

| Total power consumption                                                     |                 |      | <u> </u> |          | 1    |        |

| DC input                                                                    |                 | Full |          | 403      |      | mW     |

| Sine wave input (Four channels including output drivers ANSI 644 mode)      |                 | Full |          | 440      | 480  | mW     |

| Sine wave input (Four channels including output drivers reduced range mode) |                 | 25°C |          | 425      |      | mW     |

| Power down mode                                                             |                 | Full |          | 2        |      | mW     |

| Standby mode 5/                                                             |                 | Full |          | 235      |      | mW     |

| DLA LAND AND MARITIME | SIZE | CODE IDENT NO. | DWG NO.          |  |

|-----------------------|------|----------------|------------------|--|

| COLUMBUS, OHIO        | A    | <b>16236</b>   | <b>V62/13627</b> |  |

|                       |      | REV            | PAGE 5           |  |

TABLE I.  $\underline{\text{Electrical performance characteristics}}$  - Continued.  $\underline{1}/$

| Test <u>2</u> /                                          | Test conditions      | Temp |      | Limits |     | Unit     |

|----------------------------------------------------------|----------------------|------|------|--------|-----|----------|

|                                                          | <u>3</u> /           |      | Min  | Тур    | Max |          |

|                                                          | AC SPECIFICATIONS    |      |      |        |     |          |

| Signal to Noise Ratio (SNR)                              |                      |      |      | 75.0   |     | IDEO     |

| f <sub>IN</sub> = 9.7 MHz                                |                      | 25°C |      | 75.3   |     | dBFS     |

| f <sub>IN</sub> = 30.5 MHz                               |                      | 25°C |      | 75.2   |     |          |

| f <sub>IN</sub> = 70 MHz                                 |                      | Full | 72   | 74.1   |     | _        |

| f <sub>IN</sub> = 140 MHz                                |                      | 25°C |      | 72.2   |     | _        |

| f <sub>IN</sub> = 200 MHz                                |                      | 25°C |      | 70.7   |     |          |

| Signal to Noise And Distortion ratio (SINAD)             |                      | 0500 |      | 75.0   |     | 4DEC     |

| f <sub>IN</sub> = 9.7 MHz                                |                      | 25°C |      | 75.2   |     | dBFS     |

| f <sub>IN</sub> = 30.5 MHz                               |                      | 25°C |      | 75.1   |     |          |

| f <sub>IN</sub> = 70 MHz                                 |                      | Full | 71.7 | 74.0   |     | _        |

| f <sub>IN</sub> = 140 MHz                                |                      | 25°C |      | 71.9   |     | <u> </u> |

| f <sub>IN</sub> = 200 MHz                                |                      | 25°C |      | 70.4   |     |          |

| Effective Number Of Bits (ENOB)                          |                      | 1    |      | 400    | 1   |          |

| $f_{IN} = 9.7 \text{ MHz}$                               |                      | 25°C |      | 12.2   |     | Bits     |

| f <sub>IN</sub> = 30.5 MHz                               |                      | 25°C |      | 12.2   |     |          |

| f <sub>IN</sub> = 70 MHz                                 |                      | Full |      | 12.0   |     |          |

| f <sub>IN</sub> = 140 MHz                                |                      | 25°C |      | 11.7   |     |          |

| f <sub>IN</sub> = 200 MHz                                |                      | 25°C |      | 11.4   |     |          |

| Spurious Free Dynamic Range (SFDR)                       |                      |      |      | T      | 1   | 1        |

| $f_{IN} = 9.7 \text{ MHz}$                               |                      | 25°C |      | 98     |     | dBc      |

| $f_{IN} = 30.5 \text{ MHz}$                              |                      | 25°C |      | 92     |     |          |

| $f_{IN} = 70 \text{ MHz}$                                |                      | Full | 76   | 90     |     |          |

| $f_{IN} = 140 \text{ MHz}$                               |                      | 25°C |      | 85     |     |          |

| $f_{IN} = 200 \text{ MHz}$                               |                      | 25°C |      | 83     |     |          |

| Worst Harmonic (Second or Third)                         |                      |      |      |        |     |          |

| $f_{IN} = 9.7 \text{ MHz}$                               |                      | 25°C |      | -98    |     | dBc      |

| $f_{IN} = 30.5 \text{ MHz}$                              |                      | 25°C |      | -92    |     |          |

| $f_{IN} = 70 \text{ MHz}$                                |                      | Full |      | -90    | -76 |          |

| $f_{IN} = 140 \text{ MHz}$                               |                      | 25°C |      | -85    |     |          |

| f <sub>IN</sub> = 200 MHz                                |                      | 25°C |      | -83    |     |          |

| Worst other Harmonic (Excluding Second or Th             | ird)                 |      | •    |        |     |          |

| $f_{IN} = 9.7 \text{ MHz}$                               |                      | 25°C |      | -101   |     | dBFS     |

| f <sub>IN</sub> = 30.5 MHz                               |                      | 25°C |      | -100   |     |          |

| f <sub>IN</sub> = 70 MHz                                 |                      | Full |      | -95    | -83 |          |

| f <sub>IN</sub> = 140 MHz                                |                      | 25°C |      | -96    |     |          |

| f <sub>IN</sub> = 200 MHz                                |                      | 25°C |      | -92    |     |          |

| Two tone Intermodulation Distortion (IMD) -AN1           | and AND2 = -7.0 dBFS | •    | •    |        |     | •        |

| $f_{IN1} = 70.5 \text{ MHz}, f_{IN2} = 72.5 \text{ MHz}$ |                      | 25°C |      | 86     |     | dBc      |

| Crosstalk 6/                                             |                      | Full |      | -95    |     | dB       |

| Crosstalk (Overrange condition) 7/                       |                      | 25°C |      | -89    |     | dB       |

| Power Supply Rejection Ratio (SPRR) 8/                   | •                    | •    | •    |        | •   | •        |

| AVDD                                                     |                      | 25°C |      | 48     |     | dB       |

| DRVDD                                                    |                      | 25°C |      | 75     |     | dB       |

| Analog input bandwidth, Full power                       |                      | 25°C |      | 650    |     | MHz      |

| See footnote at end of table                             | •                    |      |      | •      |     |          |

| DLA LAND AND MARITIME | SIZE | CODE IDENT NO. | DWG NO.          |

|-----------------------|------|----------------|------------------|

| COLUMBUS, OHIO        | A    | <b>16236</b>   | <b>V62/13627</b> |

|                       |      | REV            | PAGE 6           |

TABLE I. <u>Electrical performance characteristics</u> - Continued. <u>1</u>/

| Test <u>2</u> /                                | Test conditions           | Temp     |            | Limits   |            | Unit  |

|------------------------------------------------|---------------------------|----------|------------|----------|------------|-------|

|                                                | <u>3</u> /                |          | Min        | Тур      | Max        |       |

|                                                | DIGITAL SPECIF            | ICATIONS |            |          |            |       |

| Clock inputs (CLK+, CLK-)                      |                           |          | T.         |          |            |       |

| Logic compliance                               |                           |          | CMOS       | S/LVDS/L | VPECL      |       |

| Differential input voltage 9/                  |                           | Full     | 0.2        |          | 3.6        | V p-p |

| Input voltage range                            |                           | Full     | AGND - 0.2 |          | AGND + 0.2 | V     |

| Input common mode voltage                      |                           | Full     |            | 0.9      |            | V     |

| Input resistance (Differential)                |                           | 25°C     |            | 15       |            | kΩ    |

| Input capacitance                              |                           | 25°C     |            | 4        |            | pF    |

| Logic inputs (PDWN, SYNC, SCLK)                |                           |          |            |          |            |       |

| Logic 1 voltage                                |                           | Full     | 1.2        |          | AVDD + 0.2 | V     |

| Logic 0 voltage                                |                           | Full     | 0          |          | 0.8        | V     |

| Input resistance                               |                           | 25°C     |            | 30       |            | kΩ    |

| Input capacitance                              |                           | 25°C     |            | 2        |            | pF    |

| Logic input (CSB)                              |                           |          |            |          |            |       |

| Logic 1 voltage                                |                           | Full     | 1.2        |          | AVDD + 0.2 | V     |

| Logic 0 voltage                                |                           | Full     | 0          |          | 0.8        | V     |

| Input resistance                               |                           | 25°C     |            | 26       |            | kΩ    |

| Input capacitance                              |                           | 25°C     |            | 2        |            | pF    |

| Logic input (SDIO/OLM)                         |                           |          |            |          |            |       |

| Logic 1 voltage                                |                           | Full     | 1.2        |          | AVDD + 0.2 | V     |

| Logic 0 voltage                                |                           | Full     | 0          |          | 0.8        | V     |

| Input resistance                               |                           | 25°C     |            | 26       |            | kΩ    |

| Input capacitance                              |                           | 25°C     |            | 5        |            | pF    |

| Logic output (SDIO/OLM) 10/                    |                           |          |            |          |            |       |

| Logic 1 voltage ( $I_{OH} = 800 \mu A$ )       |                           | Full     |            | 1.79     |            | V     |

| Logic 0 voltage (I <sub>OL</sub> = 50 μA)      |                           | Full     |            |          | 0.05       | V     |

| Digital outputs (D0±x, D1±x), ANSI-644         | 1                         |          |            |          |            |       |

| Logic compliance                               |                           |          |            | LVDS     |            |       |

| Differential output voltage (V <sub>OD</sub> ) |                           | Full     | 290        | 345      | 400        | mV    |

| Output offset voltage (Vos)                    |                           | Full     | 1.15       | 1.25     | 1.35       | V     |

| Output coding (Default)                        |                           |          | Two        | s comple | ment       |       |

| Digital outputs (D0±x, D1±x), low power        | er, reduced signal option | 1        | 1          |          |            |       |

| Logic compliance                               |                           |          |            | LVDS     | T          |       |

| Differential output voltage (V <sub>OD</sub> ) |                           | Full     | 160        | 200      | 230        | mV    |

| Output offset voltage (Vos)                    |                           | Full     | 1.15       | 1.25     | 1.35       | V     |

| Output coding (Default)                        |                           |          | Two        | s comple | ment       |       |

| DLA LAND AND MARITIME | SIZE | CODE IDENT NO. | DWG NO. <b>V62/13627</b> |

|-----------------------|------|----------------|--------------------------|

| COLUMBUS, OHIO        | A    | <b>16236</b>   |                          |

|                       |      | REV            | PAGE 7                   |

TABLE I. <u>Electrical performance characteristics</u> - Continued. <u>1</u>/

| Test <u>2</u> / <u>11</u> /                           | Test conditions | Temp     |                                 | Limits                                       |                         | Unit            |

|-------------------------------------------------------|-----------------|----------|---------------------------------|----------------------------------------------|-------------------------|-----------------|

|                                                       | <u>3</u> /      |          | Min                             | Тур                                          | Max                     |                 |

|                                                       | SWITCHI         | NG SPECI | FICATIONS                       |                                              |                         |                 |

| Clock                                                 |                 |          |                                 |                                              |                         |                 |

| Input clock rate                                      |                 | Full     | 10                              |                                              | 1000                    | MHz             |

| Conversion rate                                       |                 | Full     | 10                              |                                              | 125                     | MSPS            |

| Clock Pulse Width High (t <sub>EH</sub> )             |                 | Full     |                                 | 4.00                                         |                         | ns              |

| Clock Pulse Width Low (t <sub>EL</sub> )              |                 | Full     |                                 | 4.00                                         |                         | ns              |

| Output parameters <u>12</u> /                         |                 |          |                                 |                                              |                         |                 |

| Propagation Delay (tpb)                               |                 | Full     |                                 | 2.3                                          |                         | ns              |

| Rise Time (t <sub>R</sub> ) (20% to 80%)              |                 | Full     |                                 | 300                                          |                         | ps              |

| Fall Time (t <sub>F</sub> ) (20% to 80%)              |                 | Full     |                                 | 300                                          |                         | ps              |

| FCO Propagation Delay (trco)                          |                 | Full     | 1.5                             | 2.3                                          | 3.1                     | ns              |

| DCO Propagation Delay (t <sub>CPD</sub> ) <u>13</u> / |                 | Full     |                                 | t <sub>FCO</sub> + (t <sub>SAMPLE</sub> /16) |                         | ns              |

| DCO-to-Data Delay (t <sub>DATA</sub> ) <u>13</u> /    |                 | Full     | (t <sub>SAMPLE</sub> /16) - 300 | (t <sub>SAMPLE</sub> /16)                    | $(t_{SAMPLE}/16) + 300$ | ops             |

| DCO-to-FCO Delay (t <sub>FRAME</sub> ) <u>13</u> /    |                 | Full     | (t <sub>SAMPLE</sub> /16) - 300 | (t <sub>SAMPLE</sub> /16)                    | $(t_{SAMPLE}/16) + 300$ | ps              |

| Lane Delay (tld)                                      |                 |          |                                 | 90                                           |                         | ps              |

| Data to Data Skew (tdata-max - tdata-min)             |                 | Full     |                                 | ±50                                          | ±200                    | ps              |

| Wake-Up Time (Standby)                                |                 | 25°C     |                                 | 250                                          |                         | ns              |

| Wake-Up Time (Power-Down) 14/                         |                 | 25°C     |                                 | 375                                          |                         | μs              |

| Pipeline Latency                                      |                 | Full     |                                 | 16                                           |                         | Clock<br>cycles |

| Aperture                                              |                 |          |                                 |                                              |                         |                 |

| Aperture Delay (t <sub>A</sub> )                      |                 | 25°C     |                                 | 1                                            |                         | ns              |

| Aperture Uncertainty (Jitter, t <sub>J</sub> )        |                 | 25°C     |                                 | 135                                          |                         | fs ms           |

| Out-of-Range Recovery Time                            |                 | 25°C     |                                 | 1                                            |                         | Clock<br>cycles |

| DLA LAND AND MARITIME | SIZE | CODE IDENT NO. | DWG NO.          |  |

|-----------------------|------|----------------|------------------|--|

| COLUMBUS, OHIO        | A    | <b>16236</b>   | <b>V62/13627</b> |  |

|                       |      | REV            | PAGE 8           |  |

### TABLE I. Electrical performance characteristics - Continued. 1/

- 1/ Testing and other quality control techniques are used to the extent deemed necessary to assure product performance over the specified temperature range. Product may not necessarily be tested across the full temperature range and all parameters may not necessarily be tested. In the absence of specific parametric testing, product performance is assured by characterization and/or design.

- See the AN-835 manufacturer's application note. Understanding high speed ADC testing and evaluation, for definitions and for details on how these tests were completed.

- 3/ AVDD = 1.8 V, DRVDD = 1.8 V, 2 V p-p differential input, 1.0 V internal reference, AIN = -1.0 dBFS, unless otherwise noted.

- 4/ Measured with a low input frequency, full scale sine wave of all four channels.

- 5/ It can be controlled via the SPI.

- 6/ Crosstalk is measured at 70 MHz with an -1.0 dBFS analog input on one channel and no input on the adjacent channel.

- 7/ The over range condition is specified with 3 dB of the full-scale input range.

- 8/ PSRR is measured by injecting a sinusoidal signal at 10 MHz to the power supply pin and measuring the output spur on the FFT. PSRR is calculated as the ratio of the amplitudes of the spur voltage over the pin voltage, expressed in decibels.

- 9/ This is specified for LVDS and LVPECL only.

- 10/ This is specified for 13 SDIO/OLM pins sharing the same connection.

- 11/ Measured on standard FR-4 material.

- 12/ Can be adjusted via the SPI. The conversion rate is the clock rate after the divider.

- $\frac{13}{t_{SAMPLE}}$  to is based on the number of bits in two LVDS data lanes.  $t_{SAMPLE} = 1/f_{S}$ .

- 14/ Wake-up time is defined as the time required to return to normal operation from power-down mode.

| DLA LAND AND MARITIME | SIZE | CODE IDENT NO. | DWG NO.          |

|-----------------------|------|----------------|------------------|

| COLUMBUS, OHIO        | A    | <b>16236</b>   | <b>V62/13627</b> |

|                       |      | REV            | PAGE 9           |

| Dimensions |             |      |        |       |        |

|------------|-------------|------|--------|-------|--------|

| Symbol     | Millimeters |      | Symbol | Milli | meters |

|            | Min         | Max  |        | Min   | Max    |

| Α          | 0.70        | 0.80 | D1/E1  | 5.55  | 5.65   |

| A1         |             | 0.05 | е      | 0.50  | ) BSC  |

| A2         | 0.20        | REF  | S      | 0.35  | 0.45   |

| b          | 0.18        | 0.30 | S1     | 0.20  |        |

| D/E        | 6.90        | 7.10 |        |       | _      |

# NOTES:

- All linear dimensions are in millimeters.

Falls within JEDEC STANDARDS MO-220-WKKD.

FIGURE 1. Case outline.

| DLA LAND AND MARITIME | SIZE | CODE IDENT NO. | DWG NO.          |

|-----------------------|------|----------------|------------------|

| COLUMBUS, OHIO        | A    | <b>16236</b>   | <b>V62/13627</b> |

|                       |      | REV            | PAGE 10          |

## Case outline X

| Terminal number | Terminal symbol | Terminal<br>number | Terminal symbol |

|-----------------|-----------------|--------------------|-----------------|

| 1               | VIN+D           | 48                 | VIN+C           |

| 2               | VIN-D           | 47                 | VIN-C           |

| 3               | AVDD            | 46                 | AVDD            |

| 4               | AVDD            | 45                 | AVDD            |

| 5               | CLK-            | 44                 | SYNC            |

| 6               | CLK+            | 43                 | VCM             |

| 7               | AVDD            | 42                 | VREF            |

| 8               | DRVDD           | 41                 | SENSE           |

| 9               | D1-D            | 40                 | RBIAS           |

| 10              | D1+D            | 39                 | AVDD            |

| 11              | D0-D            | 38                 | VIN-B           |

| 12              | D0+D            | 37                 | VIN+B           |

| 13              | D1-C            | 36                 | VIN+A           |

| 14              | D1+C            | 35                 | VIN-A           |

| 15              | D0-C            | 34                 | AVDD            |

| 16              | D0+C            | 33                 | PDWN            |

| 17              | DCO-            | 32                 | CSB             |

| 18              | DCO+            | 31                 | SDIO/OLM        |

| 19              | FCO-            | 30                 | SCLK/DTP        |

| 20              | FCO+            | 29                 | DRVDD           |

| 21              | D1-B            | 28                 | D0+A            |

| 22              | D1+B            | 27                 | D0-A            |

| 23              | D0-B            | 26                 | D1+A            |

| 24              | D0+B            | 25                 | D1-A            |

# NOTE:

The exposed thermal PAD on the bottom of the package provides the analog ground for the part, this exposed PAD must be connected to ground for proper operation.

FIGURE 2. <u>Terminal connections</u>

| DLA LAND AND MARITIME | SIZE | CODE IDENT NO. | DWG NO.          |  |

|-----------------------|------|----------------|------------------|--|

| COLUMBUS, OHIO        | A    | <b>16236</b>   | <b>V62/13627</b> |  |

|                       |      | REV            | PAGE 11          |  |

# Case outline X

| Pin No.                    | Mnemonic    | Description                                                                                    |

|----------------------------|-------------|------------------------------------------------------------------------------------------------|

| 0                          | AGND,       | Analog Ground, Exposed Pad. The exposed thermal pad on the bottom of the package provides the  |

| 0                          | Exposed Pad | analog ground for the part. This exposed pad must be connected to ground for proper operation. |

| 1                          | VIN+D       | ADC D Analog Input True.                                                                       |

| 2                          | VIN-D       | ADC D Analog Input Complement.                                                                 |

| 3, 4, 7, 34,<br>39, 45, 46 | AVDD        | 1.8 V Analog Supply Pins.                                                                      |

| 5, 6                       | CLK-, CLK+  | Differential Encode Clock. PECL, LVDS, or 1.8 V CMOS inputs.                                   |

| 8, 29                      | DRVDD       | Digital Output Driver Supply.                                                                  |

| 9                          | D1-D        | Channel D Digital Output 1 Complement.                                                         |

| 10                         | D1+D        | Channel D Digital Output 1 True.                                                               |

| 11                         | D0-D        | Channel D Digital Output 0 Complement.                                                         |

| 12                         | D0+D        | Channel D Digital Output 0 True.                                                               |

| 13                         | D1-C        | Channel C Digital Output 1 Complement.                                                         |

| 14                         | D1+C        | Channel C Digital Output 1 True.                                                               |

| 15                         | D0-C        | Channel C Digital Output 0 Complement.                                                         |

| 16                         | D0+C        | Channel C Digital Output 0 True.                                                               |

| 17                         | DCO-        | Data Clock Output Complement.                                                                  |

| 18                         | DCO+        | Data Clock Output True.                                                                        |

| 19                         | FCO-        | Frame Clock Output Complement.                                                                 |

| 20                         | FCO+        | Frame Clock Output True.                                                                       |

| 21                         | D1-B        | Channel B Digital Output 1 Complement.                                                         |

| 22                         | D1+B        | Channel B Digital Output 1 True.                                                               |

| 23                         | D0-B        | Channel B Digital Output 0 Complement.                                                         |

| 24                         | D0+B        | Channel B Digital Output 0 True.                                                               |

| 25                         | D1-A        | Channel A Digital Output 1 Complement.                                                         |

| 26                         | D1+A        | Channel A Digital Output 1 True.                                                               |

| 27                         | D0-A        | Channel A Digital Output 0 Complement.                                                         |

| 28                         | D0+A        | Channel A Digital Output 0 True.                                                               |

| 30                         | SCLK/DTP    | SPI Clock Input/Digital Test Pattern.                                                          |

| 31                         | SDIO/OLM    | SPI Data Input and Output Bidirectional SPI Data/Output Lane Mode.                             |

| 32                         | CSB         | SPI Chip Select Bar. Active low enable; 30 kΩ internal pull-up.                                |

|                            |             | Digital Input, 30 kΩ Internal Pull-Down.                                                       |

| 33                         | PDWN        | PDWN high = power-down device.                                                                 |

|                            |             | PDWN low = run device, normal operation.                                                       |

| 35                         | VIN-A       | ADC A Analog Input Complement.                                                                 |

| 36                         | VIN+A       | ADC A Analog Input True.                                                                       |

| 37                         | VIN+B       | ADC B Analog Input True.                                                                       |

| 38                         | VIN-B       | ADC B Analog Input Complement.                                                                 |

| 40                         | RBIAS       | Sets Analog Current Bias. Connect to 10 kΩ (1% tolerance) resistor to ground.                  |

| 41                         | SENSE       | Reference Mode Selection.                                                                      |

| 42                         | VREF        | Voltage Reference Input and Output.                                                            |

| 43                         | VCM         | Analog Input Common-Mode Voltage.                                                              |

| 44                         | SYNC        | Digital Input. SYNC input to clock divider.                                                    |

| 47                         | VIN-C       | ADC C Analog Input Complement.                                                                 |

| 48                         | VIN+C       | ADC C Analog Input True.                                                                       |

FIGURE 3. Terminal function description.

| DLA LAND AND MARITIME | SIZE | CODE IDENT NO. | DWG NO.          |

|-----------------------|------|----------------|------------------|

| COLUMBUS, OHIO        | A    | <b>16236</b>   | <b>V62/13627</b> |

|                       |      | REV            | PAGE 12          |

FIGURE 4. Functional block diagram.

| DLA LAND AND MARITIME | SIZE | CODE IDENT NO. | DWG NO.          |

|-----------------------|------|----------------|------------------|

| COLUMBUS, OHIO        | A    | <b>16236</b>   | <b>V62/13627</b> |

|                       |      | REV            | PAGE 13          |

#### 4. VERIFICATION

4.1 <u>Product assurance requirements</u>. The manufacturer is responsible for performing all inspection and test requirements as indicated in their internal documentation. Such procedures should include proper handling of electrostatic sensitive devices, classification, packaging, and labeling of moisture sensitive devices, as applicable.

## 5. PREPARATION FOR DELIVERY

5.1 <u>Packaging</u>. Preservation, packaging, labeling, and marking shall be in accordance with the manufacturer's standard commercial practices for electrostatic discharge sensitive devices.

### 6. NOTES

- 6.1 ESDS. Devices are electrostatic discharge sensitive and are classified as ESDS class 1 minimum.

- 6.2 <u>Configuration control</u>. The data contained herein is based on the salient characteristics of the device manufacturer's data book. The device manufacturer reserves the right to make changes without notice. This drawing will be modified as changes are provided.

- 6.3 <u>Suggested source(s) of supply</u>. Identification of the suggested source(s) of supply herein is not to be construed as a guarantee of present or continued availability as a source of supply for the item. DLA Land and Maritime maintains an online database of all current sources of supply at <a href="http://www.landandmaritime.dla.mil/Programs/Smcr/">http://www.landandmaritime.dla.mil/Programs/Smcr/</a>.

| Vendor item drawing administrative control number 1/ | Device<br>manufacturer<br>CAGE code | Transport media | Vendor part number |

|------------------------------------------------------|-------------------------------------|-----------------|--------------------|

| V00/40007.04VF                                       |                                     | Tray, 260       | AD9253TCPZ-125EP   |

| V62/13627-01XE                                       | 24355                               | Tape and reel   | AD9253TCPZR7-125EP |

1/ The vendor item drawing establishes an administrative control number for identifying the item on the engineering documentation.

<u>CAGE code</u> <u>Source of supply</u>

24355 Analog Devices 1 Technology Way P.O. Box 9106

Norwood, MA 02062-9106

| DLA LAND AND MARITIME | SIZE | CODE IDENT NO. | DWG NO.          |

|-----------------------|------|----------------|------------------|

| COLUMBUS, OHIO        | A    | <b>16236</b>   | <b>V62/13627</b> |

|                       |      | REV            | PAGE 14          |