|                                |                             |          |           | LTR             | 2                |                       |                         |           | DESC    | RIPTI  | ON            |                                |               |                   | D                                    | ATE                                    |                          |                                | APPR        | OVED          | )   |

|--------------------------------|-----------------------------|----------|-----------|-----------------|------------------|-----------------------|-------------------------|-----------|---------|--------|---------------|--------------------------------|---------------|-------------------|--------------------------------------|----------------------------------------|--------------------------|--------------------------------|-------------|---------------|-----|

|                                |                             |          |           | Α               |                  | Char                  | nge in                  | Table     | I for n | ew re- | desigr        | ı PH                           | N             |                   | 13-03-12                             |                                        |                          | Tł                             | nomas       | М. Не         | ess |

|                                |                             |          |           |                 |                  |                       |                         |           |         |        |               |                                |               |                   |                                      |                                        |                          |                                |             |               |     |

|                                |                             |          |           |                 |                  |                       |                         |           |         |        |               |                                |               |                   |                                      |                                        |                          |                                |             |               |     |

| ì                              |                             |          |           |                 |                  |                       |                         |           |         |        |               |                                |               |                   |                                      |                                        |                          |                                |             |               |     |

| Ì                              |                             |          |           |                 |                  |                       |                         |           |         |        |               |                                |               |                   |                                      |                                        |                          |                                |             |               |     |

| Ì                              |                             |          |           |                 |                  |                       |                         |           |         |        |               |                                |               |                   |                                      |                                        |                          |                                |             |               |     |

|                                |                             |          |           |                 |                  |                       |                         |           |         |        |               |                                |               |                   |                                      |                                        |                          |                                |             |               |     |

|                                |                             |          |           |                 |                  |                       |                         |           |         |        |               |                                |               |                   |                                      |                                        |                          |                                |             |               |     |

|                                |                             |          |           |                 |                  |                       |                         |           |         |        |               |                                |               |                   |                                      |                                        |                          |                                |             |               |     |

|                                |                             |          |           |                 |                  |                       |                         |           |         |        |               |                                |               |                   |                                      |                                        |                          |                                |             |               |     |

|                                |                             |          |           |                 |                  |                       |                         |           |         |        |               |                                |               |                   |                                      |                                        |                          |                                |             |               |     |

|                                |                             |          |           |                 |                  |                       |                         |           |         |        |               |                                |               |                   |                                      |                                        |                          |                                |             |               |     |

|                                |                             |          |           |                 |                  |                       |                         |           |         |        |               |                                |               |                   |                                      |                                        |                          |                                |             |               |     |

|                                |                             |          |           |                 |                  |                       |                         |           |         |        |               |                                |               |                   |                                      |                                        |                          |                                |             |               |     |

|                                |                             |          |           |                 |                  |                       |                         |           |         |        |               |                                |               |                   |                                      |                                        |                          |                                |             |               |     |

|                                |                             |          |           |                 |                  |                       |                         |           |         |        |               |                                |               |                   |                                      |                                        |                          |                                |             |               |     |

|                                |                             |          |           |                 |                  |                       |                         |           |         |        |               |                                |               |                   |                                      |                                        |                          |                                |             |               |     |

|                                |                             |          |           |                 |                  |                       |                         |           |         |        |               |                                |               |                   |                                      |                                        |                          |                                |             |               |     |

|                                |                             |          |           |                 |                  |                       |                         |           |         |        |               |                                |               |                   |                                      |                                        |                          |                                |             |               |     |

|                                |                             |          |           |                 |                  |                       |                         |           |         |        |               |                                |               |                   |                                      |                                        |                          |                                |             |               |     |

| Prepared                       | in accord                   | ance wit | h ASM     | E Y14.          | 24               |                       |                         |           |         |        |               |                                |               |                   |                                      |                                        |                          |                                |             |               |     |

|                                |                             |          |           |                 |                  |                       |                         |           |         |        |               |                                |               |                   |                                      |                                        | Ve                       | endor                          | item d      | rawing        | )   |

| REV                            |                             |          |           |                 |                  |                       |                         |           |         |        |               |                                |               |                   |                                      |                                        | Ve                       | endor                          | item d      | rawing        | )   |

| PAGE                           | 1                           |          |           |                 |                  |                       |                         |           |         |        |               |                                |               |                   |                                      |                                        | Ve                       | endor                          | item d      | rawing        | )   |

| REV                            |                             |          |           |                 |                  |                       |                         |           |         |        |               |                                |               |                   |                                      |                                        | Ve                       | endor                          | item d      | rawing        | )   |

|                                |                             |          |           |                 |                  |                       |                         |           |         |        |               |                                |               |                   |                                      |                                        | Ve                       | endor                          | item d      | rawing        |     |

| PAGE                           |                             |          |           |                 |                  |                       |                         |           |         |        |               |                                |               |                   |                                      |                                        | Ve                       | endor                          | item d      | rawing        |     |

| REV STA                        |                             | REV      |           |                 | A                | A                     | A                       | A         | A       | A      | A             | A                              | A             | A                 | A                                    | A                                      | Ve                       | endor                          | item d      | rawing        | 3   |

|                                |                             | REV      |           |                 | A 1              | A 2                   | A 3                     | A 4       | A 5     | A 6    | A 7           | A 8                            | A 9           | A 10              | A 11                                 | A 12                                   |                          | endor                          | item d      | rawing        |     |

| REV STA                        | ES                          |          | SE I      | PARED           | 1<br>BY          | 2                     | 3                       | 4         |         |        |               |                                | 9<br><b>D</b> | 10<br><b>LA L</b> | 11<br><b>AND</b>                     | 12<br><b>ANE</b>                       | A 13                     | RITII                          | ME          |               | )   |

| REV STA<br>OF PAGE             | ES                          |          | SE I      |                 | 1<br>BY          | 2                     |                         | 4         |         |        |               |                                | 9<br><b>D</b> | 10<br><b>LA L</b> | 11<br><b>AND</b>                     | 12<br><b>ANE</b>                       | A 13                     | RITII                          |             |               | }   |

| REV STA<br>OF PAGE<br>PMIC N/A | A late of dra               | PAG      | PREF      |                 | 1<br>BY<br>P     | 2<br>Phu H.           | 3<br>Nguy               | 4<br>en   |         |        | 7 <b>TIT</b>  | 8<br>L <b>E</b>                | 9<br>COI      | 10<br>LA L<br>UMI | AND<br>BUS,                          | ANE<br>OHIO                            | A<br>13<br>D MA<br>O 43  | RITII<br>3218-                 | ME<br>-3990 |               | 3   |

| PMIC N/A                       | A<br>late of dra<br>Y MM DD | PAG      | PREF      | PARED<br>CKED I | 1<br>P<br>BY     | 2<br>Phu H.<br>Phu H. | 3                       | 4<br>en   |         |        | 7 TIT         | 8<br>L <b>E</b>                | 9<br>COL      | 10 LA L UMI       | AND<br>BUS,                          | 12<br><b>ANE</b><br><b>OHI</b><br>ΓAL, | A 13 D MA O 43           | RITII<br>3218-                 | ME<br>-3990 | )<br>         | }   |

| PMIC N/A                       | A late of dra               | PAG      | PREF      | PARED           | 1 BY P           | 2<br>Phu H.<br>Phu H. | 3<br>Nguy               | 4<br>en   |         |        | 7 TIT         | 8<br>LE<br>CROC                | 9 COL         | JIT, I            | AND<br>BUS,                          | ANE<br>OHIO                            | A 13 D MA O 43 NON SITIC | RITII<br>3218-                 | ME<br>-3990 | )<br>LE<br>AL | )   |

| PMIC N/A                       | A<br>late of dra<br>Y MM DD | PAG      | PREF      | PARED<br>CKED I | 1 P BY P BY P Th | 2<br>Phu H.<br>Phu H. | Nguy<br>Nguy            | en<br>en  |         |        | TIT MIC ME PO | 8<br>LE<br>CROC<br>MOR<br>TENT | 9 COL         | JIT, I            | AND<br>BUS,                          | ANE<br>OHIO                            | A 13 D MA O 43 NON SITIC | RITII<br>3218-                 | ME<br>-3990 | )<br>LE<br>AL |     |

| PMIC N/A                       | A<br>late of dra<br>Y MM DD | PAG      | PREF      | PARED CKED I    | 1 P BY P BY P Th | 2<br>Phu H.<br>Phu H. | Nguy<br>Nguy<br>S M. He | en<br>en  |         |        | TIT MIC ME PO | 8<br>LE<br>CROC                | 9 COL         | JIT, I            | AND<br>BUS,<br>DIGIT<br>1024<br>R, M | ANE<br>OHIO                            | A 13 D MA O 43 NON SITIC | RITII<br>3218-<br>NVOL<br>DN D | ME<br>-3990 | )<br>LE<br>AL |     |

| PMIC N/A                       | A<br>late of dra<br>Y MM DD | PAG      | PREF CHEC | PARED CKED I    | 1 P BY P BY P Th | 2<br>Phu H.<br>Phu H. | Nguy Nguy M He          | en en ess |         |        | TIT           | 8<br>LE<br>CROC<br>MOR<br>TENT | D<br>COL      | JIT, I            | AND<br>BUS,<br>DIGIT<br>1024<br>R, M | TAL,                                   | A 13 D MA O 43 NON SITIC | RITII<br>3218-<br>NVOL<br>DN D | ME<br>-3990 | )<br>LE<br>AL | }   |

**REVISIONS**

AMSC N/A 5962-V054-13

#### 1. SCOPE

- 1.1 <u>Scope</u>. This drawing documents the general requirements of a high performance non volatile memory, dual 1024-position digital potentiometer microcircuit, with an operating temperature range of -40°C to +125°C.

- 1.2 <u>Vendor Item Drawing Administrative Control Number</u>. The manufacturer's PIN is the item of identification. The vendor item drawing establishes an administrative control number for identifying the item on the engineering documentation:

V62/11605

01

X

B

Drawing number

Device type (See 1.2.1)

Case outline (See 1.2.2)

Lead finish (See 1.2.3)

1.2.1 Device type(s).

Device typeGenericCircuit function01AD5235-EPNonvolatile memory, dual 1024-position digital potentiometer

1.2.2 <u>Case outline(s)</u>. The case outlines are as specified herein.

Outline letter

Number of pins

JEDEC PUB 95

Package style

X

16

JEDEC MO-153

Small outline Package

1.2.3 <u>Lead finishes</u>. The lead finishes are as specified below or other lead finishes as provided by the device manufacturer:

Finish designator

A Hot solder dip

B Tin-lead plate

C Gold plate

D Palladium

E Gold flash palladium

Z Other

| DLA LAND AND MARITIME | SIZE | CODE IDENT NO. | DWG NO.          |

|-----------------------|------|----------------|------------------|

| COLUMBUS, OHIO        | A    | <b>16236</b>   | <b>V62/11605</b> |

|                       |      | REV A          | PAGE 2           |

# 1.3 Absolute maximum ratings. 1/

Voltage referenced:

| voltage referenced.                                                    |                                                     |

|------------------------------------------------------------------------|-----------------------------------------------------|

| V <sub>DD</sub> to GND                                                 | -0.3 V to +7.0 V                                    |

| V <sub>SS</sub> to GND                                                 | +0.3 V to -7.0 V                                    |

| V <sub>DD</sub> to V <sub>SS</sub>                                     |                                                     |

| $V_A$ , $V_B$ , $V_W$ to GND                                           | $V_{SS} - 0.3 \text{ V to } V_{DD} + 0.3 \text{ V}$ |

| Current referenced, I <sub>A</sub> , I <sub>B</sub> , I <sub>W</sub> : |                                                     |

| Pulsed <u>2</u> /                                                      | ±2.5 mA                                             |

| Continuous                                                             | ±1.1 mA                                             |

| Digital input and output voltage to GND                                | $-0.3 \text{ V to V}_{DD} + 0.3 \text{ V}$          |

| Ambient operating temperature range 3/                                 | -40°C to +125°C                                     |

| Storage temperature range                                              | -65°C to +150°C                                     |

| Maximum junction temperature (T <sub>J</sub> )                         | 150°C                                               |

| Lead temperature, soldering:                                           |                                                     |

| Vapor phase (60 sec)                                                   | 215°C                                               |

| Infrared (15 sec)                                                      |                                                     |

| Thermal resistance, junction to ambient (θJA)                          | 150°C /W                                            |

| Thermal resistance, junction to case $(\theta_{JC})$                   | 28°C /W                                             |

|                                                                        |                                                     |

### 2. APPLICABLE DOCUMENTS

## JEDEC - SOLID STATE TECHNOLOGY ASSOCIATION (JEDEC)

JEP95 – Registered and Standard Outlines for Semiconductor Devices

Package power dissipation ...... (T<sub>J max</sub> – T<sub>A</sub>)/ θ<sub>JA</sub>

JESD22a117 – Electrical Erasable programmable ROM (EEPROM) Program/Erase endurance and data retention test.

JESD51-2a - Integrated Circuits Thermal Test Method Environment Conditions - Natural Convection (Still Air)

(Copies of these documents are available online at <a href="http://www.jedec.org">http://www.jedec.org</a> or from JEDEC – Solid State Technology Association, 3103 North 10th Street, Suite 240–S, Arlington, VA 22201-2107).

| DLA LAND AND MARITIME | SIZE | CODE IDENT NO. | DWG NO.          |

|-----------------------|------|----------------|------------------|

| COLUMBUS, OHIO        | A    | <b>16236</b>   | <b>V62/11605</b> |

|                       |      | REV A          | PAGE 3           |

Stresses beyond those listed under "absolute maximum ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated under "recommended operating conditions" is not implied. Exposure to absolute maximum rated conditions for extended periods may affect device reliability.

<sup>2/</sup> Maximum terminal current is bounded by the maximum current handling of the switches, maximum power dissipation of the package, and maximum applied voltage across any two of the A, B and W terminals at a given resistance.

<sup>3/</sup> Includes programming of nonvolatile memory.

### 3. REQUIREMENTS

- 3.1 <u>Marking</u>. Parts shall be permanently and legibly marked with the manufacturer's part number as shown in 6.3 herein and as follows:

- A. Manufacturer's name, CAGE code, or logo

- B. Pin 1 identifier

- C. ESDS identification (optional)

- 3.2 <u>Unit container</u>. The unit container shall be marked with the manufacturer's part number and with items A and C (if applicable) above.

- 3.3 <u>Electrical characteristics</u>. The maximum and recommended operating conditions and electrical performance characteristics are as specified in 1.3, 1.4, and table I herein.

- 3.4 Design, construction, and physical dimension. The design, construction, and physical dimensions are as specified herein.

- 3.5 Diagrams.

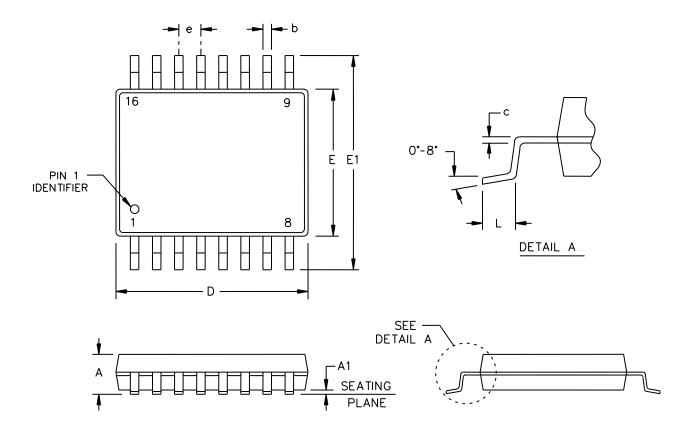

- 3.5.1 <u>Case outline</u>. The case outline shall be as shown in 1.2.2 and figure 1.

- 3.5.2 Terminal connections. The terminal connections shall be as shown in figure 2.

- 3.5.3 Terminal functions. The terminal functions shall be as shown in figure 3.

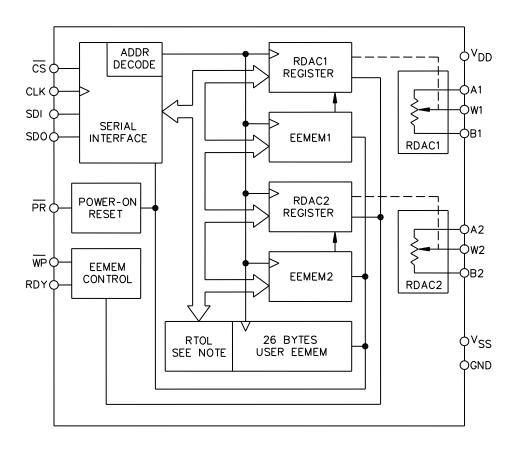

- 3.5.3 Functional block diagram. The functional block diagram shall be as shown in figure 4.

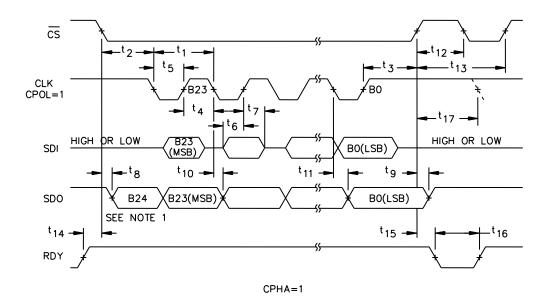

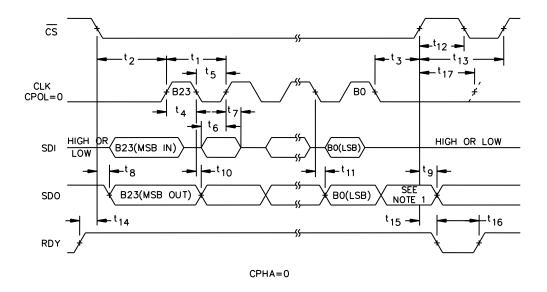

- 3.5.4 <u>Timing diagrams</u>. The timing diagrams shall be as shown in figure 5 and 6.

| DLA LAND AND MARITIME | SIZE | CODE IDENT NO. | DWG NO.          |

|-----------------------|------|----------------|------------------|

| COLUMBUS, OHIO        | A    | <b>16236</b>   | <b>V62/11605</b> |

|                       |      | REV A          | PAGE 4           |

TABLE I. Electrical performance characteristics. 1/

| Test                                          | Symbol                                                    | Test conditions                                                                    |     | Limits     |          | Unit   |

|-----------------------------------------------|-----------------------------------------------------------|------------------------------------------------------------------------------------|-----|------------|----------|--------|

|                                               |                                                           | <u>2</u> /                                                                         | Min | Тур        | Max      |        |

|                                               |                                                           | unless otherwise specified                                                         |     | <u>3</u> / |          |        |

| DC characteristic-RHEOSTAT mode               | (All RDACs)                                               |                                                                                    | 1   |            | Т        | 1      |

| Resistor differential nonlinearity <u>4</u> / | R-DNL                                                     | R <sub>WB</sub>                                                                    | -1  |            | +1       | LSB    |

| Resistor integral nonlinearity <u>4</u> /     | R-INL                                                     | R <sub>WB</sub>                                                                    | -2  |            | +2       | LSB    |

| Nominal resistor tolerance                    | $\Delta R_{AB}/R_{AB}$                                    | Code = full scale                                                                  | -8  |            | +8       | %      |

| Resistance temperature coefficient            | $(\Delta R_{AB}/R_{AB})\Delta Tx10^6$                     |                                                                                    |     | 35         |          | ppm/°C |

| Wipe resistance                               | R <sub>W</sub>                                            | $I_W = 1 \text{ V/R}_{WB}, V_{DD} = 5 \text{ V}, \text{ code} = \text{half scale}$ |     | 30         | 65       | Ω      |

|                                               |                                                           | $I_W = 1 \text{ V/R}_{WB}, V_{DD} = 3 \text{ V}, \text{ code} = \text{half scale}$ |     | 50         |          |        |

| Nominal resistance match                      | R <sub>AB1</sub> /R <sub>AB2</sub>                        | Code = full scale, T <sub>A</sub> = 25°C                                           |     | ±0.1       |          | %      |

| DC characteristics - Potentiometer of         | divider mode (All R                                       | PDACs)                                                                             |     |            |          | _      |

| Resolution                                    | N                                                         |                                                                                    |     |            | 10       | Bits   |

| Differential nonlinearity <u>5</u> /          | DNL                                                       |                                                                                    | -1  |            | +1       | LSB    |

| Integral nonlinearity <u>5</u> /              | INL                                                       |                                                                                    | -1  |            | +1       | LSB    |

| Voltage divider temperature coefficient       | (ΔV <sub>W</sub> /V <sub>W</sub> )ΔT x<br>10 <sup>6</sup> | Code = half scale                                                                  |     | 15         |          | ppm/°C |

| Full scale error                              | V <sub>WFSE</sub>                                         | Code = full scale                                                                  | -7  |            | 0        | LSB    |

| Zero scale error                              | V <sub>WZSE</sub>                                         | Code = zero scale                                                                  | 0   |            | 5        | LSB    |

| Resistor terminals                            |                                                           |                                                                                    |     |            |          |        |

| Terminal voltage range 6/                     | $V_A$ , $V_B$ , $V_W$                                     |                                                                                    | Vss |            | $V_{DD}$ | V      |

| Capacitance Ax, Bx 7/                         | C <sub>A</sub> , C <sub>B</sub>                           | f = 1 MHz, measured to GND,                                                        |     | 11         |          | pF     |

| Capacitance Wx 7/                             | Cw                                                        | code = half scale                                                                  |     | 80         |          |        |

| Common mode leakage current 7/ 8/             | I <sub>CM</sub>                                           | $V_W = V_{DD}/2$                                                                   |     | 0.01       | ±1       | μΑ     |

| Digital inputs and outputs                    |                                                           |                                                                                    |     |            |          |        |

| Input logic high                              | V <sub>IH</sub>                                           | With respect to GND, V <sub>DD</sub> = 5 V                                         | 2.4 |            |          | V      |

| Input logic low                               | $V_{IL}$                                                  | With respect to GND, V <sub>DD</sub> = 5 V                                         |     |            | 0.8      |        |

| Input logic high                              | $V_{IH}$                                                  | With respect to GND, V <sub>DD</sub> = 3 V                                         | 2.1 |            |          |        |

| Input logic low                               | $V_{IL}$                                                  | With respect to GND, V <sub>DD</sub> = 3 V                                         |     |            | 0.6      |        |

| Input logic high                              | V <sub>IH</sub>                                           | With respect to GND, $V_{DD} = +2.5 \text{ V}$ , $V_{SS} = -2.5 \text{ V}$         | 2.0 |            |          |        |

| Input logic low                               | V <sub>IL</sub>                                           | With respect to GND, $V_{DD} = +2.5 \text{ V}$ , $V_{SS} = -2.5 \text{ V}$         |     |            | 0.5      | •      |

| Output logic high (SDO, RDY)                  | V <sub>OH</sub>                                           | $R_{PULL-UP} = 2.2 \text{ k}\Omega \text{ to 5 V}$                                 | 4.9 |            |          | 1      |

| Output logic low                              | V <sub>OL</sub>                                           | I <sub>OL</sub> = 1.6 mA, V <sub>LOGIC</sub> = 5 V                                 |     |            | 0.4      | 1      |

| Input current                                 | I <sub>IL</sub>                                           | , 2000                                                                             |     |            | ±2.25    | μA     |

| Input capacitance 7/                          | C <sub>IL</sub>                                           |                                                                                    |     | 5          |          | pF     |

See footnotes at end of table.

| DLA LAND AND MARITIME | SIZE | CODE IDENT NO. | DWG NO.          |

|-----------------------|------|----------------|------------------|

| COLUMBUS, OHIO        | A    | <b>16236</b>   | <b>V62/11605</b> |

|                       |      | REV A          | PAGE 5           |

TABLE I.  $\underline{\text{Electrical performance characteristics}}$  - Continued.  $\underline{1}/$

| Test                                                                  | Symbol                   | Test conditions                                                                                                                                                                                                                                      |       | Limits            |       | Unit   |

|-----------------------------------------------------------------------|--------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|-------------------|-------|--------|

|                                                                       |                          | 2/ unless otherwise specified                                                                                                                                                                                                                        | Min   | Тур<br><u>3</u> / | Max   |        |

| Power supplies                                                        |                          |                                                                                                                                                                                                                                                      |       |                   |       |        |

| Single supply power range                                             | $V_{DD}$                 | $V_{SS} = 0 V$                                                                                                                                                                                                                                       | 2.7   |                   | 5.5   | V      |

| Dual supply power range                                               | $V_{DD}/V_{SS}$          |                                                                                                                                                                                                                                                      | ±2.25 |                   | ±2.75 | V      |

| Positive supply current                                               | I <sub>DD</sub>          | $V_{IH} = V_{DD}$ or $V_{IL} = GND$                                                                                                                                                                                                                  |       | 2                 | 7     | μΑ     |

| Negative supply current                                               | I <sub>SS</sub>          | $V_{IH} = V_{DD}$ or $V_{IL} = GND$ , $V_{DD} = +2.5$ V, $V_{SS} = -2.5$ V                                                                                                                                                                           | -6    | -2                |       | μA     |

| EEMEM store mode current                                              | I <sub>DD(store)</sub>   | $V_{IH} = V_{DD}$ or $V_{IL} = GND$ , $V_{SS} = GND$ , $I_{SS} \approx 0$                                                                                                                                                                            |       | 2                 |       | mA     |

|                                                                       | I <sub>SS(store)</sub>   | $V_{DD} = +2.5 \text{ V}, V_{SS} = -2.5 \text{ V}$                                                                                                                                                                                                   |       | -2                |       | mA     |

| EEMEM restore mode current 9/                                         | I <sub>DD(restore)</sub> | $V_{IH} = V_{DD}$ or $V_{IL} = GND$ , $V_{SS} = GND$ , $I_{SS} \approx 0$                                                                                                                                                                            |       | 320               |       | μΑ     |

|                                                                       | I <sub>SS(restore)</sub> | $V_{DD} = +2.5 \text{ V}, V_{SS} = -2.5 \text{ V}$                                                                                                                                                                                                   |       | -320              |       | μA     |

| Power dissipation 10/                                                 | P <sub>DISS</sub>        | $V_{IH} = V_{DD}$ or $V_{IL} = GND$                                                                                                                                                                                                                  |       | 10                | 40    | μW     |

| Power supply sensitivity 7/                                           | Pss                      | $\Delta V_{DD} = 5 \text{ V} \pm 10\%$                                                                                                                                                                                                               |       | 0.006             | 0.01  | %/%    |

| Dynamic characteristics $\underline{7}/\underline{11}/\underline{11}$ | ,                        |                                                                                                                                                                                                                                                      |       |                   |       |        |

| Bandwidth                                                             | BW                       | $-3 \text{ dB}, V_{DD}/V_{SS} = \pm 2.5 \text{ V}$                                                                                                                                                                                                   |       | 125               |       | kHz    |

| Total harmonic distortion                                             | THD <sub>W</sub>         | $V_A = 1 \text{ V rms}, V_B = 0 \text{ V}, f = 1 \text{ kHz}$                                                                                                                                                                                        |       | 0.009             |       | %      |

| V <sub>W</sub> settling time                                          | ts                       | $V_A = V_{DD}$ , $V_B = 0$ V,<br>$V_W = 0.50\%$ error band,<br>Code 0x000 to code 0x200                                                                                                                                                              |       | 4                 |       | μs     |

| Resistor noise density                                                | e <sub>N_WB</sub>        | T <sub>A</sub> = 25°C                                                                                                                                                                                                                                |       | 20                |       | nV/√Hz |

| Crosstalk (C <sub>W1</sub> /C <sub>W2</sub> )                         | Ст                       | $V_A = V_{DD}$ , $V_B = 0$ V, measured $V_{W1}$ with $V_{W2}$ making full scale change                                                                                                                                                               |       | 30                |       | nV-s   |

| Analog crosstalk                                                      | Ста                      | $\begin{split} V_{DD} &= V_{A1} = +2.5 \text{ V}, \ V_{SS} = V_{B1} = -2.5 \text{ V}, \\ \text{measured } V_{W1} \text{ with} \\ V_{W2} &= 5 \text{ Vp-p@f} = 1 \text{ kHz}, \\ \text{Code } 1 &= 0x200, \text{ code } 2 = 0x3\text{FF} \end{split}$ |       | -110              |       | dB     |

See footnotes at end of table.

| DLA LAND AND MARITIME | SIZE | CODE IDENT NO. | DWG NO.          |

|-----------------------|------|----------------|------------------|

| COLUMBUS, OHIO        | A    | <b>16236</b>   | <b>V62/11605</b> |

|                       |      | REV A          | PAGE 6           |

TABLE I. <u>Electrical performance characteristics</u> - Continued.

| Test                                                                          | Symbol                          | Test conditions                                  |     | Limits |     | Unit             |

|-------------------------------------------------------------------------------|---------------------------------|--------------------------------------------------|-----|--------|-----|------------------|

|                                                                               |                                 | <u>2</u> /                                       | Min | Max    |     |                  |

|                                                                               |                                 | unless otherwise specified                       |     |        |     |                  |

| Interface timing and EEMEM reliability cha                                    | aracteristics                   | s <u>12</u> /                                    |     |        |     |                  |

| Clock cycle time (t <sub>CYC</sub> )                                          | t <sub>1</sub>                  |                                                  | 20  |        |     | ns               |

| CS setup time                                                                 | t <sub>2</sub>                  |                                                  | 10  |        |     | ns               |

| CLK shut down time for $\overline{\text{CS}}$ rise                            | t <sub>3</sub>                  |                                                  | 1   |        |     | t <sub>CYC</sub> |

| Input clock pulse width                                                       | t <sub>4</sub> , t <sub>5</sub> | Clock level high or low                          | 10  |        |     | ns               |

| Data setup time                                                               | t <sub>6</sub>                  | From positive CLK transition                     | 5   |        |     |                  |

| Data hold time                                                                | t <sub>7</sub>                  | From positive CLK transition                     | 5   |        |     |                  |

| CS to SDO-SPI line acquire                                                    | t <sub>8</sub>                  |                                                  |     |        | 40  |                  |

| CS to SDO-SPI line release                                                    | t <sub>9</sub>                  |                                                  |     |        | 50  |                  |

| CLK to SDO propagation delay 13/                                              | t <sub>10</sub>                 | $R_P = 2.2 \text{ k}\Omega, C_L < 20 \text{ pF}$ |     |        | 50  |                  |

| CLK to SDO data hold time                                                     | t <sub>11</sub>                 | $R_P = 2.2 \text{ k}\Omega, C_L < 20 \text{ pF}$ | 0   |        |     |                  |

| CS high pulse width 14/                                                       | t <sub>12</sub>                 |                                                  | 10  |        |     |                  |

| $\overline{\text{CS}}$ high to $\overline{\text{CS}}$ high $\underline{14}$ / | t <sub>13</sub>                 |                                                  | 4   |        |     | tcyc             |

| RDY rise to $\overline{\text{CS}}$ fall                                       | t <sub>14</sub>                 |                                                  | 0   |        |     | ns               |

| CS rise to RDY fall time                                                      | t <sub>15</sub>                 |                                                  |     | 0.15   | 0.3 | ms               |

| Store EEMEM time 15/ 16/                                                      | t <sub>16</sub>                 | Applies to instruction 0x2, 0x3                  |     | 15     | 50  | ms               |

| Read EEMEM time 15/                                                           | t <sub>16</sub>                 | Applies to instruction 0x8, 0x9, and 0x10        |     | 7      | 30  | μs               |

| CS rise to clock rise/Fall setup                                              | t <sub>17</sub>                 |                                                  | 15  |        |     | ns               |

| Preset pulse width (Asynchronous) 17/                                         | t <sub>PRW</sub>                |                                                  | 50  |        |     | ns               |

| Preset response time to wiper setting 17/                                     | t <sub>PRESP</sub>              | PRpulsed low to refresh wiper positions          |     | 30     |     | μs               |

| Power ON EEMEM restore time 17/                                               | t <sub>EEMEM</sub>              |                                                  |     | 30     |     | μs               |

| Flash/EE memory reliability                                                   |                                 |                                                  |     |        |     |                  |

| Endurance <u>18</u> /                                                         |                                 | T <sub>A</sub> = 25°C                            |     | 1      |     | MCycles          |

|                                                                               |                                 |                                                  | 100 |        |     | kCycles          |

| Data retention 19/                                                            |                                 |                                                  |     | 100    |     | Years            |

See footnotes at end of table.

| DLA LAND AND MARITIME | SIZE | CODE IDENT NO. | DWG NO.          |

|-----------------------|------|----------------|------------------|

| COLUMBUS, OHIO        | A    | <b>16236</b>   | <b>V62/11605</b> |

|                       |      | REV A          | PAGE 7           |

### TABLE I. Electrical performance characteristics - Continued.

- 1/ Testing and other quality control techniques are used to the extent deemed necessary to assure product performance over the specified temperature range. Product may not necessarily be tested across the full temperature range and all parameters may not necessarily be tested. In the absence of specific parametric testing, product performance is assured by characterization and/or design.

- 2/ V<sub>DD</sub> = 3 V to 5.5 V, V<sub>SS</sub> =0; V<sub>DD</sub> = 2.5 V, V<sub>SS</sub> = -2.5 V, V<sub>A</sub> = V<sub>DD</sub>, V<sub>B</sub> = V<sub>SS</sub>, -40°C < T<sub>A</sub> < 125°C (unless otherwise noted). The part can be operated at 2.7 V single supply, except from 0°C to -40°C, where a minimum of 3 V is needed.

- 3/ Typicals (TYP) represent average readings at 25°C and  $V_{DD} = 5V$ .

- 4/ Resistor position nonlinearity error (R-INL) is the deviation from an ideal value measured between the maximum resistance and the minimum resistance wiper positions. R-DNL measures the relative step change from ideal between successive tap positions. I<sub>W</sub> ~ 50 μA for V<sub>DD</sub> = 2.7 V and I<sub>W</sub> ~ 400 μA for V<sub>DD</sub> = 5 V.

- 5/ INL and DNL are measured at VW with the RDAC configured as a potentiometer divider similar to a voltage output DAC. V<sub>A</sub> = V<sub>DD</sub> and V<sub>B</sub> = V<sub>SS</sub>. DNL specification limits of ±1 LSB maximum guaranteed monotonic operating conditions.

- 6/ Resistor terminal A, Resistor terminal B, and resistor terminal W has no limitations on polarity with respect to each other. Dual supply operation enables ground-referenced bipolar signal adjustment.

- 7/ Guaranteed by design and not subject to production test.

- 8/ Common mode leakage current is a measure of the dc leakage from any terminal A, terminal B, or terminal W to a common mode bias level of V<sub>DD</sub>/2.

- 9/ EEMEM response mode current is not continuous. Current is consumed while EEMEM locations are read and transferred to the RDAC register. To minimize power dissipation, on a NOP, instruction 0 (0x0) should be issued immediately after instruction 1 (0x1).

- $\underline{10}$ / P<sub>DISS</sub> is calculated from (I<sub>DD</sub> x V<sub>DD</sub>) + (I<sub>SS</sub> x V<sub>SS</sub>).

- 11/ All dynamic characteristics use  $V_{DD} = +2.5 \text{ V}$  and  $V_{SS} = -2.5 \text{ V}$ .

- $\underline{12}$ / Guaranteed by design and not subject to production test. See the timing diagrams section for the location of measured values. All input control voltages are specified with  $t_R = t_F = 2.5$  ns (10% to 90% of 3 V) and timed from a voltage level 0f 1.5 V. Switching characteristics are measured using both  $V_{DD} = 3$  V and  $V_{DD} = 5$  V.

- 13/ Propagation delay depends on the value of VDD, RPULL-UP, and CL.

- 14/ Valid for commands that do not activate the RDY pin.

- 15/ RDY pin low only for Instruction 2, Instruction 3, Instruction 8, Instruction 9, Instruction 10, and the PR hardware pulse; CMD\_8 ~ 20 μs; CMD\_9, CMD\_10 ~ 7 μs; CMD\_2, CMD\_3 ~ 15 ms; PR hardware pulse ~30 μs.

- 16/ Store EEMEM time depends on the temperature and EEMEJM writes cycles. Higher timing is expected at a lower temperature and higher write cycles.

- 17/ Not shown in FIGURE 5 and FIGURE 6.

- 18/ Endurance is qualified to 100,000 cycles per JEDEC standard 22, method A117 and measured at -40°C, +25°C, and +125°C.

- 19/ Retention life time equivalent at junction temperature (T<sub>J</sub>) = 85°C per JEDEC standard 22, method A117. Retention lifetime based on an activation energy of 1 eV derates with junction temperature in the Flash/EE memory.

| DLA LAND AND MARITIME | SIZE | CODE IDENT NO. | DWG NO.          |

|-----------------------|------|----------------|------------------|

| COLUMBUS, OHIO        | A    | <b>16236</b>   | <b>V62/11605</b> |

|                       |      | REV A          | PAGE 8           |

| Dimensions |             |      |        |          |        |  |

|------------|-------------|------|--------|----------|--------|--|

| Symbol     | Millimeters |      | Symbol | Millim   | neters |  |

|            | Min         | Max  |        | Min      | Max    |  |

| Α          |             | 1.20 | Е      | 4.30     | 4.50   |  |

| A1         | 0.05        | 0.15 | E1     | 6.40 TYP |        |  |

| b          | 0.19        | 0.30 | е      | 0.65 BSC |        |  |

| С          | 0.09        | 0.20 | L      | 0.45     | 0.75   |  |

| D          | 4.90        | 5.10 |        |          |        |  |

FIGURE 1. Case outline.

| DLA LAND AND MARITIME | SIZE | CODE IDENT NO. | DWG NO.          |

|-----------------------|------|----------------|------------------|

| COLUMBUS, OHIO        | A    | <b>16236</b>   | <b>V62/11605</b> |

|                       |      | REV A          | PAGE 9           |

|                 | Case outline X  |                 |                    |  |  |  |  |

|-----------------|-----------------|-----------------|--------------------|--|--|--|--|

| Terminal number | Terminal symbol | Terminal number | Terminal<br>symbol |  |  |  |  |

| 1               | CLK             | 16              | RDY                |  |  |  |  |

| 2               | SDI             | 15              | CS                 |  |  |  |  |

| 3               | SDO             | 14              | $\overline{PR}$    |  |  |  |  |

| 4               | GND             | 13              | WP                 |  |  |  |  |

| 5               | $V_{SS}$        | 12              | $V_{DD}$           |  |  |  |  |

| 6               | A1              | 11              | A2                 |  |  |  |  |

| 7               | W1              | 10              | W2                 |  |  |  |  |

| 8               | B1              | 9               | B2                 |  |  |  |  |

FIGURE 2. <u>Terminal connections</u>.

| Pin No. | Mnemonic        | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|---------|-----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1       | CLK             | Serial Input Register Clock. Shifts in one bit at a time on positive clock edges.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 2       | SDI             | Serial Data Input. Shifts in one bit at a time on positive clock CLK edges. MSB loads first.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 3       | SDO             | Serial Data Output. Serves readback and daisy-chain functions. Command 9 and Command 10 activate the SDO output for the readback function, delayed by 24 or 25 clock pulses, depending on the clock polarity before and after the data-word (see Figure 2 and Figure 3). In other commands, the SDO shifts out the previously loaded SDI bit pattern, delayed by 24 or 25 clock pulses depending on the clock polarity (see Figure 2 and Figure 3). This previously shifted out SDI can be used for daisy-chaining multiple devices. Whenever SDO is used, a pull-up resistor in the range of 1 k $\Omega$ to 10 k $\Omega$ is needed. |

| 4       | GND             | Ground Pin, Logic Ground Reference.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 5       | V <sub>SS</sub> | Negative Supply. Connect to 0 V for single-supply applications. If $V_{SS}$ is used in dual supply, it must be able to sink 35 mA for 30 ms when storing data to EEMEM.                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 6       | A1              | Terminal A of RDAC1.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 7       | W1              | Wiper terminal of RDAC1.ADDR(RDAC1)=0x0.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 8       | B1              | Terminal B of RDAC1.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 9       | B2              | Terminal B of RDAC2.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 10      | W2              | Wiper terminal of RDAC2.ADDR(RDAC2)=0x1.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 11      | A2              | Terminal A of RDAC2.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 12      | $V_{DD}$        | Positive Power Supply.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 13      | WP              | Optional Write Protect. When active low, $\overline{WP}$ prevents any changes to the present contents, except $\overline{PR}$ strobe. CMD_1 and COMD_8 refresh the RDAC register from EEMEM. Execute a NOP instruction before returning to $\overline{WP}$ high. Tie $\overline{WP}$ to $V_{DD}$ , if not used.                                                                                                                                                                                                                                                                                                                        |

| 14      | PR              | Optional Hardware Override Preset. Refreshes the scratchpad register with current contents of the EEMEM register. Factory default loads midscale 512 <sub>10</sub> until EEMEM is loaded with a new value by the user. $\overline{PR}$ is activated at the logic high transition. Tie $\overline{PR}$ to $V_{DD}$ , if not used.                                                                                                                                                                                                                                                                                                       |

| 15      | CS              | Serial Register Chip Select Active Low. Serial register operation takes place when $\overline{\text{CS}}$ returns to logic high.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 16      | RDY             | Ready. Active high open-drain output. Identifies completion of Instruction 2, Instruction 3, Instruction 8, Instruction 9, Instruction 10, and $\overline{PR}$ .                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

FIGURE 3. <u>Terminal functions</u>.

| DLA LAND AND MARITIME | SIZE | CODE IDENT NO. | DWG NO.          |

|-----------------------|------|----------------|------------------|

| COLUMBUS, OHIO        | A    | <b>16236</b>   | <b>V62/11605</b> |

|                       |      | REV A          | PAGE 10          |

FIGURE 4. Functional block diagram.

| DLA LAND AND MARITIME | SIZE | CODE IDENT NO. | DWG NO.          |

|-----------------------|------|----------------|------------------|

| COLUMBUS, OHIO        | A    | <b>16236</b>   | <b>V62/11605</b> |

|                       |      | REV A          | PAGE 11          |

### NOTES:

The extra bit that is not defined is normally the LSB of the character previously transmitted.

The CPOL = 1 microcontroller command aligns the incoming data to the positive edge of the clock.

FIGURE 5. Timing diagram.

#### NOTES:

The extra bit that is not defined is normally the MSB of the character just received.

The CPOL = 0 microcontroller command aligns the incoming data to the positive edge of the clock.

FIGURE 6. Timing diagram.

| DLA LAND AND MARITIME | SIZE | CODE IDENT NO. | DWG NO.          |

|-----------------------|------|----------------|------------------|

| COLUMBUS, OHIO        | A    | <b>16236</b>   | <b>V62/11605</b> |

|                       |      | REV A          | PAGE 12          |

#### 4. VERIFICATION

4.1 <u>Product assurance requirements</u>. The manufacturer is responsible for performing all inspection and test requirements as indicated in their internal documentation. Such procedures should include proper handling of electrostatic sensitive devices, classification, packaging, and labeling of moisture sensitive devices, as applicable.

### 5. PREPARATION FOR DELIVERY

- 5.1 <u>Packaging</u>. Preservation, packaging, labeling, and marking shall be in accordance with the manufacturer's standard commercial practices for electrostatic discharge sensitive devices.

- 6. NOTES

- 6.1 ESDS. Devices are electrostatic discharge sensitive and are classified as ESDS class 1 minimum.

- 6.2 <u>Configuration control</u>. The data contained herein is based on the salient characteristics of the device manufacturer's data book. The device manufacturer reserves the right to make changes without notice. This drawing will be modified as changes are provided.

- 6.3 <u>Suggested source(s) of supply</u>. Identification of the suggested source(s) of supply herein is not to be construed as a guarantee of present or continued availability as a source of supply for the item.

| Vendor item drawing administrative control number 1/ | Device<br>manufacturer<br>CAGE code | Vendor part number |

|------------------------------------------------------|-------------------------------------|--------------------|

| V62/11605-01XB                                       | 24355                               | AD5235BRU25-EP-RL7 |

1/ The vendor item drawing establishes an administrative control number for identifying the item on the engineering documentation.

<u>CAGE code</u> <u>Source of supply</u>

24355 Analog Devices Rt 1 Industrial Park

PO Box 9106 Norwood, MA 02062

Point of contact: 7910 Triad Center Drive Greensboro, NC 27409-9605

| DLA LAND AND MARITIME | SIZE | CODE IDENT NO. | DWG NO.          |

|-----------------------|------|----------------|------------------|

| COLUMBUS, OHIO        | A    | <b>16236</b>   | <b>V62/11605</b> |

|                       |      | REV A          | PAGE 13          |