# AN-1178 应用笔记

One Technology Way • P.O. Box 9106 • Norwood, MA 02062-9106, U.S.A. • Tel: 781.329.4700 • Fax: 781.461.3113 • www.analog.com

## AD7292 DAC禁用功能时序

作者: Norma O'Mahony

#### 简介

AD7292是一款单芯片解决方案,集外部器件的通用模拟信号监控和控制所需的全部功能于一体。

AD7292具有一个8通道10位SAR DAC、四个10位DAC、一个精度为±1°C的内部温度传感器,以及12个GPIO,可协助系统监控和控制。

DAC输出端VOUT0至VOUT3,具有最高5 V的输出电压范围(LSB为4.88 mV)。DAC输出缓冲器可通过配置寄存器组中的GPIO2/DAC DISABLE0和GPIO4/DAC DISABLE1子寄存器,以软件方式控制;或者通过GPIO2/DAC DISABLE0和GPIO4/DAC DISABLE1引脚,以硬件方式控制。

本应用笔记介绍与AD7292的DAC禁用功能关联的时序。

## **AN-1178**

## DAC禁用输出时序测量

## 硬件配置

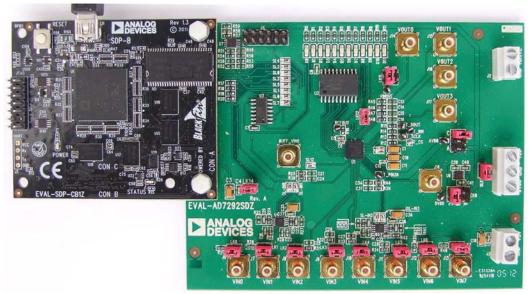

本应用笔记中介绍的测量结合使用EVAL-AD7292SDZ评估 板和评估软件以及EVAL-SDP-CB1Z系统演示平台电路板进 行。有关详细的设置和软件安装说明,请参见UG-449。

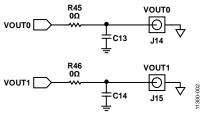

#### 评估板修改

考察了因为改变DAC输出负载电容而对DAC禁用时序造成的影响。为此, EVAL-AD7292SDZ评估板有两处需略做修改。默认情况下, EVAL-AD7292SDZ评估板物料清单要求

不装配C13和C14。这两个电容空间是考虑到将负载电容添加到VOUT0和VOUT1。分别用100 pF和330 pF电容填充C13和C14。

图1. VOUT0和VOUT1负载电容修改 (C13 = 100 pF, C14 = 330 pF)

图2. 硬件配置 - 评估板设置

#### 软件配置

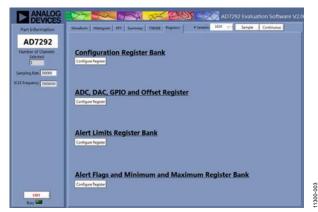

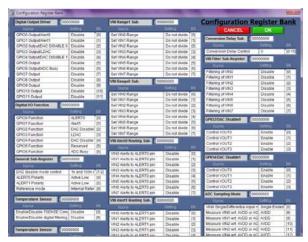

通过评估软件中的"寄存器"选项卡,用户可以配置内部 AD7292寄存器。

图3. EVAL-AD7292SDZ评估软件中的"寄存器"选项卡

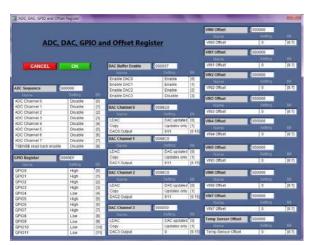

### ADC、DAC、GPIO和失调寄存器设置

DAC缓冲器使能寄存器(0x0A)

上电时,DAC输出缓冲器默认处于禁用状态。将D0至D3 位设置为1可使能DAC输出缓冲器。

## DAC通道寄存器(0x30至0x33)

通过对DAC通道寄存器的[D6:D15]位写入数据,将DAC输出VOUT1、VOUT2和VOUT3设置为3 V。

图4. ADC、DAC、GPIO和失调寄存器

#### 配置寄存器组设置

## GPIO2/DAC DISABLE0和GPIO4/DAC DISABLE1

GPIO2/DAC DISABLE0寄存器的内容未作改动,从而使DAC DISABLE功能被禁用。若要考察DAC禁用时序,就需要设置[D0:D2]位,从而禁用DAC输出VOUT0至VOUT3。可使用GPIO4/DAC DISABLE1寄存器执行相同功能。

注意,通用子寄存器中的默认DAC禁用模式控制位D1和 D2仍然保留了默认值而未作改动,从而获得 $1\,k\Omega$ 和 $100\,k\Omega$ 电阻并联接地的禁用模式。

图5. 配置寄存器组

900-00

## **AN-1178**

## 测量结果

### DAC禁用时序

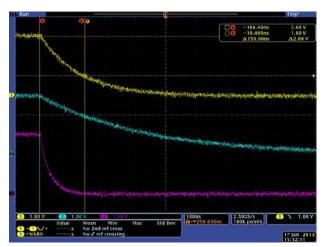

若要考察DAC禁用时序,就需要将GPIO2/DAC DISABLE0 寄存器的[D0:D2]位设置为1,从而禁用DAC输出VOUT0至 VOUT3。使用Tektronix TDS 3054示波器获取DAC输出从3 V 降至1 V所花的时间(见图6)。

图6. DAC禁用时序示波器曲线图

### 表1. DAC禁用时序

| DAC<br>输出 | 负载电容    | 示波器迹线 | VOUTx从3 V降<br>至1 V的时间<br>(典型值) |

|-----------|---------|-------|--------------------------------|

| VOUT0     | 100 p F | 黄色    | 150 ns                         |

| VOUT1     | 330 pF  | 蓝色    | 380 ns                         |

| VOUT2     | 0 pF    | 粉红    | 40 ns                          |

### 修订历史

2013年2月—修订版0: 初始版

#### DAC使能时序

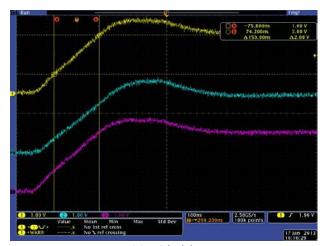

为了完整性起见,也测量了相反方向的时序。通过向GPIO2/DAC DISABLE0寄存器的[D0:D2]位写入0重新使能DAC输出。获取DAC输出从1V升至3V所花的时间(见图7)。

图7. 反向时序

#### 表2. DAC使能时序

| DAC<br>输出 | 负载电容   | 示波器迹线 | VOUTx从3 V降<br>至1 V的时间<br>(典型值) |

|-----------|--------|-------|--------------------------------|

| VOUT0     | 100 pF | 黄色    | 150 ns                         |

| VOUT1     | 330 pF | 蓝色    | 164 ns                         |

| VOUT2     | 0 pF   | 粉红    | 150 ns                         |