ANALOG Technical notes on using Analog Devices products and development tools Visit our Web resources http://www.analog.com/ee-notes and http://www.analog.com/processors or **DEVICES** e-mail processor.support@analog.com or processor.tools.support@analog.com for technical support.

# ADSP-CM40x Board Design Guidelines for Optimal ADC Performance

Contributed by Prashant Gawade and Kritika Shahu

Rev 1 - December 9, 2015

#### Introduction

ADSP-CM40xF mixed-signal control processors are based on the ARM® Cortex-M4<sup>TM</sup> core consisting of two 16-bit SAR-type ADCs and two 12-bit DACs, along with the associated analog subsystem and a rich set of peripherals and accelerators. This family of mixed-signal control processors is produced with a lowpower and low-voltage design methodology, delivering world-class processor and ADC performance with lower power consumption.

When designing ADSP-CM40x-based systems for optimal ADC performance, mixed-signal design aspects such as selection, placement, and partitioning of analog and digital components must be considered. As the processor, its peripherals, I/Os, and related digital circuits operate at higher clock rates, a significant amount of noise and radiation can degrade the ADC performance. Sustaining ADC performance in a hostile digital environment depends on good design techniques such as proper decoupling, signal routing and grounding. Design problems can result in inaccurate ADC readings, excessive electromagnetic interference (EMI), and other unwanted system behavior. Careful management of the board design process ensures better system control and reliability required for precision measurement and control systems. It also significantly reduces development time. This document provides some guidelines for consideration while designing ADSP-CM40x-based boards with a specific focus on how to achieve the best performance from the processor's ADCs.

# ADC Front-End Circuit Design

The analog subsystem of the ADSP-CM40xF processor contains two 16-bit, high-speed, low-power Successive Approximation Register (SAR)-type ADCs. SAR ADCs offer high resolution, excellent accuracy, and low power consumption. Each ADC has a maximum of 12 multiplexed analog input channels.

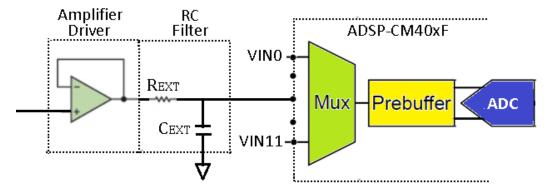

To get the best performance from SAR-type ADCs, designers should first focus on the design of the ADC front end, which interfaces the analog input signal to the ADC input channel. It consists of two parts: the driving operational amplifier (op-amp) and the RC filter, as shown in Figure 1.

Figure 1. SAR ADC Design

The amplifier conditions the input signal and acts as a low-impedance buffer between the signal source and the ADC input. The RC filter limits the amount of out-of-band noise arriving at the ADC input and helps to attenuate the kick from the switched capacitors in the ADC's input. The RC network also helps to relax the driving op-amp requirements.

Apart from the analog front end circuit, a signal conditioning circuit may also be required, depending upon the range of the input signal. The ADSP-CM40x ADC accepts analog signals in the range of 0-2.5V, which can be achieved by conditioning the analog input signal.

### **RC Filter Design**

The input signal bandwidth determines the low-noise needed over that frequency spectrum to get a good Signal-to-Noise Ratio (SNR). The RC filter network limits the bandwidth of the input signal and reduces the amount of noise fed to the ADC by the amplifier and other upstream circuitry. However, too much bandlimiting will increase the settling time and distort the input signal.

To select a suitable RC filter, the RC bandwidth for the ADC channel must be calculated, which is described in the *Front-End Amplifier and RC Filter Design for a Precision SAR Analog-to-Digital Converter* article<sup>[2]</sup>. Using the theory described in this article, consider the case where the maximum input sine wave frequency to the ADC is 5 kHz, and the maximum input voltage is 2.5V (V<sub>PEAK</sub> = 1.25V). The values of the external R-C components, R<sub>EXT</sub> and C<sub>EXT</sub>, can be calculated using the following specifications from the datasheet<sup>[1]</sup>:

- ADC Conversion Time (TCONV) = 380ns

- ADC Acquisition Time (TACQ) = 150ns

The one LSB voltage value for a 16-bit ADC with 2.5V VREF is  $38.1\mu V$ ; therefore, 1/4th the LSB voltage (V<sub>1/4LSB</sub>, required to settle for best SINAD) is  $9.54\mu V$ .

The voltage change of the sine wave for every sample (Vchange) is:

$$2\pi * fin * V_{PEAK} * T_{CONV} = 2\pi * 5000 * 1.25 * 380e-9 = 14.9 mV$$

VCHANGE is then attenuated by the parallel combination of the on-chip internal capacitor (Cint = 9pF) and external capacitor (Cext). Assuming Cext = 5.6nF, VSTEP is:

VCHANGE \* (CINT / (CINT + CEXT)) =

$$14.9e-3 * (9e-12 / (9e-12 + 5.6e-9)) = 23.9\mu V$$

From this, the number of time constants required to settle the input to 1/4th LSB during the acquisition time of the ADC (NTC) can be computed:

$$ln(V_{STEP} / V_{1/4LSB}) = ln(23.9e-6/9.54e-6) = 0.92$$

The Time Constant (TAU) then becomes:

$$T_{ACQ} / N_{TC} = 150e-9 / 0.92 = 163ns$$

And the bandwidth can then be computed:

$$1/(2\pi * Tau) = 1/(2\pi * 163e-9) = 977 \text{ kHz}$$

From this, the Rext value can then be calculated:

$$T_{AU} / C_{EXT} = 163e-9 / 5.6e-9 = 29.1 \Omega$$

For this example, it is safe to approximate this to the common 33  $\Omega$  resistor value. It is not advised to choose Cext lower than 3.3nF, as the voltage kick observed due to the sampling action of the ADC may not get fully replenished by the smaller external capacitor. Higher values of Cext can be chosen, but when used with lower bandwidth buffers, it might result in too much harmonic distortion at the input of the ADC. The resistor value ensures that the op-amp will not oscillate, and the capacitor value ensures that the ADC will have sufficient charge for each conversion. A capacitor with a low-voltage coefficient (which determines the THD of the system) should be chosen.

Note that nominal RC values calculated here are useful guidelines, not a final solution. Choosing the right balance between the Rext and Cext components requires knowledge of the input frequency range, how much capacitance the amplifier can drive, and the acceptable level of distortion. In order to optimize the RC values, it is important to experiment with actual hardware to arrive at the best performance. The RC filter should be placed as close as possible to the ADC channel pins of the processor to achieve best results. For more information on calculating the RC values beyond the previously referenced article<sup>[2]</sup>, please refer to the on-line filter tool provided by Analog Devices, located at <a href="http://www.analog.com/filterwizard.">http://www.analog.com/filterwizard.</a>

#### **Driving Amplifier Design**

It is recommended to have a driving amplifier circuit in the path before feeding the input signal to the ADC input channel. It helps to avoid loading of the input signal, thereby avoiding errors in ADC measurement. Generally, a low-noise operational amplifier (op-amp) in Voltage Follower mode is used for this purpose. The main factors which affect op-amp selection are input signal bandwidth, settling time requirements, noise and distortion amplifier specifications, and its own effect on system noise. It must have sufficient slew rate and fast transient response to charge the Rext-Cext according to input signal changes. In addition to these characteristics, another consideration is how the op-amp is powered.

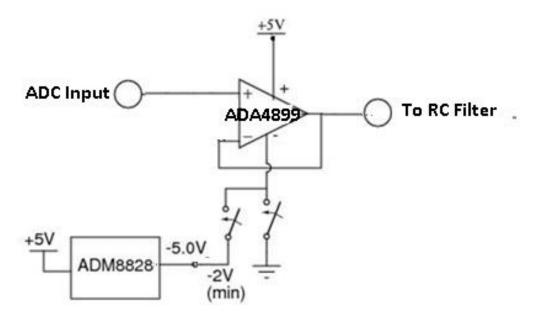

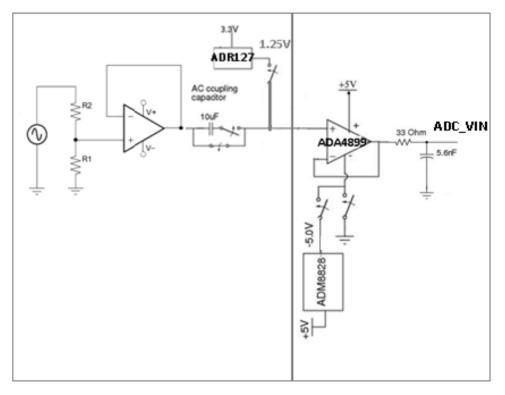

The ADA4899-1 is an ultra-low-noise  $(1nV/\sqrt{Hz})$  and distortion (<-117 dBc @1 MHz) unity-gain stable voltage feedback op-amp, making it ideal for 16-bit ADC systems which need high slew rates and low noise at unity gain. As for the power, the ADA4899 op-amp needs a dual-5V power supply (+5V and -5V) for the best performance.

If the application strictly demands full range from 0V-2.5V, or if the user intends to do linearity testing such as DNL or INL using the sine-wave histogram method, then it is recommended to provide a negative power supply with a minimum -2.0V at the -Vs pin of the ADA4899 buffer. This is because there is some distortion close to 0V, which can contribute to INL degradation. The board can integrate a charge-pump voltage inverter (ADM8828) to generate this negative supply (-5V), as shown in <u>Figure 2</u>.

Figure 2. Op-Amp as Driving Amplifier

For a slightly relaxed requirement, the -Vs pin of the op-amp can be connected to ground.

The DISABLEb pin of the ADA4899-1, if brought to within 0.7 V of the positive supply, reduces the input bias current by a factor of 100; hence, the DISABLEb pin should be connected to +5V and should not be left floating.

Note that the combination of Rext and Cext determines the stability of the operational amplifier. A single-supply AD8655 op-amp can also be used for the driving amplifier if the application does not demand full range and cannot provide a negative supply.

# Signal Conditioning Circuit Design

In order to allow a variety of input signals to be interfaced with the ADSP-CM40x ADC, signal conditioning must be performed on the analog inputs to get them in the range of 0-2.5V. Some key components of a signal conditioning circuit are the filter, attenuator, amplifier, and level shifter, depending upon the type of analog signal supplied. If the application provides analog signals in the suitable range for the ADC, it may not be required to add a signal conditioning circuit in the system.

For example, if the analog input is coming directly from a sensor, the signal can first pass through a filter in order to reduce the noise and limit the bandwidth. Then, depending on the range of the analog input, the signal can either be attenuated or amplified in order to match the range of the ADC. The attenuated/amplified signals can pass through a level-shifter (for bipolar analog signals).

### **Analog Input Scaling**

Most signal conditioning designs use different types of circuits to amplify or attenuate the analog signal. Modern analog circuits consist of basic integrated operational amplifiers, which contain many circuit components but are typically portrayed as a simple functional block.

### **Amplifier Stage**

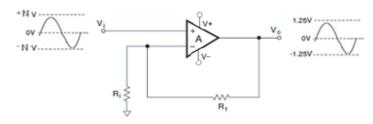

Many sensors, such as LVDT, thermocouple, and current, generate low-level output signals. These sensor outputs are often weak and must be amplified in order to occupy as much of the ADC's dynamic range as possible. The amplifying stage can be designed with the help of a non-inverting op-amp, as shown in <u>Figure 3</u>.

Figure 3. Non-Inverting Op-Amp Circuit

The gain of the amplifier can be set by configuring the feedback  $(R_f)$  and input  $(R_i)$  resistor values according to the gain equation:

$$V_{o} / V_{i} = 1 + (R_{f} / R_{i})$$

For bipolar analog signals with amplitude less than 1.25V, the signals should be amplified before being provided to the ADC. The gain should be configured such that the amplifier output is in the range of -1.25V to +1.25V.

### **Attenuator Stage**

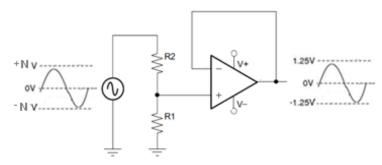

For high-voltage analog signals, the signals must be attenuated to levels acceptable to the ADC. One approach to attenuator circuit design is to use a buffered voltage divider. The circuit shown in <u>Figure 4</u> consists of a voltage divider followed by an op-amp in the Voltage Follower configuration.

Figure 4. Attenuator Circuit

The attenuation factor can be set by configuring the R1 and R2 resistors according to the equation:

$$V_o / V_i = R1 / (R1+R2)$$

For bipolar analog signals with amplitude greater than 1.25V, the signals should be attenuated before being provided to the ADC. The attenuation factor should be configured such that the attenuator output is in the range of -1.25V to +1.25V.

#### **Level Shifter**

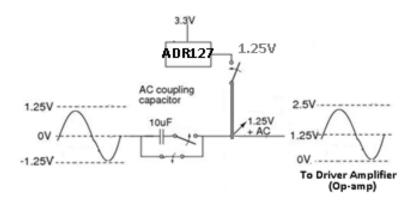

Bipolar analog signals coming out of the amplifier/attenuator circuit should pass through a level shifter in order to make them unipolar and in the range of 0-2.5V. A level shifter can be implemented in an AC coupling scheme for this purpose, as shown in Figure 5.

Figure 5. 1.25V Level Shifter

A DC offset of 1.25V is provided by the micro-power, low-dropout (LDO) voltage reference (ADR127), which requires only 1.45V above the nominal output voltage on the input to provide a stable output voltage. The level shifter circuit design provides an input of 3.3V to the ADR127, and the generated output of 1.25V will be used to level-shift the bipolar analog input.

The level-shifting scheme should be implemented on the board such that the DC offset can be bypassed, if required, depending upon the type of analog signal supplied (unipolar or bipolar). In order to sample unipolar analog signals, the 10µF capacitor and the ADR127 output must be bypassed in the circuit.

# **Analog Signal Flow Chain**

The complete analog signal chain will consist of both the signal conditioning circuit and the analog front end circuit, as previously discussed. However, a signal conditioning circuit is optional and depends upon the range of the input signal.

In order to achieve the best performance, the analog input should be a noise-free signal. Figure 6 provides a complete analog signal chain circuit for the case where attenuation is required. The analog input from a sensor or signal generator passes through an attenuator or an amplifier, depending on the range of the input signal, to scale the signal range to -1.25V to +1.25V. The signal then passes through a 1.25V level shifter to shift the range to 0-2.5V. After conditioning the analog input signal, the driving amplifier helps to drive the ADC, and then the signal passes through the RC filter before being supplied to the ADSP-CM40x ADC input channel.

#### SIGNAL CONDITIONING

#### ANALOG FRONT END

Figure 6. Analog Signal Flow Chain

# **Power Supply Design**

The power supply is a very important aspect of the board design and one of the major factors in controlling noise and radiation. A clean and stable power supply is required for all system designs. In a mixed-signal system, having separate power supplies for the analog and digital circuits is highly desirable.

Thoughtfully determining the power supply architecture that is the best fit for the application is extremely important. The SMPS power supply has high efficiency, which makes it an ideal choice for designs where saving power is critical, such as in battery-powered applications; however, switching supplies introduce high-frequency noise to the power supply net. LDO linear regulators have some advantages, such as low noise with a high power supply rejection ratio, fast response to load changes, and low cost.

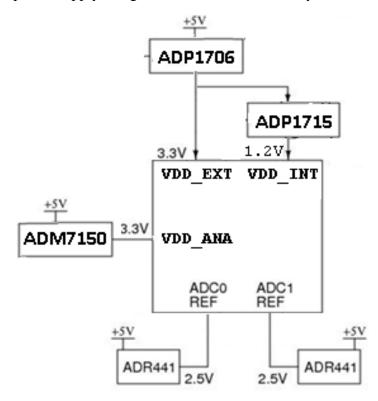

The ADSP-CM40x processor has three main power domains:

- VDD\_EXT 3.3V digital power domain for flash memory, peripherals, and I/O

- VDD\_INT 1.2V digital power domain for M4 core operation

- VDD\_ANA 3.3V analog power domain used by the processor's analog subsystem

It is recommended that all three power domains be separately generated from LDO regulators rather than switching regulators, as switching regulators can increase ground bounce noise and lead to a leakage path in the analog power domain. Further, the VDD\_EXT and VDD\_ANA power domains should not be shared, despite the fact that they are both 3.3V. As such, separate power planes should be created for VDD\_EXT and VDD\_ANA, and it is critically important that digital power planes do not overlap analog power planes.

<u>Figure 7</u> shows a typical power supply design for an ADSP-CM40xF system.

Figure 7. Typical Power Supply Network for an ADSP-CM40xF System

The VDD\_INT supply can be internally generated using a STD2805T4 PNP transistor connected to the VREG\_BASE pin of the processor.

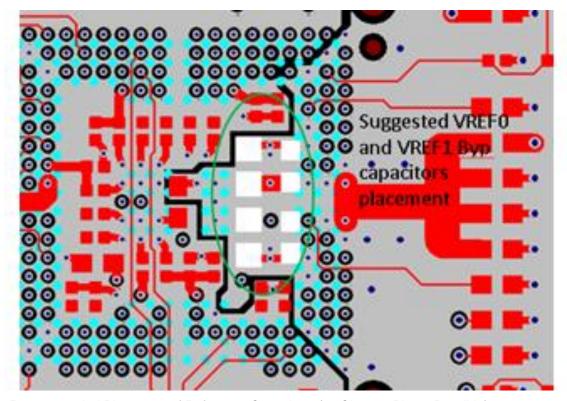

Each ADC has an on-chip 2.5V reference that can be overridden when an external reference is preferred. If an external reference is selected, 2.5V should be supplied at the VREFn (Voltage Reference for ADC) pins of the processor, and bypass capacitors should be connected as close as possible to the VREFn pins.

### **Bypass/Decoupling Capacitors**

A proper decoupling scheme is needed on both the analog and digital power supplies. Good decoupling is important to control the noise within the system and to ensure that power supply droop is lower than the specified limits. For the digital portion, the capacitors on the VDD\_EXT and VDD\_INT power supplies serve as mini-charge-reservoirs for the respective domains. For the analog subsystem, the bypass capacitors on the VDD\_ANA power supply help to redirect high frequency noise that may otherwise enter the sensitive analog portion of the chip through the power supply pins.

The analog subsystem of the processor also brings out a few pins for bypassing purposes:

- BYP\_An the on-chip analog power regulation bypass filter node for the ADC

- BYP D0 the on-chip digital power regulation bypass filter node for the analog subsystem

- REFCAP analog output of the band-gap generator filter node

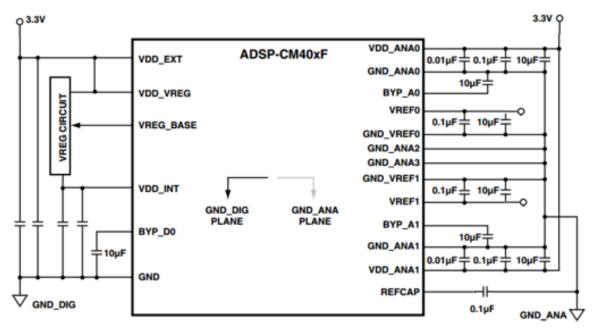

Figure 8 shows the recommended decoupling scheme for the analog and digital sections of the processor:

Figure 8. Recommended Decoupling Scheme

Bypass capacitors on the BYP\_An and REFCAP pins should be connected to analog ground (AGND), and bypass capacitor on the BYP\_D0 pin should be connected to digital ground (DGND). In addition to these recommendations, the VREF pins should also be properly terminated with bypass or decoupling capacitors to analog ground (AGND).

The recommended bypass/decoupling capacitor values for the analog subsystem are:

- VDD\_ANA0 and VDD\_ANA1: parallel 0.01μF, 0.1μF and 10μF

- VREF0 and VREF1: parallel 0.1μF and 10μF

- BYP\_A0 and BYP\_A1: 10μF

- REFCAP: 0.1μF

The digital power supplies (VDD\_EXT and VDD\_INT) should be decoupled with  $10\mu F$  capacitor. In addition, it is recommended to connect  $0.1\mu F$  and  $0.01\mu F$  capacitors in parallel for individual VDD\_EXT and VDD\_INT pins.

To achieve the best outcome from this decoupling scheme, the capacitors must be placed as close as possible to the respective pins, ideally adjacent to the device, with the widest possible trace. Ceramic capacitors are the best choice for these decoupling capacitors, and they should have low Effective Series Resistance (ESR) and Inductance (ESI), which provides a low-impedance path to ground at high frequencies to handle transient currents due to internal logic switching.

# **Board Layout Guidelines**

Though PCB layout is one of the last steps in the design process, it is the most critical. Grounding of analog and digital components is one of the most debated topics in a mixed-signal system design. A common concern is how to isolate the analog and digital grounds so that the noisy digital circuitry does not interfere with the analog circuitry and affect its performance. Analog circuitry is highly susceptible to noise and can be easily affected by large, fast-switching current spikes drawn by the digital circuitry. Ideally, the sensitive analog components are totally isolated from the noisy digital circuitry in terms of placement, routing and plane creation. It is also possible that high-speed digital logic might get interference from the low-level analog circuits.

It is beneficial to use separate ground planes for the analog and digital circuitry, using the split-plane ground technique. Separating the analog current return path from the noisier digital current return path can improve ADC performance. Use a large-area, low-impedance ground plane to provide a better return path for decoupling high-frequency currents and to minimize EMI/RFI emissions. Currents should be efficiently returned to their sources through the smallest possible loop.

The analog and digital ground planes should not overlap one another. This will avoid, or at least minimize, capacitive coupling between them, which may cause RF emissions from one plane to another. Placement of components is very important. Analog traces should be routed under the analog sections only, with respect to their analog reference planes; and digital traces should run only with digital reference planes to maintain the homogeneous nature of current density (i.e., digital currents must not flow in the analog section of the ground plane and vice versa). This is the decisive factor in ensuring how well analog circuitry signals flow through the PCB, as well as how the planes are split to keep analog characteristics isolated from the digital section. It is sensible to arrange the different blocks in such a way that interaction between the potentially noisy circuit blocks and sensitive analog circuits is minimized. The first need is for good floor planning.

Some of the common recommendations with respect to signal traces are:

- trace length should always be minimized

- trace width should remain constant throughout the length of the trace

- the turns in traces should be routed using two 45 degree turns instead of one 90 degree turn

The best layer stack-up strategy is to use a ground plane under each new signal or power plane so that the return current of one signal will have a minimal affect on another signal. Placing the ground planes close to a signal source reduces inductance (and hence the EMI). But for cost reasons, each signal layer can be placed in between the ground plane and the power plane.

The components in analog circuitry and the ADSP-CM40xF processor should be soldered directly to the respective signal, power or ground plane to minimize series inductance and resistance. The use of traditional IC sockets is not recommended, as they may add extra inductance and capacitance to degrade the device performance. If sockets must be used, as in prototyping, the leads should be mechanically very tiny and should have as little self-inductance and self-capacitance as possible.

The ADC clock is derived from the Clock Generating Unit's (CGU) system clock, which is based from the processor's input clock. A precise and low-jitter clock must be input to the processor.

# **Processor-Specific Guidelines**

The ADSP-CM40x processor is neatly designed to prevent coupling of noise generated by digital logic into the analog subsystem; however, there are certain measures that can be taken in application software to minimize the digital ground noise, thereby boosting ADC performance. The processor integrates a Dynamic Power Management (DPM) unit, which controls transitions between different power-saving modes. It also allows individual clock domains to be enabled or disabled and permits operation of multiple external wake-up sources. It is best to exercise power-saving modes whenever possible in the application code.

The unused GPIO pins of the processor can be handled in one of the following ways:

- Configured in GP output mode and driven low

- Configured in GP input mode with input buffer enabled (set INEN bit) such that these pins will be tri-stated and the internal pull-up resistor on them will be disabled.

# **Design Verification**

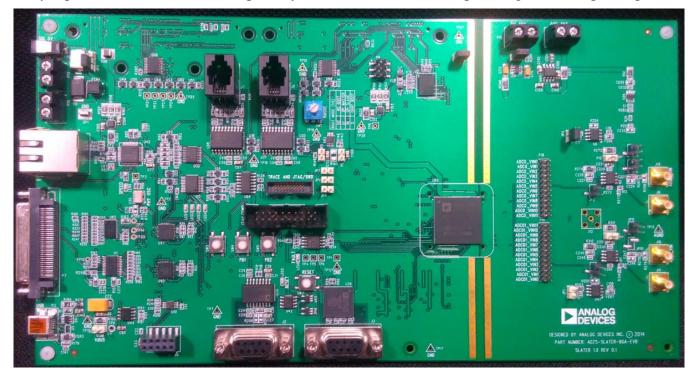

Based on the recommendations and guidelines described in this EE-note, two boards were designed for internal evaluation of the ADC, one around the ADSP-CM409 BGA package and one around the ADSP-CM408 LQFP package. The following sections provide some important layout details for each.

#### **ADSP-CM409F BGA Verification Board**

<u>Figure 9</u> shows an example of effective partitioning that places analog components and associated circuitry on the right side of the PCB and digital circuitry on the left. The analog ground (AGND) and digital ground (DGND) planes are separated by a pair of copper strips. In this fashion, the analog and digital circuitry are totally separated, and traces can be separately routed underneath the respective ground and power planes.

Figure 9. ADSP-CM409F BGA Evaluation Board

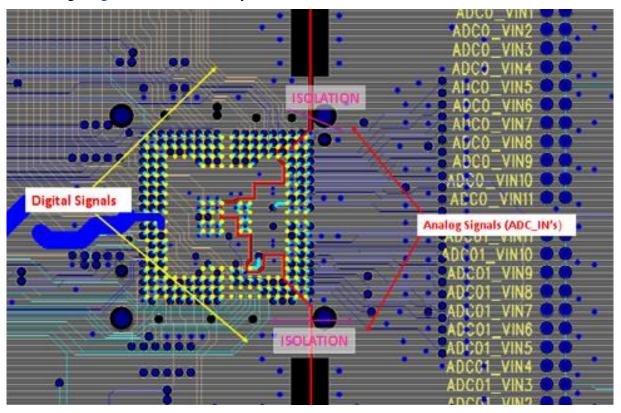

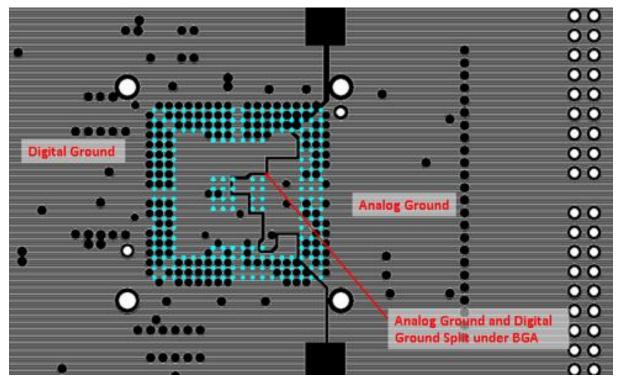

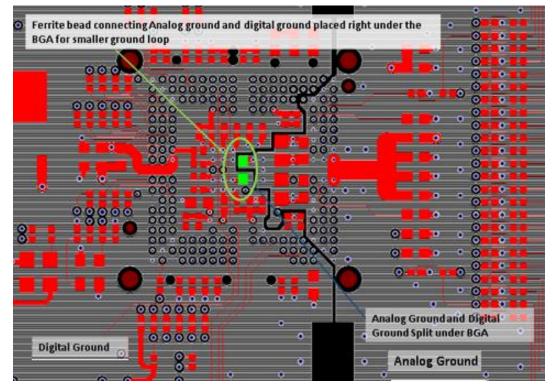

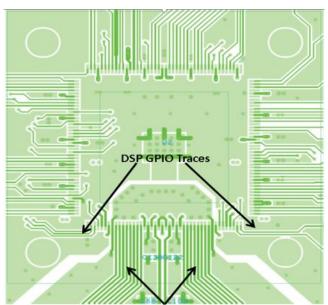

Figure 10 through Figure 13 show some layout schematics for this board.

Figure 10. Spacing between Analog and Digital Signals

Figure 11. Analog and Digital Ground-Splitting Technique

Both the analog and digital ground planes must be tied together at one point through a low-impedance bridge or, preferably, a ferrite bead (as shown in Figure 12).

Figure 12. Analog and Digital Grounds Tied Together through a Ferrite Bead

Figure 13. Recommended Placement of Reference Capacitors (as Close to Pin as Possible)

### **ADSP-CM408 LQFP Verification Board**

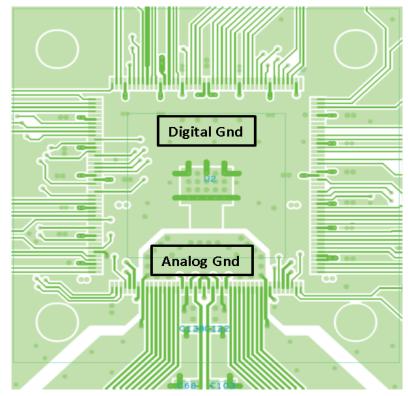

<u>Figure 14</u> shows the partitioning between the analog and digital circuitry on the ADSP-CM408 LQFP evaluation board. In this design as well, the analog (AGND) and digital (DGND) ground planes are separated by a pair of copper strips, such that the analog and digital circuitry are isolated and traces can be separately routed underneath the respective ground and power planes.

Figure 14. ADSP-CM408F LQFP Evaluation Board

Figure 15 shows isolation between the analog and digital I/O traces. The analog inputs are shielded with analog ground on both sides.

Figure 15. Spacing Between Analog and Digital Signal Traces

<u>Figure 16</u> shows the split-ground-plane technique that is used to separate the analog and digital grounds. Both grounds are shorted at the supply source, similar to a star connection.

Figure 16. Analog and Digital Ground-Plane-Splitting Technique

# **Test Setup**

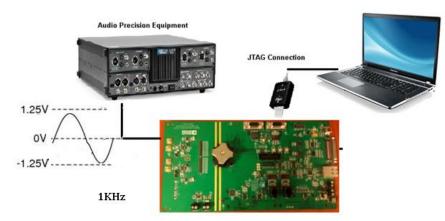

To measure the ADC performance on these evaluation boards, the set-up shown in Figure 17 was used.

Figure 17. Test Setup to Measure ADC Performance

The Audio Precision Equipment was used to generate a clean 1kHz sine wave with a 2.5Vpp amplitude and a THD+N > 105dB spec. This signal was fed into one of the input channels of the ADSP-CM40xF processor, which samples this ADC input at a rate of 2.631 MSPS<sup>[3]</sup>. Once the required ADC samples were collected, they were processed to calculate the dynamic performance of the ADC.

#### Results

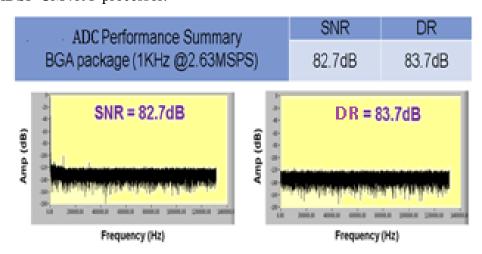

The observed ADC performance matched expectations, even with escalated digital activity from the processor where the M4 core was performing floating-point complex math operations while all the peripherals were enabled with high-speed I/O switching activity. Testing was then duplicated on all the available channels of the ADCs with consistent results. Figure 18 shows the SNR and Dynamic Range (DR) results for the ADSP-CM409F processor.

Figure 18. Dynamic Performance of ADC

ADC performance in the BGA package was best, as there was a minor degradation of up to 2dB in SNR observed using the LQFP package (which still results in 13.1 ENOB). That notwithstanding, these experiments show that proper board design techniques can yield the best ADC performance even with high digital activity in an ADSP-CM40xF mixed-signal processor system.

#### References

- [1] ADSP-CM40x ARM Cortex-M4 Mixed-Signal Control Processor Data Sheet. Rev A, October 2015. Analog Devices, Inc.

- [2] Front-End Amplifier and RC Filter Design for a Precision SAR Analog-to-Digital Converter. Analog Dialog Volume 46, December 2012. Analog Devices, Inc.

- [3] Maximizing ADC Sampling Rate on ADSP-CM40x Mixed-Signal Control Processors (EE-365). Rev 1, September 20, 2013. Analog Devices, Inc.

# Readings

- [4] ADSP-CM40x Mixed-Signal Control Processor with ARM Cortex-M4 Hardware Reference. Rev 1.0, November 2015. Analog Devices, Inc.

- [5] The Data Conversion Handbook. March 2004. Analog Devices, Inc.

# **Document History**

| Revision                                                            | Description     |

|---------------------------------------------------------------------|-----------------|

| Rev 1 – December 9, 2015 by<br>Prashant Gawade and Kritika<br>Shahu | Initial Release |