One Technology Way • P.O. Box 9106 • Norwood, MA 02062-9106, U.S.A. • Tel: 781.329.4700 • Fax: 781.461.3113 • www.analog.com

### Evaluation Board for a 20-Bit Serial Input, Voltage Output DAC with Integrated Precision Reference Buffer Amplifiers

#### FEATURES

Full-featured evaluation board for the AD5790

Link options

PC control in conjunction with Analog Devices, Inc., system demonstration platform

PC software for control

#### **EVALUATION BOARD DESCRIPTION**

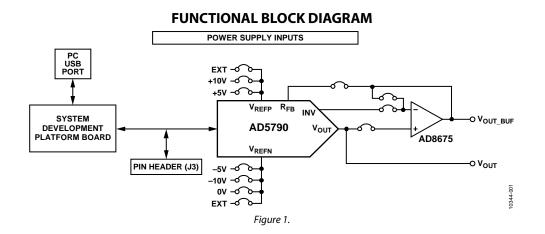

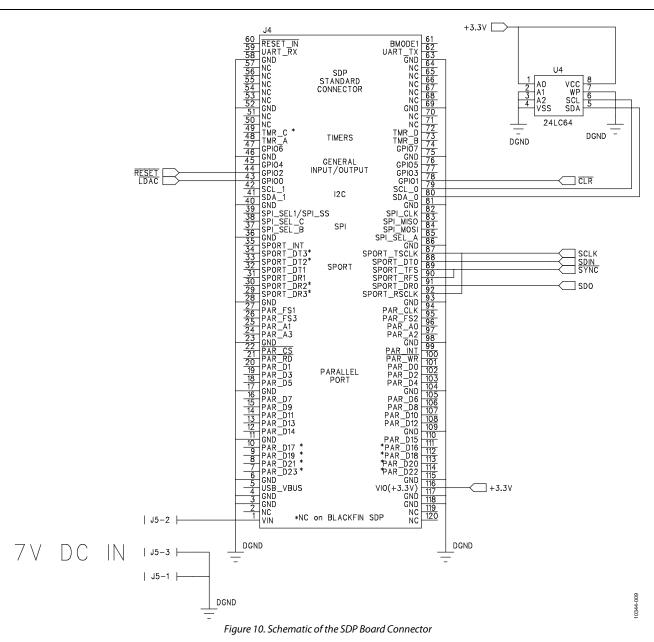

The EVAL-AD5790SDZ is a full-featured evaluation board, designed to allow the user to easily evaluate all features of the AD5790 voltage output, 20-bit digital-to-analog converter (DAC). The AD5790 pins are accessible at on-board connectors for external connection. The board can be controlled by two means: via the on-board connector (J3), or via the system demonstration platform (SDP) connector (J4). The SDP board allows the evaluation board to be controlled through the USB port of a Windows<sup>®</sup> XP (SP2 or later) or more recent 32-bit or 64-bit (Vista, Windows 7) PC using the AD5790 evaluation software.

#### **DEVICE DESCRIPTION**

The AD5790 is a high precision, 20-bit DAC with integrated precision reference buffer amplifiers designed to meet the requirements of precision control applications. The output range of the AD5790 is configured by two reference voltage inputs. The device is specified to operate with a dual power supply of up to 33 V.

Complete specifications for the AD5790 are provided in the AD5790 data sheet, available from Analog Devices, and should be consulted in conjunction with this user guide when using the evaluation board.

## TABLE OF CONTENTS

| Features                     | 1 |

|------------------------------|---|

| Evaluation Board Description | 1 |

| Device Description           | 1 |

| Functional Block Diagram     | 1 |

| Revision History             | 2 |

| Evaluation Board Hardware    | 3 |

| Power Supplies               | 3 |

| Link Options                 | 3 |

#### **REVISION HISTORY**

| 2/13—Rev. 0 to Rev. A                                    |   |

|----------------------------------------------------------|---|

| Changes to Table 2                                       | 3 |

| Replaced Evaluation Board Schematics and Artwork Section | 8 |

| Changes to Table 41                                      | 4 |

#### 11/11—Revision 0: Initial Version

| On-Board Connectors                     | 3  |

|-----------------------------------------|----|

| Evaluation Board Software               | 5  |

| Software Installation                   | 5  |

| Software Operation                      | 5  |

| Main Window                             | 6  |

| Evaluation Board Schematics and Artwork | 8  |

| Ordering Information                    | 14 |

| Bill of Materials                       | 14 |

### **EVALUATION BOARD HARDWARE** POWER SUPPLIES

The following external supplies must be provided:

- 5 V between the V<sub>CC</sub> and DGND inputs for the digital supply of the AD5790. Alternatively, place Link 1 in Position A to power the digital circuitry from the USB port via the SDP board (default).

- 7.5 V to 16.5 V between the V<sub>DD</sub> and AGND inputs for the positive analog supply of the AD5790.

- -2.5 V to -16.5 V between the V<sub>ss</sub> and AGND inputs for the negative analog supply of the AD5790.

The analog and digital planes are connected at one location, close to the AD5790. To avoid ground loop problems, it is recommended not to connect AGND and DGND elsewhere in the system.

Each supply is decoupled to the relevant ground plane with 10  $\mu F$  and 0.1  $\mu F$  capacitors. Each device supply pin is again decoupled with a 10  $\mu F$  and 0.1  $\mu F$  capacitor pair to the relevant ground plane.

#### LINK OPTIONS

The link options on the evaluation board should be set for the required operating setup before using the board. The functions of the link options are described in Table 3.

#### **Default Link Option Setup**

The default link options are listed in Table 1. By default, the board is configured with  $V_{REFP} = +10$  V and  $V_{REFN} = -10$  V for a ±10 V output range.

#### Table 1. Default Link Options

| Link No. | Option   |

|----------|----------|

| LK1      | A        |

| LK2      | В        |

| LK3      | A        |

| LK4      | Removed  |

| LK5      | Removed  |

| LK6      | Removed  |

| LK7      | Removed  |

| LK8      | С        |

| LK9      | Inserted |

| LK11     | Inserted |

#### **Connector J3 Pin Configuration**

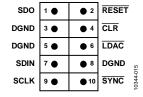

Figure 2 shows the pin configuration of Connector J3.

Figure 2. Connector J3 Pin Configuration

#### **ON-BOARD CONNECTORS**

There are nine connectors on the AD5790 evaluation board PCB as outlined in Table 2.

#### Table 2. On-Board Connectors

| Connector | Function                                                                                                                                                    |

|-----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|

| J1        | Digital power supply connector                                                                                                                              |

| J2        | Analog power supply connector                                                                                                                               |

| J3        | Digital interface pin header connector                                                                                                                      |

| J4        | SDP board connector                                                                                                                                         |

| VOUT      | DAC output connector                                                                                                                                        |

| VOUT_BUF  | Buffered DAC output connector                                                                                                                               |

| VREF      | 5 V external reference voltage input connector<br>(+10 V, +5 V, -10 V, and -5 V reference voltages are<br>generated from this 5 V input or on-board ADR4550 |

| VREFN     | DAC negative reference input connector                                                                                                                      |

| VREFP     | DAC positive reference input connector                                                                                                                      |

#### Table 3. Link Options

| Link No. | Description                                                                                                                                                                          |  |  |

|----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| LK1      | This link selects the source of the digital power supply.                                                                                                                            |  |  |

|          | Position A selects the source from the SDP board.                                                                                                                                    |  |  |

|          | Position B selects the source from Connector J1.                                                                                                                                     |  |  |

| LK2      | This link selects the positive reference voltage source.                                                                                                                             |  |  |

|          | Position A selects an on-board generated 5 V.                                                                                                                                        |  |  |

|          | Position B selects an on-board generated 10 V.                                                                                                                                       |  |  |

|          | Position C selects an external voltage applied at Connector VREFP.                                                                                                                   |  |  |

| LK3      | This link is used in conjunction with LK4 to configure the mode of operation of the output amplifier.                                                                                |  |  |

|          | Position A configures the amplifier in unity gain. LK4 should be removed. <sup>1</sup>                                                                                               |  |  |

|          | Position B configures the amplifier for a gain of 2. Lk4 should be inserted. <sup>2</sup>                                                                                            |  |  |

| LK4      | This link is used in conjunction with LK3 to configure the mode of operation of the output amplifier.                                                                                |  |  |

|          | When this link is inserted, LK3 should be in Position B to configure the amplifier for a gain of 2. <sup>2</sup>                                                                     |  |  |

|          | When this link is removed, LK3 should be in Position A to configure the amplifier for unity gain. <sup>1</sup>                                                                       |  |  |

| LK5      | This link selects the state of the RESET pin.                                                                                                                                        |  |  |

|          | When this link is inserted, RESET is at logic low.                                                                                                                                   |  |  |

|          | When this link is removed, RESET is at logic high.                                                                                                                                   |  |  |

| LK6      | This link selects the state of the CLR pin.                                                                                                                                          |  |  |

|          | When this link is inserted, $\overline{\text{CLR}}$ is at logic low.                                                                                                                 |  |  |

|          | When this link is removed, CLR is at logic high.                                                                                                                                     |  |  |

| LK7      | This link selects the state of the LDAC pin.                                                                                                                                         |  |  |

|          | When this link is inserted, LDAC is at logic low.                                                                                                                                    |  |  |

|          | When this link is removed, LDAC is at logic high.                                                                                                                                    |  |  |

| LK8      | This link selects the negative reference voltage source.                                                                                                                             |  |  |

|          | Position A selects an on-board generated –5 V.                                                                                                                                       |  |  |

|          | Position B selects AGND.                                                                                                                                                             |  |  |

|          | Position C selects an on-board generated –10 V.                                                                                                                                      |  |  |

|          | Position D selects an external voltage applied at Connector VREFN.                                                                                                                   |  |  |

| LK9      | This link connects the output of Voltage Reference U5 to the reference scaling circuitry.                                                                                            |  |  |

| LK11     | This link connects the DAC output to the noninverting input of the output buffer amplifier.                                                                                          |  |  |

|          | When this link is inserted, the DAC output is connected to the noninverting input of the output amplifier.                                                                           |  |  |

|          | When this link is removed, the DAC output is disconnected from the noninverting input of the output buffer amplifier and the DAC output voltage is accessible at the VOUT connector. |  |  |

<sup>1</sup> The RBUF bit of the control register must be set to high to enable the unity-gain mode of operation. <sup>2</sup> The RBUF bit of the control register must be cleared to low to enable the gain of 2 mode of operation.

### **EVALUATION BOARD SOFTWARE** SOFTWARE INSTALLATION

The AD5790 evaluation kit includes self-installing software on a CD. The software is compatible with Windows XP (SP2) and Vista (32-bit or 64-bit). If the setup file does not run automatically, you can run the **setup.exe** file from the CD.

Install the evaluation software before connecting the evaluation board and SDP board to the USB port of the PC to ensure that the evaluation system is correctly recognized when connected to the PC.

- 1. After installation from the CD is complete, power up the AD5790 evaluation board as described in the Power Supplies section. Connect the SDP board (via either Connector A or Connector B) to the AD5790 evaluation board and then to the USB port of your PC using the supplied cable.

- 2. When the evaluation system is detected, proceed through any dialog boxes that appear. This completes the installation.

#### SOFTWARE OPERATION

To launch the software, complete the following steps:

- 1. From the **Start** menu, select **Analog Devices**, **AD5790**, then **AD5790 Evaluation Software**. The main window of the software then opens (see Figure 4).

- 2. If the evaluation system is not connected to the USB port when the software is launched, a connectivity error displays (see Figure 3). Connect the evaluation board to the USB port of the PC, wait a few seconds, click **Rescan**, and follow the instructions.

| B Hardware Select |              |  |  |

|-------------------|--------------|--|--|

|                   |              |  |  |

| Previous Next Se  | elect Cancel |  |  |

Figure 3. Connectivity Error Alert

| Amplifiere Paul  | PINIA                      | Lip Converso                                                               |

|------------------|----------------------------|----------------------------------------------------------------------------|

| AD5790           |                            | al Input, Voltage Output DAC with integrated<br>eference buffer amplifiers |

| Configure Progra | m Voltage Measure DAC O    | utput                                                                      |

| Contr            | rol Register               | 50005 NH/25 DACIN 01500 NDF                                                |

|                  | Clearcode Regis            | ter 📜                                                                      |

| Sof              | ftware Control<br>Register | 0 0 0                                                                      |

| Ha               | rdware Control             |                                                                            |

|                  | DAC Register               | Å.<br>•                                                                    |

|                  | LIN COMP                   | ).C                                                                        |

|                  |                            |                                                                            |

|                  | _                          | 5109                                                                       |

Figure 4. Main Window

### UG-342

#### MAIN WINDOW

The main window is divided into three tabs: **Configure**, **Program Voltage**, and **Measure DAC Output**.

#### Configure

The **Configure** section allows access to the control register, clearcode register, software control register, and DAC register and allows control of the RESET, CLR, and LDAC pins.

#### Program Voltage

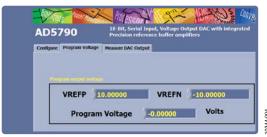

The **Program Voltage** section programs the DAC register with the value calculated from the entered values: the positive voltage reference (**VREFP**), the negative voltage reference (**VREFN**), and the desired output voltage (see Figure 5).

Figure 5. Program Voltage Window

#### Measure DAC Output

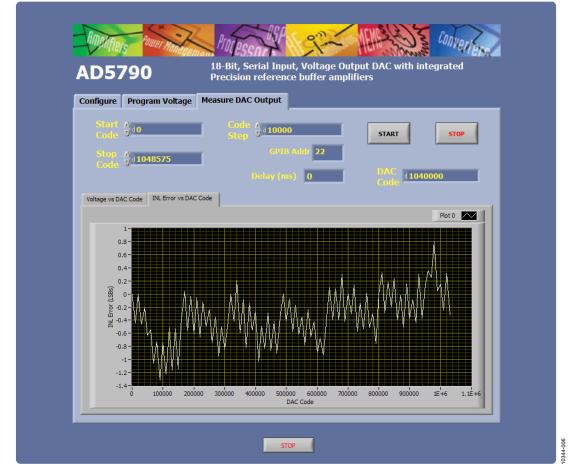

The **Measure DAC Output** section allows the PC to control an Agilent 3458A multimeter to measure and log the DAC output voltage.

The multimeter is controlled over a general-purpose interface bus (GPIB). When the multimeter is connected to the PC, first configure the multimeter via its front panel before taking a measurement. Figure 7 shows the measurement options. The software runs through a sequence of steps, programming the DAC register and measuring the DAC output voltage. The sequence begins with the software programming the DAC with the **Start Code** value, incrementing the programmed value at each step by the **Code Step** value, and finishing when the programmed value reaches the **Stop Code** value. A delay between measurements can be inserted, if required. The GPIB address of the multimeter must be specified. To begin the measurement, click **START**. The measurement can be halted at any time by clicking **STOP**. When the measurement is completed, a dialog box opens to allow you to save the data as a spreadsheet file with three columns of data. The first column is the DAC code, the second column is the DAC voltage in volts, and the third column is the INL error in LSBs, as shown in Figure 6. A graph of both the DAC output voltage vs. the DAC code and the INL error vs. the DAC code is displayed in the **Measure DAC Output** tab (see Figure 7). In the measurement example shown in Figure 7, measurements are taken in 10000 code steps beginning at Code 0 and finishing at Code 1,048,575 in a total of 100 measurements. With the number of power line cycles (NPLC) setting on the multimeter set to 1, the measurement takes ~10 sec to complete. To complete an all codes measurement requiring 1,048,575 measurement points takes ~1 day.

|    | А     | В        | С        |

|----|-------|----------|----------|

| 1  | 0     | -9.9983  | 0        |

| 2  | 1024  | -9.92018 | -0.01316 |

| 3  | 2048  | -9.84206 | -0.01866 |

| 4  | 3072  | -9.76394 | 0.010392 |

| 5  | 4096  | -9.68582 | -0.02197 |

| 6  | 5120  | -9.6077  | 0.007083 |

| 7  | 6144  | -9.52958 | 0.016931 |

| 8  | 7168  | -9.45146 | 0.013356 |

| 9  | 8192  | -9.37334 | 0.028971 |

| 10 | 9216  | -9.29522 | 0.040746 |

| 11 | 10240 | -9.2171  | 0.058275 |

| 12 | 11264 | -9.13898 | 0.043191 |

| 13 | 12288 | -9.06086 | 0.066475 |

| 14 | 13312 | -8.98274 | 0.060986 |

Figure 6. Saved Data Format

0344-005

If an Agilent 3458A multimeter is not connected to the PC, the software steps through the codes without taking any measurements.

# UG-342

Figure 7. Measure DAC Output Tab

Rev. A | Page 8 of 16

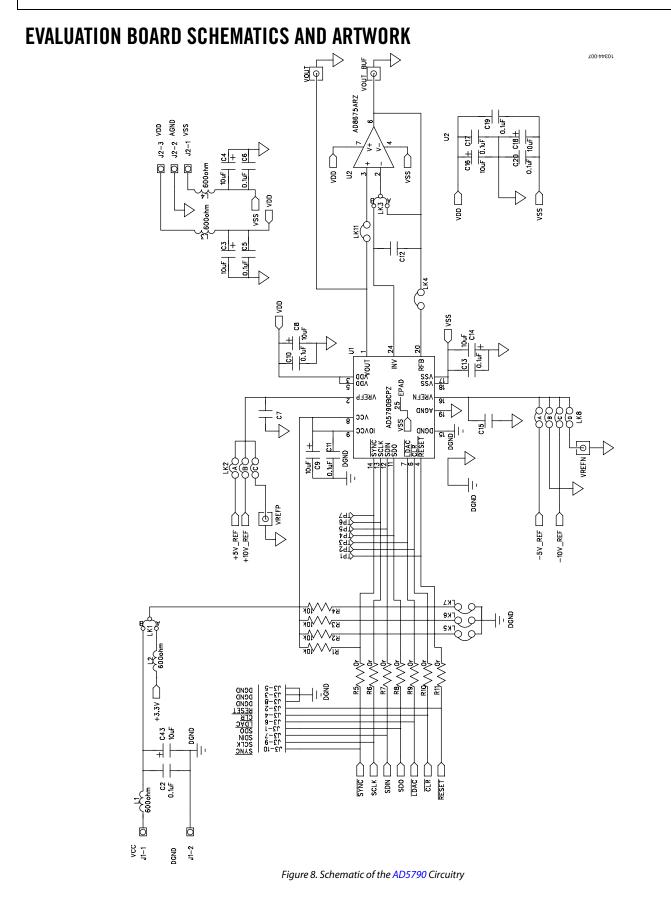

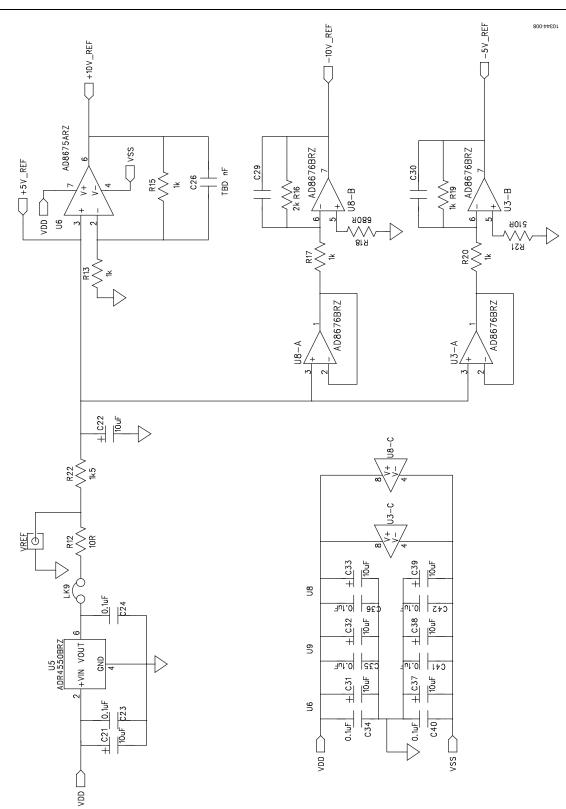

Figure 9. Schematic of the Voltage Reference Circuitry

UG-342

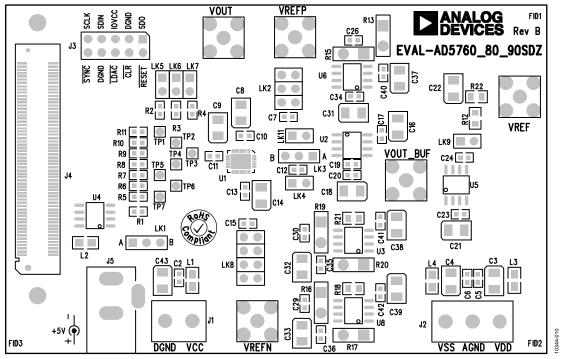

Figure 11. Component Placement Schematic

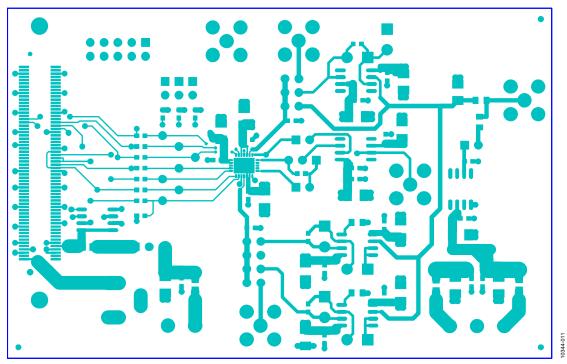

Figure 12. Top Printed Circuit Board (PCB) Layer Schematic

### UG-342

UG-342

### **Evaluation Board User Guide**

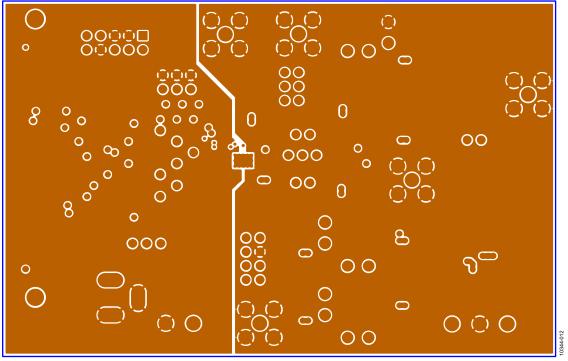

Figure 13. Inner First PCB Layer Schematic

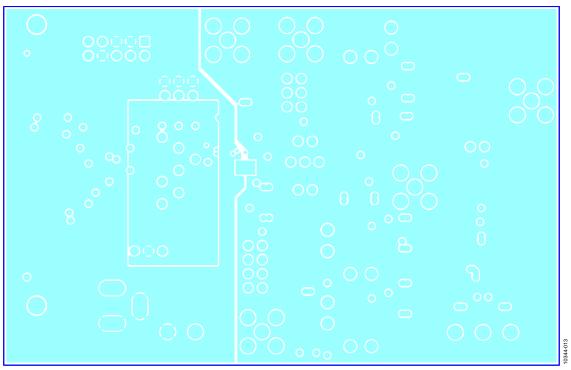

Figure 14. Inner Second PCB Layer Schematic

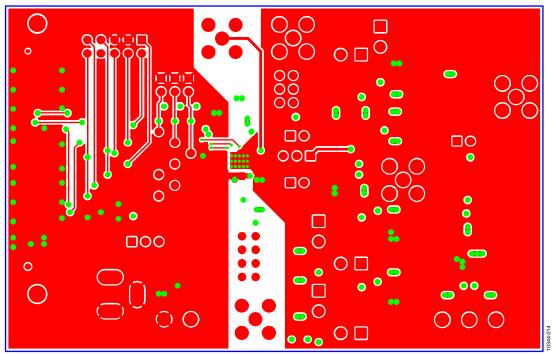

Figure 15. Bottom PCB Layer Schematic

## **ORDERING INFORMATION**

### **BILL OF MATERIALS**

#### Table 4.

| Reference Designator                                                             | Part Description                                       | Part Number              | Stock Code                                |

|----------------------------------------------------------------------------------|--------------------------------------------------------|--------------------------|-------------------------------------------|

| C2, C5, C6, C10, C11, C13,<br>C17, C19, C20, C23, C24, C34<br>to C36, C40 to C42 | Capacitor, 0603, 0.1 μF, 16 V                          | CM105X7R104K16AT         | FEC 9406140                               |

| C3, C4, C8, C9, C14, C16, C18,<br>C21, C22, C31, C32, C33, C37<br>to C39, C43    | Capacitor +, 10 μF, 16 V, 10%, Case B                  | TAJB106K016R             | FEC 498737                                |

| J1                                                                               | 2-pin terminal block (5 mm pitch)<br>CON\POWER         | CTB5000/2                | FEC 151789                                |

| J2                                                                               | 3-pin terminal block (5 mm pitch)<br>CON\POWER3        | CTB5000/3                | FEC 151790                                |

| J3                                                                               | 20-pin (2 × 10) header                                 | Not applicable           | FEC 1022244<br>(36 + 36-pin strip)        |

| J4                                                                               | 120-way connector, 0.6 mm pitch, SDP-<br>STANDARD-CONN | FX8-120S-SV(21)          | FEC 1324660                               |

| L1 to L4                                                                         | Ferrite bead IND                                       | 74279204                 | FEC 1635719                               |

| LK1, LK3                                                                         | 3-pin SIL header and shorting link                     | M20-9990345 and M7567-05 | FEC 1022248 and 150410                    |

| LK2                                                                              | 6-pin (3 $\times$ 2) 0.1" header and shorting block    | M20-9983646 and M7566-05 | FEC 148-535 and 150-411<br>(36-pin strip) |

| LK4 to LK7, LK9, LK11                                                            | 2-pin (0.1" pitch) header and shorting shunt           | M20-9990246              | FEC 1022247 and 150-411                   |

| LK8                                                                              | 8-pin (4 $\times$ 2) 0.1" header and shorting block    | M20-9983646 and M7566-05 | FEC 1022244 and 150-411<br>(36-pin strip) |

| R1 to R12                                                                        | SMD resistor                                           | MC 0.063W 0603 10k       | FEC 9331700                               |

| R13, R15, R17, R19, R20                                                          | Resistor, 1 kΩ, 0805, 5 ppm                            | PCF0805-13-1K-B-T1       | FEC 31108863                              |

| R16                                                                              | Resistor, 2 kΩ, 0805, 5 ppm                            | PCF0805-13-2K-B-T1       | FEC 1108872                               |

| R18                                                                              | Resistor, 0805, 680 Ω                                  | MC 0.1W 0805 5% 680R     | FEC 9334785                               |

| R21                                                                              | Resistor, 0805, 510 Ω                                  | MC 0.1W 0805 5% 510R     | FEC 9334637                               |

| R22                                                                              | Resistor, 0805, 1.5 kΩ                                 | MC 0.1W 0805 5% 1K5      | FEC 9333924                               |

| TP1 to TP7                                                                       | Red test point                                         | 20-2137                  | FEC 240-333                               |

| U1                                                                               | 20-bit DAC                                             | AD5790BCPZ               | AD5790BCPZ                                |

| U2, U6                                                                           | Single op amp                                          | AD8675ARZ                | AD8675ARZ                                 |

| U8, U9                                                                           | Dual op amp                                            | AD8676BRZ                | AD8676BRZ                                 |

| U4                                                                               | 64k I <sup>2</sup> C serial EEPROM                     | 24LC64-ISN               | FEC 9758070                               |

| U5                                                                               | 5 V reference                                          | ADR4550BRZ               | ADR4550BRZ                                |

| VOUT, VOUT_BUF, VREF,<br>VREFN, VREFP                                            | Straight PCB mount SMB jack, 50 $\Omega$               | 1-1337482-0              | FEC 1206013                               |

## NOTES

### NOTES

#### ESD Caution

ESD (electrostatic discharge) sensitive device. Charged devices and circuit boards can discharge without detection. Although this product features patented or proprietary protection circuitry, damage may occur on devices subjected to high energy ESD. Therefore, proper ESD precautions should be taken to avoid performance degradation or loss of functionality.

#### Legal Terms and Conditions

By using the evaluation board discussed herein (together with any tools, components documentation or support materials, the "Evaluation Board"), you are agreeing to be bound by the terms and conditions set forth below ("Agreement") unless you have purchased the Evaluation Board, in which case the Analog Devices Standard Terms and Conditions of Sale shall govern. Do not use the Evaluation Board until you have read and agreed to the Agreement. Your use of the Evaluation Board shall signify your acceptance of the Agreement. This Agreement is made by and between you ("Customer") and Analog Devices, Inc. ("ADI"), with its principal place of business at One Technology Way, Norwood, MA 02062, USA. Subject to the terms and conditions of the Agreement, ADI hereby grants to Customer a free, limited, personal, temporary, non-exclusive, non-sublicensable, non-transferable license to use the Evaluation Board FOR EVALUATION PURPOSES ONLY. Customer understands and agrees that the Evaluation Board is provided for the sole and exclusive purpose referenced above, and agrees not to use the Evaluation Board for any other purpose. Furthermore, the license granted is expressly made subject to the following additional limitations: Customer shall not (i) rent, lease, display, sell, transfer, assign, sublicense, or distribute the Evaluation Board; and (ii) permit any Third Party to access the Evaluation Board. As used herein, the term "Third Party" includes any entity other than ADI, Customer, their employees, affiliates and in-house consultants. The Evaluation Board is NOT sold to Customer; all rights not expressly granted herein, including ownership of the Evaluation Board, are reserved by ADL CONFIDENTIALITY. This Agreement and the Evaluation Board shall all be considered the confidential and proprietary information of ADL Customer may not disclose or transfer any portion of the Evaluation Board to any other party for any reason. Upon discontinuation of use of the Evaluation Board or termination of this Agreement, Customer agrees to promptly return the Evaluation Board to ADI. ADDITIONAL RESTRICTIONS. Customer may not disassemble, decompile or reverse engineer chips on the Evaluation Board. Customer shall inform ADI of any occurred damages or any modifications or alterations it makes to the Evaluation Board, including but not limited to soldering or any other activity that affects the material content of the Evaluation Board. Modifications to the Evaluation Board must comply with applicable law, including but not limited to the RoHS Directive. TERMINATION. ADI may terminate this Agreement at any time upon giving written notice to Customer. Customer agrees to return to ADI the Evaluation Board at that time. LIMITATION OF LIABILITY. THE EVALUATION BOARD PROVIDED HEREUNDER IS PROVIDED "AS IS" AND ADI MAKES NO WARRANTIES OR REPRESENTATIONS OF ANY KIND WITH RESPECT TO IT. ADI SPECIFICALLY DISCLAIMS ANY REPRESENTATIONS, ENDORSEMENTS, GUARANTEES, OR WARRANTIES, EXPRESS OR IMPLIED, RELATED TO THE EVALUATION BOARD INCLUDING, BUT NOT LIMITED TO, THE IMPLIED WARRANTY OF MERCHANTABILITY, TITLE, FITNESS FOR A PARTICULAR PURPOSE OR NONINFRINGEMENT OF INTELLECTUAL PROPERTY RIGHTS. IN NO EVENT WILL ADI AND ITS LICENSORS BE LIABLE FOR ANY INCIDENTAL, SPECIAL, INDIRECT, OR CONSEQUENTIAL DAMAGES RESULTING FROM CUSTOMER'S POSSESSION OR USE OF THE EVALUATION BOARD, INCLUDING BUT NOT LIMITED TO LOST PROFITS, DELAY COSTS, LABOR COSTS OR LOSS OF GOODWILL. ADI'S TOTAL LIABILITY FROM ANY AND ALL CAUSES SHALL BE LIMITED TO THE AMOUNT OF ONE HUNDRED US DOLLARS (\$100.00). EXPORT. Customer agrees that it will not directly or indirectly export the Evaluation Board to another country, and that it will comply with all applicable United States federal laws and regulations relating to exports. GOVERNING LAW. This Agreement shall be governed by and construed in accordance with the substantive laws of the Commonwealth of Massachusetts (excluding conflict of law rules). Any legal action regarding this Agreement will be heard in the state or federal courts having jurisdiction in Suffolk County, Massachusetts, and Customer hereby submits to the personal jurisdiction and venue of such courts. The United Nations Convention on Contracts for the International Sale of Goods shall not apply to this Agreement and is expressly disclaimed.

©2011–2013 Analog Devices, Inc. All rights reserved. Trademarks and registered trademarks are the property of their respective owners. UG10344-0-2/13(A)

www.analog.com

Rev. A | Page 16 of 16