|     | REVISIONS   |      |          |

|-----|-------------|------|----------|

| LTR | DESCRIPTION | DATE | APPROVED |

|     |             |      |          |

|     |             |      |          |

|     |             |      |          |

Prepared in accordance with ASME Y14.24

REV PAGE REV Vendor item drawing

|                                                  |     |   | REV                      | •                                                                                         |       |       |                      |     |     |      | PAG    | <b>E</b> 1                    | OF  | 17   |      |    |    |    |  |  |  |  |

|--------------------------------------------------|-----|---|--------------------------|-------------------------------------------------------------------------------------------|-------|-------|----------------------|-----|-----|------|--------|-------------------------------|-----|------|------|----|----|----|--|--|--|--|

|                                                  |     | - | ZE<br>A                  | COD                                                                                       | E IDE | 162   | o.<br><b>236</b>     |     |     | DWG  | G NO.  |                               | \   | /62  | 2/14 | 63 | 5  |    |  |  |  |  |

| Original date of drawing<br>YY MM DD<br>17-01-09 |     |   |                          | APP                                                                                       | ROVE  | ED BY | BY<br>Thomas M. Hess |     |     |      |        | INTERFACE, MONOLITHIC SILICON |     |      |      |    |    |    |  |  |  |  |

|                                                  |     |   | CHECKED BY Phu H. Nguyen |                                                                                           |       |       | NAI                  | ROC | AC+ | WITH | 1 4 pp | EAR,<br>om/°C                 | REF | FERE | NCE  |    | ı. |    |  |  |  |  |

| PMIC N/A PREPARED BY Phu H. Nguyen               |     |   |                          | DLA LAND AND MARITIME<br>COLUMBUS, OHIO 43218-3990<br>http://www.landandmaritime.dla.mil/ |       |       |                      |     |     |      |        |                               |     |      |      |    |    |    |  |  |  |  |

| OF PAGES                                         |     |   | PAG                      | E                                                                                         |       | 1     | 2                    | 3   | 4   | 5    | 6      | 7 8 9 10 11 12 13 14 15 16 17 |     |      |      |    |    | 17 |  |  |  |  |

| REV STA                                          | TUS |   | REV                      | ,                                                                                         |       |       |                      |     |     |      |        |                               |     |      |      |    |    |    |  |  |  |  |

| PAGE                                             |     |   |                          |                                                                                           |       |       |                      |     |     |      |        |                               |     |      |      |    |    |    |  |  |  |  |

AMSC N/A 5962-V003-17

## 1. SCOPE

- 1.1 <u>Scope</u>. This drawing documents the general requirements of a high performance Quad, 16-Bit nanoDAC+ with 4 ppm/°C Reference, SPI interface microcircuit, with an operating temperature range of -55°C to +125°C.

- 1.2 <u>Vendor Item Drawing Administrative Control Number</u>. The manufacturer's PIN is the item of identification. The vendor item drawing establishes an administrative control number for identifying the item on the engineering documentation:

V62/14635

01

X

E

Drawing number

Device type (See 1.2.1)

Case outline (See 1.2.2)

Lead finish (See 1.2.3)

1.2.1 Device type(s).

Device type

Generic

O1

AD5686R –EP

Quad, 16-Bit nanoDAC+ with 4 ppm/°C Reference, SPI interface

1.2.2 <u>Case outline(s)</u>. The case outlines are as specified herein.

Outline letter

Number of pins

JEDEC PUB 95

Package style

X

16

JEDEC MO-220-WEED-6

Lead Frame Chip Scale Package

1.2.3 Lead finishes. The lead finishes are as specified below or other lead finishes as provided by the device manufacturer:

Finish designator

A Hot solder dip

B Tin-lead plate

C Gold plate

D Palladium

E Gold flash palladium

Z Other

| DLA LAND AND MARITIME | SIZE | CODE IDENT NO. | DWG NO.          |

|-----------------------|------|----------------|------------------|

| COLUMBUS, OHIO        | A    | <b>16236</b>   | <b>V62/14635</b> |

|                       |      | REV            | PAGE 2           |

# 1.3 Absolute maximum ratings. 1/

| V <sub>DD</sub> to GND                                                       | -0.3 V to +7 V                             |

|------------------------------------------------------------------------------|--------------------------------------------|

| V <sub>LOGIC</sub> to GND                                                    | -0.3 V to +7 V                             |

| Vout to GND                                                                  | $-0.3 \text{ V to V}_{DD} + 0.3 \text{ V}$ |

| V <sub>REF</sub> to GND                                                      | $-0.3 \text{ V to V}_{DD} + 0.3 \text{ V}$ |

| Digital Input Voltage to GND                                                 | -0.3 V to V <sub>LOGIC</sub> + 0.3 V       |

| Operating temperature range:                                                 | -55°C to +125°C                            |

| Storage temperature range                                                    | -65°C to 150°C                             |

| Junction temperature                                                         | 135°C                                      |

| Case outline X, θ <sub>JA</sub> Thermal Impedance, 0 Airflow (4-Layer Board) | 70°C/W                                     |

| Reflow Soldering Peak Temperature, Pb Free (J-STD-020)                       | 260°C                                      |

| Electrostatic Discharge Sensitivity (ESDS):                                  |                                            |

| HBM                                                                          | 4 kV                                       |

| FICDM                                                                        | 1.25 kV                                    |

### 2. APPLICABLE DOCUMENTS

# JEDEC - SOLID STATE TECHNOLOGY ASSOCIATION (JEDEC)

JEP95 – Registered and Standard Outlines for Semiconductor Devices

JEDEC J-STD-020 – Standard for moisture/reflow sensitivity classification for nonhermetric solid state surface mount devices. For electrostatic discharge sensitivity test Human Body Model (HBM) – component level.

JESD22-C101 — Field-Induced Charged-Device Model (FIDCM) Test Method for Electrostatic-Discharge-Withstand

Thresholds of Microelectronic Components

(Copies of these documents are available online at <a href="http://www.jedec.org">http://www.jedec.org</a> or from JEDEC – Solid State Technology Association, 3103 North 10th Street, Suite 240–S, Arlington, VA 22201-2107).

| DLA LAND AND MARITIME | SIZE | CODE IDENT NO. | DWG NO.          |

|-----------------------|------|----------------|------------------|

| COLUMBUS, OHIO        | A    | <b>16236</b>   | <b>V62/14635</b> |

|                       |      | REV            | PAGE 3           |

Stresses beyond those listed under "absolute maximum ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated under "recommended operating conditions" is not implied. Exposure to absolute maximum rated conditions for extended periods may affect device reliability.

### 3. REQUIREMENTS

- 3.1 <u>Marking</u>. Parts shall be permanently and legibly marked with the manufacturer's part number as shown in 6.3 herein and as follows:

- A. Manufacturer's name, CAGE code, or logo

- B. Pin 1 identifier

- C. ESDS identification (optional)

- 3.2 <u>Unit container</u>. The unit container shall be marked with the manufacturer's part number and with items A and C (if applicable) above.

- 3.3 <u>Electrical characteristics</u>. The maximum and recommended operating conditions and electrical performance characteristics are as specified in 1.3, 1.4, and table I herein.

- 3.4 <u>Design, construction, and physical dimension</u>. The design, construction, and physical dimensions are as specified herein.

- 3.5 Diagrams.

- 3.5.1 <u>Case outline</u>. The case outline shall be as shown in 1.2.2 and figure 1.

- 3.5.2 Terminal connections. The terminal connections shall be as shown in figure 2.

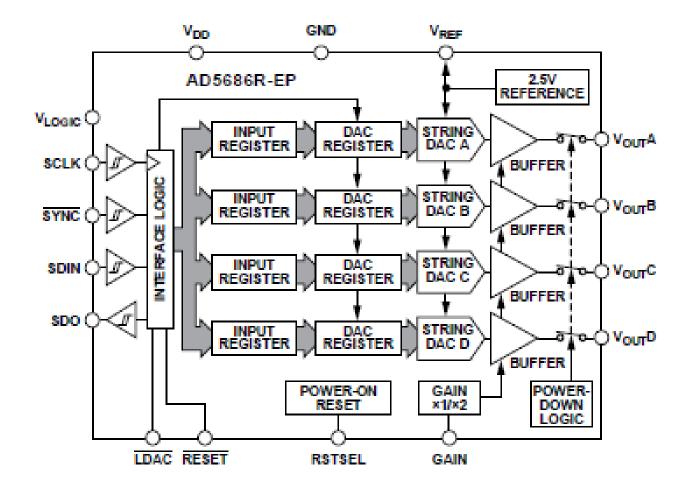

- 3.5.3 <u>Terminal function</u>. The terminal function shall be as shown in figure 3.

- 3.5.4 Functional block diagram. The functional block diagram shall be as shown in figure 4.

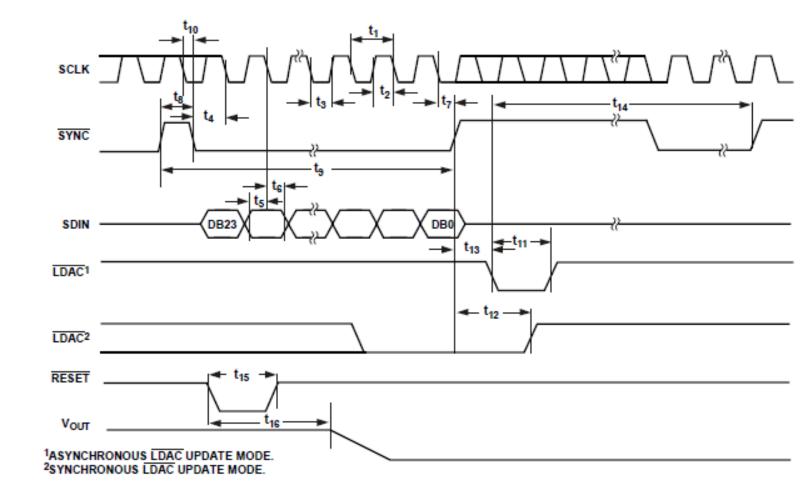

- 3.5.5 <u>Serial Write Operation</u>. The Serial Write Operation shall be as shown in figure 5.

- 3.5.6 <u>Load Circuit for Digital Output (SDO) Timing Specification</u>. The Load Circuit for Digital Output (SDO) Timing Specification shall be as shown in figure 6.

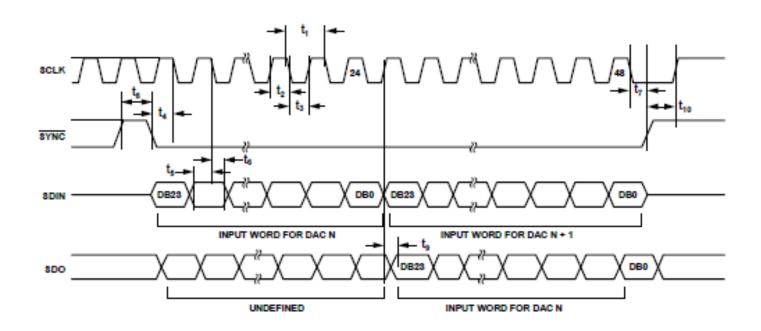

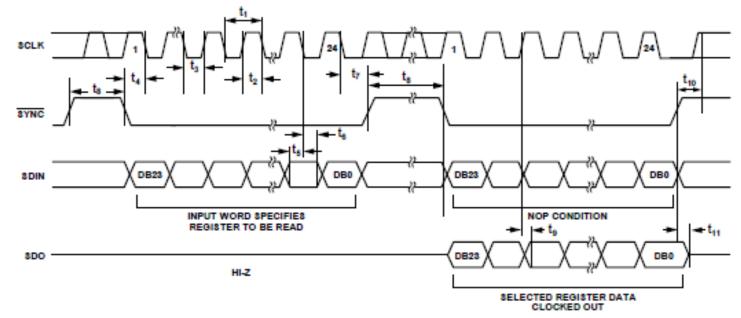

- 3.5.7 <u>Daisy-Chain Timing Diagram</u>. The Daisy-Chain Timing Diagram shall be as shown in figure 7.

- 3.5.8 Readback Timing Diagram. The Readback Timing Diagram shall be as shown in figure 8.

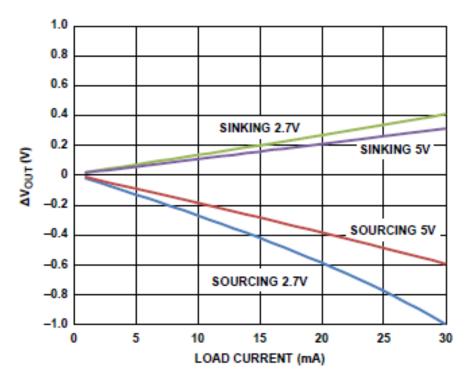

- 3.5.9 <u>Headroom/Footroom vs Load Current</u>. The Headroom/Footroom vs Load Current shall be as shown in figure 9.

| DLA LAND AND MARITIME | SIZE | CODE IDENT NO. | DWG NO.          |

|-----------------------|------|----------------|------------------|

| COLUMBUS, OHIO        | A    | <b>16236</b>   | <b>V62/14635</b> |

|                       |      | REV            | PAGE 4           |

TABLE I. Electrical performance characteristics. 1/

| Test                                       | Test conditions                                  |        | Limits |          | Unit     |

|--------------------------------------------|--------------------------------------------------|--------|--------|----------|----------|

|                                            | 2/                                               | Min    | Тур    | Max      |          |

| Static Performance 3/                      |                                                  |        |        |          |          |

| Resolution                                 |                                                  | 16     |        |          | Bits     |

| Relative Accuracy                          | Gain = 2                                         |        | ±1     | ±4       | LSB      |

| Troiding / local doy                       | Gain = 1                                         |        | ±1     | ±5       | LSB      |

| Differential Nonlinearity (DNL)            | Guaranteed monotonic by design                   |        |        | ±1       | LSB      |

| Zero-Code Error                            | All zeros loaded to DAC register                 |        | 0.4    | 1.5      | mV       |

| Offset Error                               |                                                  |        | ±0.1   | ±0.5     | mV       |

| Full-Scale Error                           | All ones loaded to DAC register                  |        | +0.01  | +0.1     | % of FSR |

| Gain Error                                 | Gain = 2                                         |        | ±0.02  | ±0.1     | % of FSR |

|                                            | Gain = 1                                         |        | ±0.02  | ±0.15    | % of FSR |

| Total Unadjusted Error                     | External reference; gain = 2                     |        | ±0.01  | ±0.1     | % of FSR |

| Total Chaquetea Eller                      | Internal reference; gain = 1                     |        |        | ±0.2     | % of FSR |

| Offset Error Drift 4/                      |                                                  |        | ±1     |          | μV/°C    |

| Gain Temperature Coefficient (TC) 4/       | Of FSR/°C                                        |        | ±1     |          | ppm      |

| DC Power Supply Rejection Ratio <u>4</u> / | DAC code = midscale, V <sub>DD</sub> = 5 V ± 10% |        | 0.15   |          | mV/V     |

|                                            | Due to single channel, full-scale output change  |        | ±2     |          | μV       |

| DC Crosstalk                               | Due to load current change                       |        | ±3     |          | μV/mA    |

|                                            | Due to powering down (per channel)               |        | ±2     |          | μV       |

| Output Characteristics <u>4</u> /          |                                                  |        |        |          |          |

| Output Voltage Range                       | Gain = 1                                         | 0      |        | Vref     | V        |

|                                            | Gain = 2, see Figure 9                           | 0      |        | 2 × Vref | V        |

| Capacitive Load Stability                  | R <sub>L</sub> = ∞                               |        | 2      |          | nF       |

|                                            | $R_L = 1 k\Omega$                                |        | 10     |          | nF       |

| Resistive Load <u>5</u> /                  |                                                  | 1      |        |          | kΩ       |

|                                            | V ± 10%, DAC code = midscale;                    |        | 80     |          | μV/mA    |

| Load Regulation                            | -30 mA ≤ Iо∪т ≤ 30 mA                            |        |        |          |          |

|                                            | 3 V ± 10%, DAC code = midscale;                  |        | 80     |          | μV/mA    |

|                                            | -20 mA ≤ Iо∪т ≤ 20 mA                            |        |        |          |          |

| Short-Circuit Current 6/                   |                                                  |        | 40     |          | mA       |

| Load Impedance at Rails 7/                 | See Figure 9                                     |        | 25     |          | Ω        |

| Power-Up Time                              | Coming out of power-down mode; VDD = 5 V         |        | 2.5    |          | μs       |

| Reference Output                           |                                                  | T      | 1      | Т        | 1        |

| Output Voltage <u>8</u> /                  | At ambient                                       | 2.4975 |        | 2.5025   | V        |

| Reference TC <u>9</u> / <u>10</u> /        |                                                  |        | 4      | 13       | ppm/°C   |

| Output Impedance 4/                        |                                                  |        | 0.04   |          | Ω        |

| Output Voltage Noise 4/                    | 0.1 Hz to 10 Hz                                  |        | 12     |          | μV p-p   |

| Output Voltage Noise Density               | At ambient; f = 10 kHz, C <sub>L</sub> = 10 nF   |        | 240    |          | nV/√Hz   |

| Load Regulation Sourcing 4/                | At ambient                                       |        | 20     |          | μV/mA    |

| Load Regulation Sinking 4/                 | At ambient                                       |        | 40     |          | μV/mA    |

| Output Current Load Capability             | V <sub>DD</sub> ≥ 3 V                            |        | ±5     |          | mA       |

| Line Regulation                            | At ambient                                       |        | 100    |          |          |

| DLA LAND AND MARITIME | SIZE | CODE IDENT NO. | DWG NO.          |

|-----------------------|------|----------------|------------------|

| COLUMBUS, OHIO        | A    | <b>16236</b>   | <b>V62/14635</b> |

|                       |      | REV            | PAGE 5           |

TABLE I.  $\underline{\text{Electrical performance characteristics}}$  - Continued.  $\underline{1}/$

| Test                                    | Test conditions                                                                 |                          | Limits |              | Unit |

|-----------------------------------------|---------------------------------------------------------------------------------|--------------------------|--------|--------------|------|

|                                         | <u>2</u> /                                                                      | Min                      | Тур    | Max          |      |

| Reference Output (Continued)            |                                                                                 |                          |        |              |      |

| Thermal Hysteresis 4/                   | First cycle                                                                     |                          | 125    |              | ppm  |

| Thermal Trystorosis <u>n</u>            | Additional cycles                                                               |                          | 25     |              | ppm  |

| Logic Inputs 4/                         |                                                                                 |                          |        |              |      |

| Input Current                           | Per pin                                                                         |                          |        | ±2           | μA   |

| Input Voltage                           |                                                                                 |                          |        |              |      |

| Low (V <sub>IN</sub> )                  |                                                                                 |                          |        | 0.3 × Vlogic | V    |

| High (V <sub>INH</sub> )                |                                                                                 | 0.7 × Vlogic             |        |              | V    |

| Pin Capacitance                         |                                                                                 |                          | 2      |              | pF   |

| Logic Outputs (SDO) 4/                  | •                                                                               |                          |        |              |      |

| Output Voltage                          |                                                                                 |                          |        |              |      |

| Low (VoL)                               | I <sub>SINK</sub> = 200 μA                                                      |                          |        | 0.4          | V    |

| High (Vон)                              | Isource = 200 µA                                                                | V <sub>LOGIC</sub> - 0.4 |        |              | V    |

| Floating State Output Capacitance       |                                                                                 |                          | 4      |              | pF   |

| Power Requirements                      |                                                                                 |                          |        |              |      |

| VLOGIC                                  |                                                                                 | 1.62                     |        | 5.5          | V    |

| I <sub>LOGIC</sub>                      |                                                                                 |                          |        | 3            | μΑ   |

| $V_{DD}$                                | Gain = 1                                                                        | 2.7                      |        | 5.5          | V    |

| $V_{DD}$                                | Gain = 2                                                                        | Vref + 1.5               |        | 5.5          | V    |

| I <sub>DD</sub>                         | $V_{IH} = V_{DD}$ , $V_{IL} = GND$ , $V_{DD} = 2.7 \text{ V to } 5.5 \text{ V}$ |                          |        |              |      |

| Normal Mode 11/                         | Internal reference off                                                          |                          | 0.59   | 0.7          | mΑ   |

| 110 110 110 110 110 110 110 110 110 110 | Internal reference on at full scale                                             |                          | 1.1    | 1.3          | mA   |

| All Power-Down Modes 12/                | -40°C to +85°C                                                                  |                          | 1      | 4            | μΑ   |

| _                                       | -55°C to +125°C                                                                 |                          |        | 6            | μA   |

| DLA LAND AND MARITIME | SIZE | CODE IDENT NO. | DWG NO.          |

|-----------------------|------|----------------|------------------|

| COLUMBUS, OHIO        | A    | <b>16236</b>   | <b>V62/14635</b> |

|                       |      | REV            | PAGE 6           |

TABLE I. <u>Electrical performance characteristics</u> - Continued. <u>1</u>/

| Test                                         | Test conditions                                  | Limits |      |     | Unit   |  |

|----------------------------------------------|--------------------------------------------------|--------|------|-----|--------|--|

|                                              |                                                  | Min    | Тур  | Max |        |  |

| AC Characteristics 13/ 14/ 15/               |                                                  |        |      |     |        |  |

| Output Voltage Settling Time                 | 1/4 to 3/4 scale settling to ±2 LSB              |        | 5    | 8   | μs     |  |

| Slew Rate                                    |                                                  |        | 0.8  |     | V/µs   |  |

| Digital-to-Analog Glitch Impulse             | 1 LSB change around major carry                  |        | 0.5  |     | nV-sec |  |

| Digital Feedthrough                          |                                                  |        | 0.13 |     | nV-sec |  |

| Digital Crosstalk                            |                                                  |        | 0.1  |     | nV-sec |  |

| Analog Crosstalk                             |                                                  |        | 0.2  |     | nV-sec |  |

| DAC-to-DAC Crosstalk                         |                                                  |        | 0.3  |     | nV-sec |  |

| Total Harmonic Distortion (THD) 16/          | At ambient, BW = 20 kHz, VDD = 5 V, fOUT = 1 kHz |        | -80  |     | dB     |  |

| Output Noise Spectral Density (NSD)          | DAC code = midscale, 10 kHz; gain = 2            |        | 300  |     | nV/√Hz |  |

| Output Noise                                 | 0.1 Hz to 10 Hz                                  |        | 6    |     | μV p-p |  |

| Signal-to-Noise Ratio (SNR)                  | At ambient, BW = 20 kHz, VDD = 5 V, fOUT = 1 kHz |        | 90   |     | dB     |  |

| Spurious Free Dynamic Range (SFDR)           | At ambient, BW = 20 kHz, VDD = 5 V, fOUT = 1 kHz |        | 83   |     | dB     |  |

| Signal-to-Noise-and-Distortion Ratio (SINAD) | At ambient, BW = 20 kHz, VDD = 5 V, fOUT = 1 kHz |        | 80   |     | dB     |  |

| DLA LAND AND MARITIME | SIZE | CODE IDENT NO. | DWG NO.          |

|-----------------------|------|----------------|------------------|

| COLUMBUS, OHIO        | A    | <b>16236</b>   | <b>V62/14635</b> |

|                       |      | REV            | PAGE 7           |

TABLE I. <u>Electrical performance characteristics</u> - Continued. <u>1</u>/

| Test                                                         | Symbol          | Test conditions |                         | Lim          | its                    |               | Unit |

|--------------------------------------------------------------|-----------------|-----------------|-------------------------|--------------|------------------------|---------------|------|

|                                                              |                 |                 | 1.62 V ≤ V <sub>L</sub> | ogic ≤ 2.7 V | 2.7 V ≤ V <sub>L</sub> | _ogic ≤ 5.5 V |      |

|                                                              |                 |                 | Min                     | Max          | Min                    | Max           |      |

| Timing Characteristics 17/ 18/ (See Figure 17)               | ure 5)          |                 |                         |              |                        |               |      |

| SCLK Cycle Time                                              | t <sub>1</sub>  |                 | 20                      |              | 20                     |               | ns   |

| SCLK High Time                                               | t <sub>2</sub>  |                 | 10                      |              | 10                     |               | ns   |

| SCLK Low Time                                                | t <sub>3</sub>  |                 | 10                      |              | 10                     |               | ns   |

| SYNC to SCLK Falling Edge Setup Time                         | t <sub>4</sub>  |                 | 15                      |              | 10                     |               | ns   |

| Data Setup Time                                              | <b>t</b> 5      |                 | 5                       |              | 5                      |               | ns   |

| Data Hold Time                                               | t <sub>6</sub>  |                 | 5                       |              | 5                      |               | ns   |

| SCLK Falling Edge to SYNC Rising Edge                        | t <sub>7</sub>  |                 | 10                      |              | 10                     |               | ns   |

| Minimum SYNC High Time                                       | t <sub>8</sub>  |                 | 20                      |              | 20                     |               | ns   |

| SYNC Rising Edge to SYNC Rising Edge (DAC Register Update/s) | t <sub>9</sub>  |                 | 870                     |              | 830                    |               | ns   |

| SYNC falling Edge to SCLK Fall Ignore                        | t <sub>10</sub> |                 | 16                      |              | 10                     |               | ns   |

| LDAC Pulse width low                                         | t <sub>11</sub> |                 | 15                      |              | 15                     |               | ns   |

| SYNC Rising Edge to LDAC Rising Edge                         | t <sub>12</sub> |                 | 20                      |              | 20                     |               | ns   |

| SYNC Rising Edge to LDAC Falling Edge                        | t <sub>13</sub> |                 | 30                      |              | 30                     |               | ns   |

| LDAC Falling Edge to SYNC Rising Edge                        | t <sub>14</sub> |                 | 840                     |              | 800                    |               | ns   |

| Minimum Pulse Width Low                                      | t <sub>15</sub> |                 | 30                      |              | 30                     |               | ns   |

| Pulse Activation time                                        | t <sub>16</sub> |                 | 30                      |              | 30                     |               | ns   |

| Power-Up Time 19/                                            |                 |                 | 4.5                     |              | 4.5                    |               | μs   |

| DLA LAND AND MARITIME | SIZE | CODE IDENT NO. | DWG NO.          |

|-----------------------|------|----------------|------------------|

| COLUMBUS, OHIO        | A    | <b>16236</b>   | <b>V62/14635</b> |

|                       |      | REV            | PAGE 8           |

TABLE I. <u>Electrical performance characteristics</u> - Continued. <u>1</u>/

| Test                                                                     | Symbol          | Test conditions |                         | Limits       |                        |              | Unit |

|--------------------------------------------------------------------------|-----------------|-----------------|-------------------------|--------------|------------------------|--------------|------|

|                                                                          |                 |                 | 1.62 V ≤ V <sub>L</sub> | ogic ≤ 2.7 V | 2.7 V ≤ V <sub>L</sub> | ogic ≤ 5.5 V |      |

|                                                                          |                 |                 | Min                     | Max          | Min                    | Max          |      |

| Daisy-Chain and Readback Timing Characteristics 20/ 21/ (See Figure 6-8) |                 |                 |                         |              |                        |              |      |

| SCLK Cycle Time                                                          | t <sub>1</sub>  |                 | 66                      |              | 40                     |              | ns   |

| SCLK High Time                                                           | t <sub>2</sub>  |                 | 33                      |              | 20                     |              | ns   |

| SCLK Low Time                                                            | t <sub>3</sub>  |                 | 33                      |              | 20                     |              | ns   |

| SYNC to SCLK Falling Edge                                                | t <sub>4</sub>  |                 | 33                      |              | 20                     |              | ns   |

| Data Setup Time                                                          | <b>t</b> 5      |                 | 5                       |              | 5                      |              | ns   |

| Data Hold Time                                                           | t <sub>6</sub>  |                 | 5                       |              | 5                      |              | ns   |

| SCLK Falling Edge to SYNC Rising Edge                                    | t <sub>7</sub>  |                 | 15                      |              | 10                     |              | ns   |

| Minimum SYNC High Time                                                   | t <sub>8</sub>  |                 | 60                      |              | 30                     |              | ns   |

| SDO Data Valid from SCLK Rising Edge                                     | t <sub>9</sub>  |                 |                         | 45           |                        | 30           | ns   |

| SYNC Rising Edge to SCLK Rising Edge                                     | t <sub>10</sub> |                 | 15                      |              | 10                     |              | ns   |

| SYNC Rising Edge to SDO Disable                                          | t <sub>11</sub> |                 | 60                      |              | 60                     |              | ns   |

| DLA LAND AND MARITIME | SIZE | CODE IDENT NO. | DWG NO.          |  |

|-----------------------|------|----------------|------------------|--|

| COLUMBUS, OHIO        | A    | <b>16236</b>   | <b>V62/14635</b> |  |

|                       |      | REV            | PAGE 9           |  |

## TABLE I. Electrical performance characteristics - Continued. 1/

- Testing and other quality control techniques are used to the extent deemed necessary to assure product performance over the specified temperature range. Product may not necessarily be tested across the full temperature range and all parameters may not necessarily be tested. In the absence of specific parametric testing, product performance is assured by characterization and/or design.

- 2/ V<sub>DD</sub> = 2.7 V to 5.5 V; 1.62 V ≤ V<sub>LOGIC</sub> ≤ 5.5 V; all specifications T<sub>MIN</sub> to T<sub>MAX</sub>, unless otherwise noted. R<sub>L</sub> = 2 k $\Omega$ ; C<sub>L</sub> = 200 pF.

- $\underline{3}$ / DC specifications tested with the outputs unloaded, unless otherwise noted. Upper dead band = 10 mV and exists only when  $V_{REF} = V_{DD}$  with gain = 1 or when  $V_{REF}/2 = V_{DD}$  with gain = 2. Linearity is calculated using a reduced code range of 256 to 65,280.

- 4/ Guaranteed by design, not subject to production test.

- 5/ Channel A can have an output current of up to 15 mA. Similarly, Channel B can have an output current of up to 15 mA, up to a junction temperature of 135°C.

- 6/ V<sub>DD</sub> = 5 V. The device includes current limiting that is intended to protect the device during temporary overload conditions. Junction temperature may be exceeded during current limit, but operation above the specified maximum operation junction temperature can impair device reliability.

- 7/ When drawing a load current at either rail, the output voltage headroom, with respect to that rail, is limited by the 25 Ω typical channel resistance of the output device. For example, when sinking 1 mA, the minimum output voltage = 25 Ω × 1 mA = 25 mV (see Figure 9).

- 8/ Initial accuracy presolder reflow is ±750 μV; output voltage includes the effects of preconditioning drift. See manufacturer data sheet AD5686R/AD5685R/AD5684R for more information.

- 9/ Reference is trimmed and tested at two temperatures and is characterized from -55°C to +125°C.

- <u>10</u>/ Reference temperature coefficient is calculated as per the box method. See manufacturer data sheet AD5686R/AD5685R/AD5684R for more information.

- 11/ Interface inactive. Both DACs active. DAC outputs unloaded.

- 12/ Both DACs powered down.

- 13/  $V_{DD} = 2.7 \text{ V to } 5.5 \text{ V}$ ;  $R_L = 2 \text{ k}\Omega$  to GND;  $C_L = 200 \text{ pF}$  to GND; 1.62  $V \le V_{LOGIC} \le 5.5 \text{ V}$ ; all specifications  $T_{MIN}$  to  $T_{MAX}$ , unless otherwise noted. Guaranteed by design and characterization; not production tested.

- 14/ Temperature range is −55°C to +125°C, typical at 25°C.

- 15/ See manufacturer data sheet AD5686R/AD5685R/AD5684R

- 16/ Digitally generated sine wave at 1 kHz.

- All input signals are specified with  $t_R = t_F = 1$  ns/V (10% to 90% of V<sub>DD</sub>) and timed from a voltage level of (V<sub>IL</sub> + V<sub>IH</sub>)/2. See Figure 5. V<sub>DD</sub> = 2.7 V to 5.5 V, 1.62 V  $\leq$  V<sub>LOGIC</sub>  $\leq$  5.5 V; V<sub>REF</sub> = 2.5 V. All specifications T<sub>MIN</sub> to T<sub>MAX</sub>, unless otherwise noted.

- <u>18</u>/ Maximum SCLK frequency is 50 MHz at V<sub>DD</sub> = 2.7 V to 5.5 V, 1.8 V ≤ V<sub>LOGIC</sub> ≤ V<sub>DD</sub>. Guaranteed by design and characterization; not production tested.

- 19/ Time to exit power-down to normal mode of AD5686R-EP operation, 32nd clock edge to 90% of DAC midscale value, with output unloaded.

- 20/ All input signals are specified with  $t_R = t_F = 1$  ns/V (10% to 90% of V<sub>DD</sub>) and timed from a voltage level of (V<sub>IL</sub> + V<sub>IH</sub>)/2. See Figure 7 and Figure 8. V<sub>DD</sub> = 2.7 V to 5.5 V, 1.62 V ≤ V<sub>LOGIC</sub> ≤ 5.5 V; V<sub>REF</sub> = 2.5 V. All specifications T<sub>MIN</sub> to T<sub>MAX</sub>, unless otherwise noted. V<sub>DD</sub> = 2.7 V to 5.5 V.

- 21/ Maximum SCLK frequency is 25 MHz or 15 MHz at V<sub>DD</sub> = 2.7 V to 5.5 V, 1.8 V ≤ V<sub>LOGIC</sub> ≤ V<sub>DD</sub>. Guaranteed by design and characterization; not production tested.

| DLA LAND AND MARITIME | SIZE     | CODE IDENT NO. | DWG NO. <b>V62/14635</b> |

|-----------------------|----------|----------------|--------------------------|

| COLUMBUS, OHIO        | <b>A</b> | <b>16236</b>   |                          |

|                       |          | REV            | PAGE 10                  |

## NOTES:

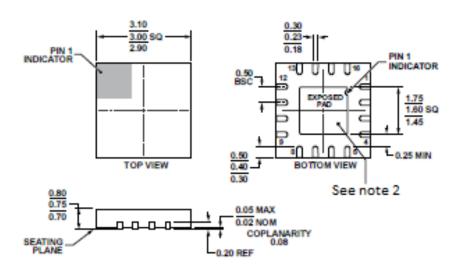

- 1. All linear dimensions are in millimeters.

- 2. For proper connection of the exposed PAD, refer to the pin configuration and function descriptions section on Figure 3.

- 3. Falls within JEDEC MO-220-WEED-6.

FIGURE 1. Case outline.

| Case outline X  |                    |                 |                    |  |  |  |

|-----------------|--------------------|-----------------|--------------------|--|--|--|

| Terminal number | Terminal symbol    | Terminal number | Terminal symbol    |  |  |  |

| 1               | VoutA              | 16              | VоитВ              |  |  |  |

| 2               | GND                | 15              | $V_{REF}$          |  |  |  |

| 3               | $V_{DD}$           | 14              | RSTSEL             |  |  |  |

| 4               | V <sub>OUT</sub> C | 13              | RESET              |  |  |  |

| 5               | VoutD              | 12              | SDIN               |  |  |  |

| 6               | SDO                | 11              | SYNC               |  |  |  |

| 7               | LDAC               | 10              | SCLK               |  |  |  |

| 8               | GAIN               | 9               | V <sub>LOGIC</sub> |  |  |  |

# NOTES:

- 1. The exposed PAD must be tied to GND.

- 2. NC = No Connect. Do not Connect to this PIN.

FIGURE 2. Terminal connections.

| DLA LAND AND MARITIME | SIZE | CODE IDENT NO. | DWG NO.          |

|-----------------------|------|----------------|------------------|

| COLUMBUS, OHIO        | A    | <b>16236</b>   | <b>V62/14635</b> |

|                       |      | REV            | PAGE 11          |

| Terminal<br>Number | Terminal<br>Symbol | Description                                                                                                                                                                                                                                                                                                                                           |

|--------------------|--------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1                  | V <sub>OUT</sub> A | Analog Output Voltage from DAC A. The output amplifier has rail-to-rail operation.                                                                                                                                                                                                                                                                    |

| 2                  | GND                | Ground Reference Point for All Circuitry on the device.                                                                                                                                                                                                                                                                                               |

| 3                  | $V_{DD}$           | Power Supply Input. The AD5686R-EP can be operated from 2.7 V to 5.5 V. Decouple the supply with a 10 $\mu$ F capacitor in parallel with a 0.1 $\mu$ F capacitor to GND.                                                                                                                                                                              |

| 4                  | VoutC              | Analog Output Voltage from DAC C. The output amplifier has rail-to-rail operation.                                                                                                                                                                                                                                                                    |

| 5                  | V <sub>OUT</sub> D | Analog Output Voltage from DAC D. The output amplifier has rail-to-rail operation.                                                                                                                                                                                                                                                                    |

| 6                  | SDO                | Serial Data Output. SDO can be used to daisy-chain a number of AD5686R-EP devices together, or it can be used for readback. The serial data is transferred on the rising edge of SCLK and is valid on the falling edge of the clock.                                                                                                                  |

| 7                  | LDAC               | <u>LDAC</u> can be operated in two modes, asynchronously and synchronously. Pulsing this pin low allows any or all DAC registers to be updated if the input registers have new data. This allows all DAC outputs to update simultaneously. This pin can also be tied permanently low.                                                                 |

| 8                  | GAIN               | Span Set Pin. When this pin is tied to GND, all four DAC outputs have a span from 0 V to VREF. If this pin is tied to VLOGIC, all four DACs output a span of 0 V to 2 x VREF.                                                                                                                                                                         |

| 9                  | V <sub>LOGIC</sub> | Digital Power Supply. Voltage ranges from 1.8 V to 5.5 V.                                                                                                                                                                                                                                                                                             |

| 10                 | SCLK               | Serial Clock Input. Data is clocked into the input shift register on the falling edge of the serial clock input. Data can be transferred at rates of up to 50 MHz.                                                                                                                                                                                    |

| 11                 | SYNC               | Active Low Control Input. This is the frame synchronization signal for the input data. When SYNC goes low, data is transferred in on the falling edges of the next 24 clocks.                                                                                                                                                                         |

| 12                 | SDIN               | Serial Data Input. This device has a 24-bit input shift register. Data is clocked into the register on the falling edge of the serial clock input.                                                                                                                                                                                                    |

| 13                 | RESET              | Asynchronous Reset Input. The $\overline{\text{RESET}}$ input is falling edge sensitive. When $\overline{\text{RESET}}$ is low, all $\overline{\text{LDAC}}$ pulses are ignored. When $\overline{\text{RESET}}$ activated, the input register and the DAC register are updated with zero scale or midscale, depending on the state of the RSTSEL pin. |

| 14                 | RSTSEL             | Power-On Reset Select. Tying this pin to GND powers up both DACs to zero scale. Tying this pin to VLOGIC powers up both DACs to midscale.                                                                                                                                                                                                             |

| 15                 | VREF               | Reference Voltage. The AD5686R-EP has a common reference pin. When using the internal reference, this is the reference output pin. When using an external reference, this is the reference input pin. The default for this pin is as a reference output.                                                                                              |

| 16                 | VоитВ              | Analog Output Voltage from DAC B. The output amplifier has rail-to-rail operation.                                                                                                                                                                                                                                                                    |

| 17                 | EPAD               | Exposed Pad. The exposed pad must be tied to GND.                                                                                                                                                                                                                                                                                                     |

FIGURE 3. <u>Terminal function</u>.

| DLA LAND AND MARITIME | SIZE | CODE IDENT NO. | DWG NO.          |  |

|-----------------------|------|----------------|------------------|--|

| COLUMBUS, OHIO        | A    | <b>16236</b>   | <b>V62/14635</b> |  |

|                       |      | REV            | PAGE 12          |  |

FIGURE 4. Functional block diagram.

| DLA LAND AND MARITIME | SIZE | CODE IDENT NO. | DWG NO.          |

|-----------------------|------|----------------|------------------|

| COLUMBUS, OHIO        | A    | <b>16236</b>   | <b>V62/14635</b> |

|                       |      | REV            | PAGE 13          |

FIGURE 5. <u>Serial Write Operation</u>.

| DLA LAND AND MARITIME | SIZE     | CODE IDENT NO. | DWG NO.          |

|-----------------------|----------|----------------|------------------|

| COLUMBUS, OHIO        | <b>A</b> | <b>16236</b>   | <b>V62/14635</b> |

|                       |          | REV            | PAGE 14          |

FIGURE 6. Load Circuit for Digital Output (SDO) Timing Specifications.

FIGURE 7. Daisy-Chain Timing Diagram.

| DLA LAND AND MARITIME | SIZE | CODE IDENT NO. | DWG NO.          |

|-----------------------|------|----------------|------------------|

| COLUMBUS, OHIO        | A    | <b>16236</b>   | <b>V62/14635</b> |

|                       |      | REV            | PAGE 15          |

FIGURE 8. Readback Timing Diagram.

FIGURE 9. Headroom/Footroom vs Load Current.

| DLA LAND AND MARITIME | SIZE     | CODE IDENT NO. | DWG NO.          |

|-----------------------|----------|----------------|------------------|

| COLUMBUS, OHIO        | <b>A</b> | <b>16236</b>   | <b>V62/14635</b> |

|                       |          | REV            | PAGE 16          |

### 4. VERIFICATION

4.1 <u>Product assurance requirements</u>. The manufacturer is responsible for performing all inspection and test requirements as indicated in their internal documentation. Such procedures should include proper handling of electrostatic sensitive devices, classification, packaging, and labeling of moisture sensitive devices, as applicable.

# 5. PREPARATION FOR DELIVERY

- 5.1 <u>Packaging</u>. Preservation, packaging, labeling, and marking shall be in accordance with the manufacturer's standard commercial practices for electrostatic discharge sensitive devices.

- 6. NOTES

- 6.1 ESDS. Devices are electrostatic discharge sensitive and are classified as ESDS class 1 minimum.

- 6.2 <u>Configuration control</u>. The data contained herein is based on the salient characteristics of the device manufacturer's data book. The device manufacturer reserves the right to make changes without notice. This drawing will be modified as changes are provided.

- 6.3 <u>Suggested source(s) of supply</u>. Identification of the suggested source(s) of supply herein is not to be construed as a guarantee of present or continued availability as a source of supply for the item. DLA Land and Maritime maintains an online database of all current sources of supply at <a href="https://landandmaritimeapps.dla.mil/programs/smcr/default.aspx">https://landandmaritimeapps.dla.mil/programs/smcr/default.aspx</a>

| Vendor item drawing administrative control number 1/ | Device<br>manufacturer<br>CAGE code | Ordering<br>Quantity       | Vendor part number |

|------------------------------------------------------|-------------------------------------|----------------------------|--------------------|

| V62/14635-01XE 24355                                 |                                     | Tray units = Not Available | AD5686R-EP         |

| V02/11000 01/AE 21000                                | 21000                               | Reel units= 1500           | AD5686RTCPZ-EP-RL7 |

1/ The vendor item drawing establishes an administrative control number for identifying the item on the engineering documentation.

CAGE code

Source of supply

24355

Analog Devices 1 Technology Way P.O. Box 9106 Norwood, MA 02062-9106

| DLA LAND AND MARITIME | SIZE | CODE IDENT NO. | DWG NO.          |

|-----------------------|------|----------------|------------------|

| COLUMBUS, OHIO        | A    | <b>16236</b>   | <b>V62/14635</b> |

|                       |      | REV            | PAGE 17          |