# Optimizing MOSFET Characteristics by Adjusting Gate Drive Amplitude

Steve Mappus

Power Supply Control

#### ABSTRACT

Most publications related to power supply gate drive highlight switching properties of the MOSFET and various methods that can be used to turn the devices on and off as efficiently as possible. One aspect often overlooked is the issue of gate drive voltage amplitude and the role it can play in overall power converter efficiency. The operating characteristics of a MOSFET change according to the amplitude of the gate drive pulse. As a result, trade-offs exist when considering one gate drive voltage level versus another. Although these principles can apply to most switching power supply topologies, a synchronous buck ia used as an application example. Graphs showing frequency and load current trade-offs present general MOSFET power loss equations. For discrete MOSFET gate drive circuits, driver ICs and PWM controllers, this methodology can apply to any power supply application with the capability to vary the gate drive voltage amplitude.

#### 1 Introduction

Power supply designers can sometimes gain additional efficiency increases by properly matching the gate drive voltage with the MOSFETs being driven. Driving a MOSFET gate with a higher voltage, results in a lower associated on-resistance, R<sub>DS(on)</sub>, up to a particular point of diminishing return. This can be extremely beneficial to low voltage high current VRM designs and control driven synchronous rectifiers found in many high current isolated power supply applications. In synchronous buck power applications, lowering the MOSFET on-resistance is especially critical for the synchronous rectifier, since in most cases the power loss due to the freewheeling current through the MOSFET channel resistance is the highest single contributor to total dissipated power. There are, however, additional factors to consider.

Higher gate drive voltage levels place additional charge into the gate-to-source junction of the MOSFET, resulting in increased losses within the MOSFET driver stage. In addition, a higher gate charge requirement will produce longer rise and fall times, which impact switching losses in the high-side MOSFET of a synchronous buck converter. To increase efficiency, the applied voltage should drive the MOSFET gates such that the added gate charge and switching losses are less than the power savings gained by lowering R<sub>DS(on)</sub>. For example, taking on an additional 0.5 W of power dissipated in the high-side MOSFET may be acceptable when 1 W of power is saved in the synchronous MOSFET.

1

Definition of Symbols and Abbreviations

#### 2 Definition of Symbols and Abbreviations

The following list of symbols and abbreviations are used throughout the application example of this article.

- D Duty Cycle

- Fsw Switching Frequency

- G1 Control MOSFET Gate Drive

- G2 Synchronous Rectifier MOSFET Gate Drive

- IG(sink) Driver Sink Current

- IG(source) Driver Source Current

- Iout Output Load Current

- L<sub>LUMP</sub> Driver to MOSFET Parasitic Inductance

- PBD Synchronous Rectifier MOSFET Body-Diode Power Loss

- Pc MOSFET Conduction Power Loss

- **P**<sub>D</sub> Total Dissipated Power (G1, Q1, G2, Q2)

- **P**<sub>OUT</sub> MOSFET Output Capacitance Loss

- P<sub>RR</sub> Synchronous Rectifier MOSFET Body-Diode Reverse Recovery Power Loss

- Psw MOSFET Switching Loss

- **Q**<sub>G</sub> Total Gate Charge

- **Q**<sub>RR</sub> Body-Diode Reverse Recovery Charge

- Q1 Control MOSFET

- Q2 Synchronous Rectifier MOSFET

- R<sub>DS(on)</sub> MOSFET Drain-to-Source On Resistance

- R<sub>G</sub> MOSFET External Discrete Gate Resistance

- R<sub>GI</sub> MOSFET Internal Gate Resistance

- R<sub>G1(sink)</sub> G1 Driver Sink Resistance

- RG1(source) G1 Driver Source Resistance

- R<sub>G2(sink)</sub> G2 Driver Sink Resistance

- R<sub>G2(source)</sub> G2 Driver Source Resistance

- t<sub>BDF</sub> MOSFET Body-Diode Conduction Time, Switch Node Falling

- t<sub>BDR</sub> MOSFET Body-Diode Conduction Time, Switch Node Rising

- t<sub>f</sub> MOSFET Turn OFF Fall Time

- tr MOSFET Turn On Rise Time

- V<sub>F</sub> MOSFET Body-Diode Forward Voltage Drop

- V<sub>GS</sub> Gate-to-Source Voltage

- V<sub>IN</sub> Input Voltage

V<sub>TH</sub> — MOSFET Turn On Threshold Voltage

Vout — Output Voltage

$\Delta \eta$  — Change in Overall Efficiency

# 3 Gate Drive Voltage Considerations

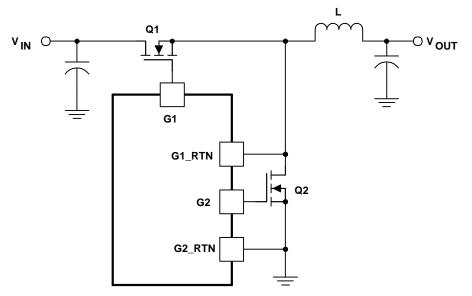

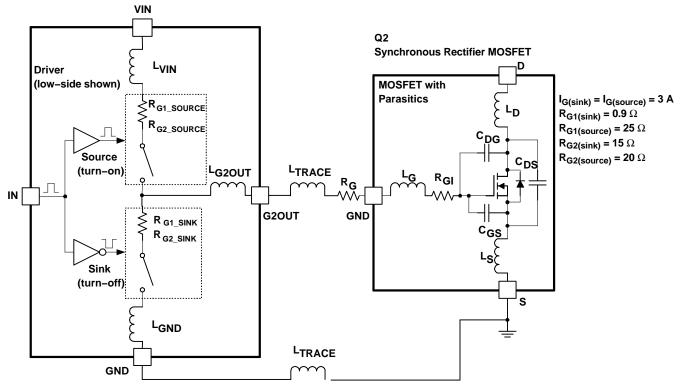

Driving the gates of control MOSFET Q1 and synchronous MOSFET Q2 (see Figure 1) with one voltage level verses another requires careful consideration. The need for additional discrete components, impact to the PCB routing, and the requirement of optimal drive voltage amplitudes that may or may not be readily available are all trade-offs to weigh against the potential efficiency savings from possibly lowering the MOSFET  $R_{DS(on)}$ .

Figure 1. Synchronous Buck Power and Driver Stage

As an example, consider the following analysis using arbitrary devices for the control MOSFET and synchronous rectifier MOSFET. In order to weigh the benefit of one gate-source voltage ( $V_{GS}$ ) versus another, the  $R_{DS(on)}$  versus gate drive voltage and gate drive voltage versus gate charge curves for each MOSFET must be carefully looked at.

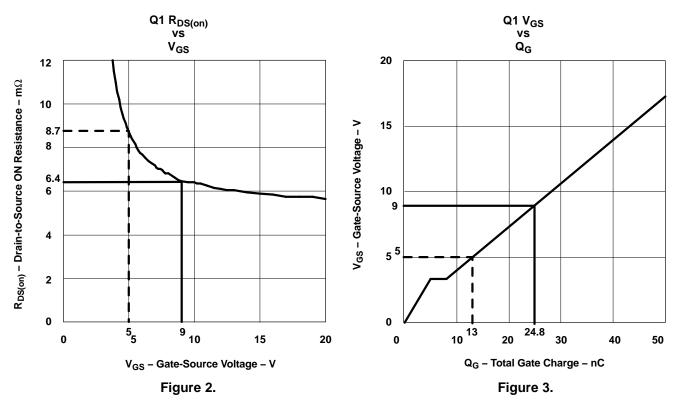

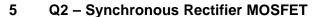

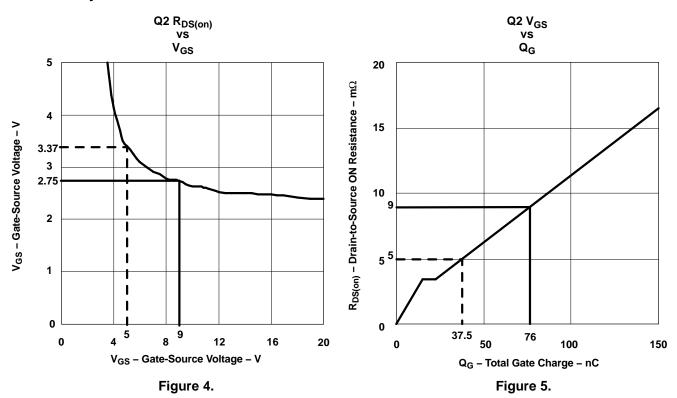

The graphs shown in Figure 2 through Figure 4 show typical MOSFET performance characteristic curves found in most manufacturers' data sheets and will be used as a basis for the following application example.

# 4 Q1 - Control MOSFET

Figure 2 highlights the R<sub>DS(on)</sub> values for V<sub>GS</sub> = 5 V and V<sub>GS</sub> = 9 V for the control MOSFET, Q1. Since it is more prone to switching loss, Q1 is normally selected based primarily upon lower gate charge, with secondary consideration given to R<sub>DS(on)</sub>. For V<sub>GS</sub> = 5 V, R<sub>DS(on)</sub> = 8.7 m $\Omega$ , and for V<sub>GS</sub> = 9 V, R<sub>DS(on)</sub> = 6.4 m $\Omega$ . Similarly Figure 3 shows the impact on gate charge for increasing V<sub>GS</sub> from 5 V to 9 V. For V<sub>GS</sub> = 5 V, Q<sub>G</sub> = 13 nC, and for V<sub>GS</sub> = 9 V, Q<sub>G</sub> = 24.8 nC. Table 1 summarizes the results.

Figure 4 highlights the R<sub>DS(on)</sub> values for V<sub>GS</sub> = 5 V and V<sub>GS</sub> = 9 V for the synchronous rectifier MOSFET, Q2. Since it is more prone to conduction loss, Q2 is selected based upon lowest possible R<sub>DS(on)</sub>, with secondary consideration given to gate charge. For V<sub>GS</sub> = 5 V, R<sub>DS(on)</sub> = 3.37 m $\Omega$ , and for 9 V, R<sub>DS(on)</sub> = 2.75 m $\Omega$ . Similarly Figure 5, shows the impact on gate charge for increasing V<sub>GS</sub> from 5 V to 9 V. For V<sub>GS</sub> = 5 V, Q<sub>G</sub> = 37.5 nC, and for V<sub>GS</sub> = 9 V, Q<sub>G</sub> = 76 nC. MOSFET parameters for each case of VGS are summarized in Table 1.

| V <sub>GS</sub> (V)               | R <sub>DS(on)</sub> (mΩ) | Q <sub>G</sub> (nC) | C <sub>OSS</sub> (pF) | R <sub>GI</sub> (Ω) | V <sub>TH</sub> (V) |  |  |  |

|-----------------------------------|--------------------------|---------------------|-----------------------|---------------------|---------------------|--|--|--|

| Q1 – Control MOSFET               |                          |                     |                       |                     |                     |  |  |  |

| 5                                 | 8.7                      | 13                  | 400                   | 0.5                 | 2                   |  |  |  |

| 9                                 | 6.4                      | 24.8                | 400                   | 0.5                 | 2                   |  |  |  |

| Q2 – Synchronous Rectifier MOSFET |                          |                     |                       |                     |                     |  |  |  |

| 5                                 | 3.37                     | 37.5                | 1200                  | 0.5                 | 2                   |  |  |  |

| 9                                 | 2.75                     | 76                  | 1200                  | 0.5                 | 2                   |  |  |  |

#### Table 1. MOSFET Parameters for Varying V<sub>GS</sub>

Depending upon the maximum load current, the lower  $R_{DS(on)}$  resulting from higher  $V_{GS}$  yields lower power losses up to some cut-off frequency where switching losses begins to dominate. At higher frequencies where switching losses dominate the lower gate charge resulting from lower  $V_{GS}$  will be preferred. At lower frequencies where conduction losses dominate the lower  $R_{DS(on)}$  resulting from higher  $V_{GS}$  will be preferred. At lower frequencies where conduction losses dominate the lower R<sub>DS(on)</sub> resulting from higher  $V_{GS}$  will be preferred. In terms of increasing efficiency, the best choice may be to drive the control MOSFET with a lower  $V_{GS}$  to minimize switching losses, and the synchronous rectifier with higher  $V_{GS}$  to lower conduction loss. However, since most synchronous buck MOSFET drivers do not offer the option of independently driving the control gate and synchronous gate with different voltages, this may not be a practical solution.

#### 6 **MOSFET Driver Parasitics**

Figure 6. Low-Side Drive and MOSFET Parasitic Model

Figure 6 shows a representative model illustrating most of the parasitic elements that can impact switching power supply performance. For simplicity only the low-side synchronous rectifier MOSFET and driver stage are shown. The resistances associated with the driver sink and source impedances quite often are not the same value and should be specified in a manufacturer's data sheet. It is also important to mention the effect of parasitic inductance between the driver and the MOSFET. At higher frequency operation, this inductance can limit the gate current trying to charge the MOSFET input capacitance. Equation 3 verifies that this results in slower rise and fall times and additional switching losses. The total lumped parasitic inductance,  $L_{LUMP}$ , for this example is assumed to be 50 nH. As shown in Figure 6,  $L_{LUMP}$  consists mostly of internal lead inductances associated with the MOSFET and driver package type. Since the designer really has no control over these parameters, the only component of parasitic inductance that can be controlled is trace inductance,  $L_{TRACE}$ . Therefore minimizing the length of trace between the driver and the MOSFET, as well as running a short and wide gate trace directly over a ground plane, will reduce parasitic trace inductance.

## 7 Application Example

The following application example compares the efficiency results for two cases of  $V_{GS}$ . For simplicity, the same amplitude  $V_{GS}$  is used for the control MOSFET and synchronous MOSFET for each case.

Given the following specifications:

- V<sub>IN</sub> = 5 V

- V<sub>OUT</sub> = 1.8 V

- I<sub>OUT</sub> = 20 A

- D = 0.36

- F<sub>SW</sub> = 200 kHz

- $R_G = 0 \Omega$

6

• L<sub>LUMP</sub> = 50 nH

# 8 Control MOSFET Power Loss Calculations

$$P_{C} = I_{OUT}^{2} \times R_{DS(on)} \times D$$

<sup>(1)</sup>

$$\mathsf{P}_{\mathsf{SW}} = \frac{1}{2} \times \mathsf{V}_{\mathsf{IN}} \times \mathsf{I}_{\mathsf{OUT}} \times \left(\mathsf{t}_{\mathsf{R}} + \mathsf{t}_{\mathsf{f}}\right) \times \mathsf{F}_{\mathsf{SW}} \tag{2}$$

Where tr  $\approx$  tf, and is approximated by:

$$t_r = t_f = \frac{Q_G}{I_G} + \frac{L_{LUMP} \times I_G}{V_{GS} - V_{TH}}$$

(3)

$$\mathsf{P}_{\mathsf{OUT}} = \frac{1}{2} \times \frac{4}{3} \times \mathsf{C}_{\mathsf{OSS}} \times \mathsf{V}_{\mathsf{IN}}^{2} \times \mathsf{F}_{\mathsf{SW}} \tag{4}$$

#### 9 High Side Driver Power Loss

Since the sink and source resistances of the driver are so much greater than the MOSFET's internal gate resistance, most of the switch loss associated with charging and discharging the MOSFET gate is dissipated in the driver device.

$$\mathsf{P}_{G1} = \mathsf{Q}_{G} \times \mathsf{V}_{GS} \times \mathsf{F}_{SW} \times \left( \frac{\mathsf{R}_{G1(sink)}}{\mathsf{R}_{G1(sink)} + \mathsf{R}_{G} + \mathsf{R}_{GI}} + \frac{\mathsf{R}_{G1(source)}}{\mathsf{R}_{G1(source)} + \mathsf{R}_{G} + \mathsf{R}_{GI}} \right)$$

(5)

Using Equation 1 through Equation 5, the total losses for the control MOSFET and driver can be approximated for each case of  $V_{GS}$ .

## 10 Synchronous Rectifier MOSFET Power Loss

For simplification of calculations, assume the following body-diode characteristics:

•

$$t_{BDR} + t_{BDF} = 10 \text{ ns}$$

•  $Q_{RR} = 48 \text{ nC}$

•  $V_F = 1 \text{ V}$

$P_{BD} = V_F \times I_{OUT} \times Fsw \times (t_{BDR} + t_{BDF})$  (6)

$P_C = I_{OUT}^2 \times R_{DS(on)} \times (1 - D)$  (7)

$P_{RR} = Q_{RR} \times V_{IN} \times F_{SW}$  (8)

$P_{SW} = 0$  (9)

$P_{RW} = 0$  (9)

$$P_{OUT} = 0 \tag{10}$$

#### 11 Low Side Driver Power Loss

$$\mathsf{P}_{G2} = \mathsf{Q}_{G} \times \mathsf{V}_{GS} \times \mathsf{F}_{SW} \times \left( \frac{\mathsf{R}_{G2(sink)}}{\mathsf{R}_{G2(sink)} + \mathsf{R}_{G} + \mathsf{R}_{G1}} + \frac{\mathsf{R}_{G2(source)}}{\mathsf{R}_{G2(source)} + \mathsf{R}_{G} + \mathsf{R}_{GI}} \right)$$

(11)

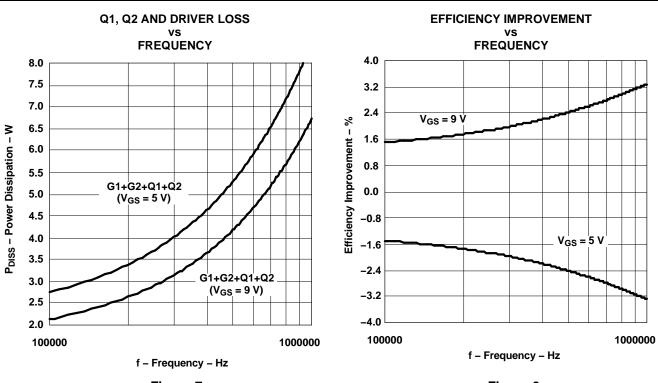

Using Equation 6 through Equation 11, the designer can approximate the total losses for the synchronous rectifier MOSFET and driver for each case of  $V_{GS}$ . Since many of the individual losses represented by Equation 1 through Equation 11 are frequency dependant, an EXCEL spreadsheet was designed to calculate and plot the total losses associated with the upper control MOSFET and lower synchronous MOSFET, versus frequency for each case of  $V_{GS}$ . A spreadsheet or MathCAD can make it is easy to determine the effect of varying the  $V_{GS}$  value.

Figure 7.

Figure 8.

Figure 7 shows Equation 1 through Equation 11 plotted against varying frequency (100 kHz to 1 MHz) for each case of V<sub>GS</sub>. Although these graphs can be generated at any output load current of interest, the results of Figure 7 are shown at  $I_{OUT(max)} = 20$  A, which is the point where rising MOSFET junction temperatures benefit most from higher efficiency. For  $I_{OUT} = 20$  A, it is clear that  $V_{GS} = 9$  V results in significantly less dissipated power over all frequencies of interest. Having calculated the total dissipated power for each case of V<sub>GS</sub>, and knowing the maximum output power, the graph of Figure 8 is developed using Equation 12.

$$\Delta \eta = \left[ \frac{\pm \mathsf{P}_{\mathsf{OUT}(\mathsf{max})} \times \left( \mathsf{P}_{\mathsf{DISS}(9\mathsf{V})} - \mathsf{P}_{\mathsf{DISS}(5\mathsf{V})} \right)}{\left( \mathsf{P}_{\mathsf{OUT}(\mathsf{max})} + \mathsf{P}_{\mathsf{DISS}(5\mathsf{V})} \right) \times \left( \mathsf{P}_{\mathsf{OUT}(\mathsf{max})} + \mathsf{P}_{\mathsf{DISS}(9\mathsf{V})} \right)} \right] \times 100\%$$

(12)

In addition to the driver and MOSFET effects, the power stage components must also be considered when selecting the optimal switching frequency. Since analyzing the power stage frequency effects are beyond the scope of this example, it is assumed that 200 kHz is a good trade-off between optimizing the MOSFET and gate drive circuitry and maintaining a fairly high frequency to minimize the size of the passive components in the power stage. The graph of Figure 8 shows an efficiency increase of approximately 1.7 percent at 200 kHz, for  $V_{GS} = 9$  V and  $I_{OUT} = 20$  A.

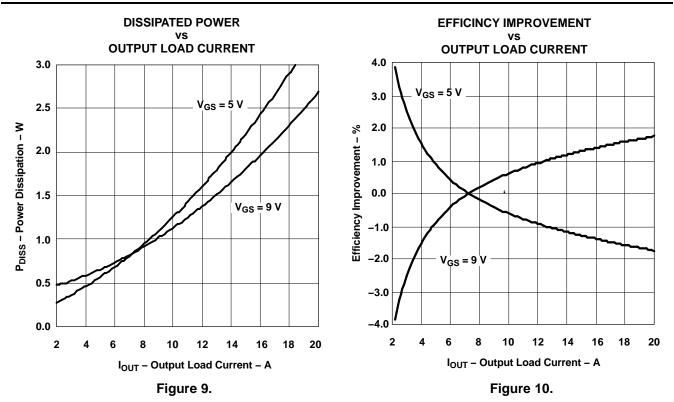

Selecting a switching frequency of 200 kHz, it would be helpful to know what effect  $V_{GS}$  has over the entire load range at the selected frequency. Equation 1 through Equation 11 can next be plotted versus load current at a fixed 200-kHz frequency.

Figure 9 shows the effects of power dissipation versus load current for  $V_{GS} = 5$  V and  $V_{GS} = 9$  V at a fixed 200 kHz frequency. As expected, Figure 10 shows a 1.7 percent efficiency increase for  $V_{GS} = 9$  V at  $I_{OUT} = 20$  A. However, at  $I_{OUT}$  less than 7 A,  $V_{GS} = 9$  V results in an efficiency loss compared to  $V_{GS} = 5$  V. For  $I_{OUT}$  less than 7 A, the efficiency improvement resulting from lower conduction loss has less effect, as is evident by Equation 1 and Equation 7. At lighter load current, frequency dependant losses begin to dominate over current dependant (conduction) losses, so a lower  $V_{GS} = 5$  V, hence a lower overall gate charge, is preferred.

It is interesting to note that by iterating through this graphical process, we can optimize the combination of  $V_{GS}$  and switching frequency. In this example, for instance using  $V_{GS} = 9$  V, at a frequency of 200 kHz we can gain 1.7 percent efficiency at maximum output current, at the cost of lower efficiency at lighter load current. Conversely, using  $V_{GS} = 5$  V at 200 kHz would result in higher efficiency just below the mid range of load current, but a lower efficiency at higher load current.

Following are the detailed calculations used to generate the graphs shown in Figure 7 through Figure 10:

(19)

(25)

Low Side Driver Power Loss

# 11.1 Control MOSFET, $V_{GS} = 5 V$

$$\mathsf{P}_{\mathsf{C}(5\mathsf{V})} = 20 \,\mathsf{A}^2 \times 8.7 \times 10^{-3} \,\Omega \times 0.36 = 1.253 \,\mathsf{W} \tag{13}$$

$$t_{R(5V)} = t_{f(5V)} = \frac{13 \times 10^{-9}C}{3 A} + \frac{50 \times 10^{-9}H \times 3 A}{5 V - 2 V} = 54.3 \times 10^{-9} s$$

(14)

$$P_{SW(5V)} = \frac{1}{2} \times 5 \text{ V} \times 20 \text{ A} \times (54.3 \times 10^{-9} \text{ s} + 54.3 \times 10^{-9} \text{ s}) \times (200 \times 10^{3} \text{ Hz}) = 1.09 \text{ W}$$

(15)

$$P_{OUT(5V)} = \frac{1}{2} \times \frac{4}{3} \times 400 \times 10^{-12} \,\text{F} \times 5 \,\text{V} \times 200 \times 10^3 \,\text{Hz} = 0.27 \,\text{mW}$$

(16)

And the power dissipated in the driver device at  $V_{GS}$  = 5 V is:

$$\mathsf{P}_{\mathsf{G1}(5\mathsf{V})} = 13 \times 10^{-9} \,\mathsf{C} \times 5 \,\mathsf{V} \times 200 \times 10^3 \,\mathsf{Hz} \times \left(\frac{0.9 \,\Omega}{0.9 \,\Omega + 0 + 0.5 \,\Omega} + \frac{25 \,\Omega}{25 \,\Omega + 0 + 0.5 \,\Omega}\right) = 21.1 \,\mathsf{mW} \tag{17}$$

The total power loss of the upper control MOSFET and the gate driver device is simply the sum of all the losses given by Equation 13 through Equation 17.

$$P_{G1_{TOTAL(5V)}} = 1.253 \text{ W} + 1.09 \text{ W} + 0.27 \times 10^{-3} \text{ W} + 21.1 \times 10^{-3} \text{ W} = 2.36 \text{ W}$$

(18)

## 11.2 Control MOSFET, $V_{GS} = 9 V$

$P_{C(9V)} = 20 \text{ A}^2 \times 6.4 \times 10^{-3} \,\Omega \times 0.36 = 0.922 \text{ W}$

$$t_{\mathsf{R}(9\mathsf{V})} = t_{\mathsf{f}(9\mathsf{V})} = \frac{24.8 \times 10^{-9} \mathsf{C}}{3 \mathsf{A}} + \frac{50 \times 10^{-9} \mathsf{H} \times 3 \mathsf{A}}{9 \mathsf{V} - 2 \mathsf{V}} = 30 \times 10^{-9} \mathsf{s}$$

(20)

$$P_{SW(9V)} = \frac{1}{2} \times 5 V \times 20 A \times (30 \times 10^{-9} s + 30 \times 10^{-9} s) \times (200 \times 10^{3} Hz) = 0.6 W$$

(21)

$$\mathsf{P}_{\mathsf{OUT}(9\mathsf{V})} = \frac{1}{2} \times \frac{4}{3} \times 400 \times 10^{-12} \,\mathsf{F} \times 5 \,\mathsf{V} \times 200 \times 10^3 \,\mathsf{Hz} = 0.27 \,\mathsf{mW}$$

(22)

And the power dissipated in the driver device at  $V_{GS} = 9$  V is:

$$\mathsf{P}_{\mathsf{G1(9V)}} = 24.9 \times 10^{-9} \,\mathsf{C} \times 9 \,\mathsf{V} \times 200 \times 10^3 \,\mathsf{Hz} \times \left(\frac{0.9 \,\Omega}{0.9 \,\Omega + 0 + 0.5 \,\Omega} + \frac{25 \,\Omega}{25 \,\Omega + 0 + 0.5 \,\Omega}\right) = 72.46 \,\mathsf{mW}$$

(23)

The total power loss of the upper control MOSFET and the gate driver device is simply the sum of all the losses given by Equation 19 through Equation 23.

$$P_{G1_{TOTAL(9V)}} = 0.922 \text{ W} + 0.6 \text{ W} + 0.27 \times 10^{-3} \text{ W} + 72.46 \times 10^{-3} \text{ W} = 1.595 \text{ W}$$

(24)

# 11.3 Synchronous Rectifier MOSFET, $V_{GS} = 5 V$

$P_{BD(5V)} = 1 \text{ V} \times 20 \text{ A} \times 200 \times 10^{3} \text{ Hz} \times (10 \times 10^{-9} \text{s}) = 40 \times 10^{-3} \text{ W}$

$$\mathsf{P}_{\mathsf{C}(5\mathsf{V})} = 20 \,\mathsf{A}^2 \times 3.37 \times 10^{-3} \,\Omega \times (1 - 0.36) = 0.863 \,\mathsf{W} \tag{26}$$

$$P_{RR(5V)} = 37.5 \times 10^{-9} \,\text{C} \times 5 \,\text{V} \times 200 \times 10^3 \,\text{Hz} = 37.5 \times 10^{-3} \,\text{W}$$

<sup>(27)</sup>

And the power dissipated in the driver device at  $V_{GS}$  = 5 V is:

$$\mathsf{P}_{\mathsf{G2}(5\mathsf{V})} = 37.5 \times 10^{-9} \,\mathsf{C} \times 5 \,\mathsf{V} \times 200 \times 10^3 \,\mathsf{Hz} \times \left(\frac{15\,\Omega}{15\,\Omega + 0 + 0.5\,\Omega} + \frac{20\,\Omega}{20\,\Omega + 0 + 0.5\,\Omega}\right) = 72.88 \times 10^{-3} \,\mathsf{W} \tag{28}$$

The total power loss of the synchronous rectifier MOSFET and the gate driver device is simply the sum of all the losses given by Equation 25 through Equation 28.

$$P_{G2\_TOTAL(5V)} = 40 \times 10^{-3} \text{ W} + 0.863 \text{ W} + 37.5 \times 10^{-3} \text{ W} + 72.88 \times 10^{-3} \text{ W} = 1.014 \text{ W}$$

(29)

#### TEXAS INSTRUMENTS www.ti.com

# 11.4 Synchronous Rectifier MOSFET, $V_{GS} = 9 V$

$$P_{BD(9V)} = 1 V \times 20 A \times 200 \times 10^{3} Hz \times (10 \times 10^{-9} s) = 40 \times 10^{-3} W$$

(30)

$$P_{C(9V)} = 20 A^2 \times 2.75 \times 10^{-3} \Omega \times (1 - 0.36) = 704 \times 10^{-3} W$$

(31)

$$P_{RR(9V)} = 76 \times 10^{-9} \,\text{C} \times 5 \,\text{V} \times 200 \times 10^3 \,\text{Hz} = 76 \times 10^{-3} \,\text{W}$$

(32)

And the power dissipated in the driver device at  $V_{GS} = 9$  V is:

$$\mathsf{P}_{\mathsf{G2}(9\mathsf{V})} = 76 \times 10^{-9} \,\mathsf{C} \times 9 \,\mathsf{V} \times 200 \times 10^3 \,\mathsf{Hz} \times \left(\frac{15\,\Omega}{15\,\Omega+0+0.5\,\Omega} + \frac{20\,\Omega}{20\,\Omega+0+0.5\,\Omega}\right) = 265.85 \times 10^{-3} \,\mathsf{W}$$

(33)

The total power loss of the synchronous rectifier MOSFET and the gate driver device is simply the sum of all the losses given by Equation 30 through Equation 33.

$$P_{G2\_TOTAL(9V)} = 40 \times 10^{-3} W + 704 \times 10^{-3} W + 76 \times 10^{-3} W + 265.85 \times 10^{-3} W = 1.086 W$$

(34)

Results from the application example are summarized in Table 2:

#### Table 2. F = 200 kHz, I<sub>OUT</sub> = 20 A, Power Dissipation Summary for Varying V<sub>GS</sub> V<sub>GS</sub> (V) Q1 - Control MOSFET Q2 - Synchronous Rectifier MOSFET Driver IC (G1) Driver IC (G2) Total Power Loss (MOSFETs + Driver IC) Δη

| 5 V         2.34 W         0.941 W         21.1 mW         72.88 mW         3.375 W         N/A           9 V         1.52 W         0.820 W         72.46 mW         265.85 mW         2.678 W         1.65% |     |         | MOSFEI   |           |             | + Driver IC) |        |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|---------|----------|-----------|-------------|--------------|--------|

| 9 V 1.52 W 0.820 W 72.46 mW 265.85 mW 2.678 W 1.65%                                                                                                                                                           | 5 V | 2.34 W  | 0.941 W  | 21.1 mW   | 72.88 mW    | 3.375 W      | N/A    |

|                                                                                                                                                                                                               | 9 V | 1.52 W  | 0.820 W  | 72.46 mW  | 265.85 mW   | 2.678 W      | 1.65%  |

|                                                                                                                                                                                                               |     | 1.02 11 | 0.020 11 | 72.101111 | 200.00 1111 | 2.070 11     | 1.0070 |

|                                                                                                                                                                                                               |     |         |          |           |             |              |        |

For  $F_{SW} = 200$  kHz and  $I_{OUT} = 20$  A, driving Q1 and Q2 with  $V_{GS} = 9$  V as opposed to  $V_{GS} = 5$  V results in an overall efficiency improvement of nearly 1.7 percent as shown in Table 2. For this example, a significant full load overall efficiency improvement can be gained by driving Q1 and Q2 with  $V_{GS} = 9$  V, at the trade-off of slightly lower efficiencies below  $I_{OUT} = 7$  A. The total losses for Q1 and Q2 given in Table 2 seem reasonable; however the thermal impedances of each MOSFET package should also be considered to make sure that junction temperatures are within rated limits. If junction temperatures are not being exceeded by chosen design constraints, it may be possible to further increase the switching frequency.

### 12 Conclusion

Using a given set of design parameters for a synchronous buck power stage, a full load efficiency gain of up to 1.7 percent can be realized when the MOSFET gates are driven at 9 V as opposed to 5 V. For this example, conduction losses were dominant at load currents greater then 7 A. For load currents less than 7 A, switching losses were dominant and efficiency was shown to actually decrease by up to 4%. In summary, higher light load efficiency could be expected for  $V_{GS} = 5$  V, and higher full load efficiency was shown at  $V_{GS} = 9$  V. When considering what level of  $V_{GS}$  to design for, examining the MOSFET power loss equations graphically can offer better insight as to where the benefits lie when frequency and output current are varied.

Given the choice, what is the optimal gate drive voltage amplitude for driving a switching MOSFET in a power supply application? The answer is not always clear, but with the aid of a spreadsheet or MATHCAD, the designer can make a fair comparison to graphically examine the trade-offs and potential benefits.

#### 13 References

- 1. Power Supply Design Seminar SEM-1400 Topic 2: *Design and Application Guide for High Speed MOSFET Gate Drive Circuits,* by Laszlo Balogh, Texas Instruments Literature No. SLUP169

- 2. Practical Considerations in High Performance MOSFET, IGBT and MCT Gate Drive Circuits, by Bill Andreycak, Texas Instruments Literature No. SLUA105

- 3. Power Supply Design Seminar SEM-1500 Topic 5: *Under the Hood of Low-Voltage DC/DC Converters*, by Brian Lynch and Kurt Hesse, Texas Instruments Literature No. SLUP206

- 4. Estimating MOSFET Switching Losses Means Higher Performance Buck Converters, by Peter Markowski, PlanetAnalog.com, December 18, 2002

#### **IMPORTANT NOTICE**

Texas Instruments Incorporated and its subsidiaries (TI) reserve the right to make corrections, modifications, enhancements, improvements, and other changes to its products and services at any time and to discontinue any product or service without notice. Customers should obtain the latest relevant information before placing orders and should verify that such information is current and complete. All products are sold subject to TI's terms and conditions of sale supplied at the time of order acknowledgment.

TI warrants performance of its hardware products to the specifications applicable at the time of sale in accordance with TI's standard warranty. Testing and other quality control techniques are used to the extent TI deems necessary to support this warranty. Except where mandated by government requirements, testing of all parameters of each product is not necessarily performed.

TI assumes no liability for applications assistance or customer product design. Customers are responsible for their products and applications using TI components. To minimize the risks associated with customer products and applications, customers should provide adequate design and operating safeguards.

TI does not warrant or represent that any license, either express or implied, is granted under any TI patent right, copyright, mask work right, or other TI intellectual property right relating to any combination, machine, or process in which TI products or services are used. Information published by TI regarding third-party products or services does not constitute a license from TI to use such products or services or a warranty or endorsement thereof. Use of such information may require a license from a third party under the patents or other intellectual property of the third party, or a license from TI under the patents or other intellectual property of TI.

Reproduction of information in TI data books or data sheets is permissible only if reproduction is without alteration and is accompanied by all associated warranties, conditions, limitations, and notices. Reproduction of this information with alteration is an unfair and deceptive business practice. TI is not responsible or liable for such altered documentation.

Resale of TI products or services with statements different from or beyond the parameters stated by TI for that product or service voids all express and any implied warranties for the associated TI product or service and is an unfair and deceptive business practice. TI is not responsible or liable for any such statements.

Following are URLs where you can obtain information on other Texas Instruments products and application solutions:

| Products         |                        | Applications       |                           |

|------------------|------------------------|--------------------|---------------------------|

| Amplifiers       | amplifier.ti.com       | Audio              | www.ti.com/audio          |

| Data Converters  | dataconverter.ti.com   | Automotive         | www.ti.com/automotive     |

| DSP              | dsp.ti.com             | Broadband          | www.ti.com/broadband      |

| Interface        | interface.ti.com       | Digital Control    | www.ti.com/digitalcontrol |

| Logic            | logic.ti.com           | Military           | www.ti.com/military       |

| Power Mgmt       | power.ti.com           | Optical Networking | www.ti.com/opticalnetwork |

| Microcontrollers | microcontroller.ti.com | Security           | www.ti.com/security       |

|                  |                        | Telephony          | www.ti.com/telephony      |

|                  |                        | Video & Imaging    | www.ti.com/video          |

|                  |                        | Wireless           | www.ti.com/wireless       |

Mailing Address:

Texas Instruments

Post Office Box 655303 Dallas, Texas 75265

Copyright © 2005, Texas Instruments Incorporated