# Design Voltage Margining Circuit for UCD90xxx Power Sequencer and System Manager

Zhiyuan Hu, Luke Lu

#### ABSTRACT

The UCD90xxx power sequencer and system manager provides margining function to trim output voltage of analog point-of-load converters. This application report discusses design considerations and provides a design procedure of the margining circuit.

#### Contents

| Introduction             | 2                                                                                                                      |

|--------------------------|------------------------------------------------------------------------------------------------------------------------|

| Design Considerations    | 2                                                                                                                      |

| Design Procedure         | 10                                                                                                                     |

| Fusion GUI Configuration | 13                                                                                                                     |

| Debugging Hints          | 16                                                                                                                     |

| Conclusion               | 16                                                                                                                     |

|                          | Introduction<br>Design Considerations<br>Design Procedure<br>Fusion GUI Configuration<br>Debugging Hints<br>Conclusion |

#### List of Figures

| 1  | Closed-Loop Margining Circuit                                                        | 2  |

|----|--------------------------------------------------------------------------------------|----|

| 2  | Equivalent Circuit at Maximum and Minimum V <sub>out</sub>                           | 2  |

| 3  | Equivalent Circuit of RC Filter                                                      | 4  |

| 4  | Block Diagram Without Margining Circuit                                              | 5  |

| 5  | Block Diagram With Margining Circuit                                                 | 6  |

| 6  | Example of V <sub>c1</sub> to V <sub>out</sub> Attenuation by Loop Response (Type-2) | 6  |

| 7  | Block Diagram With Margining Circuit (Type-3 Compensator)                            | 7  |

| 8  | Equivalent Circuit in Normal Operation                                               | 8  |

| 9  | Pin Assignment Window                                                                | 13 |

| 10 | Trim/Margining Configuration Window                                                  | 14 |

| 11 | OPERATION Command Window                                                             | 15 |

| 12 | GPI Configuration Window                                                             | 15 |

| 13 | PMBus Log Window                                                                     | 16 |

|    |                                                                                      |    |

#### Trademarks

All trademarks are the property of their respective owners.

#### 1 Introduction

The UCD90xxx power sequencer and system manager provides margining function to trim output voltage of analog point-of-load converters. This function can be used to facilitate voltage corner testing, which verifies the robustness of a product, as well as to actively trim output voltages in normal operation mode.

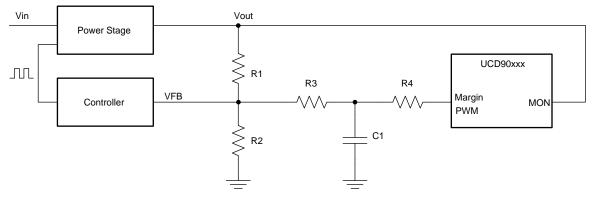

The UCD90xxx devices use digital pulse width modulator (DPWM) to implement the margining function. A closed-loop margining circuit is illustrated in Figure 1. The UCD90xxx device outputs a pulse width modulation (PWM) signal, which is filtered by an RC filter formed by R4 and C1. The DC component of C1 voltage is controlled by the PWM duty cycle. The voltage on C1 sources or sinks current from the FB node through R3 and, thus, changes the output voltage. The UCD90xxx compares the rail voltage and the targeted value and slowly adjusts the duty cycle. The margin control loop is so slow that it does not affect the power converter's feedback loop.

Figure 1. Closed-Loop Margining Circuit

This application report discusses the selection of the margin DPWM frequency, initial duty cycle, and component values of R3, R4, and C1. An Excel worksheet is available to carry out the calculation discussed in this application report (UCD90xxx Voltage Margining Circuit Design Tool).

#### 2 Design Considerations

2

#### 2.1 Resistor Values and Regulation Range

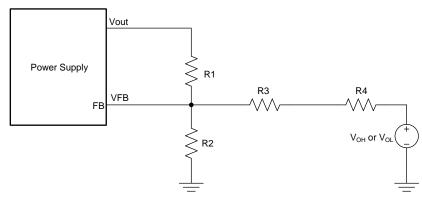

The maximum and minimum  $V_{out}$  occurs when the margin PWM duty cycle is 0 and 100%, respectively. The equivalent circuit is shown in Figure 2. The minimum and maximum output voltages with margining circuit are derived in Equation 2 and Equation 3, respectively.

Figure 2. Equivalent Circuit at Maximum and Minimum V<sub>out</sub>

$$\mathbf{V}_{\text{out,nom}} = \mathbf{V}_{\text{ref}} \times \frac{\mathbf{R}_1 + \mathbf{R}_2}{\mathbf{R}_2} \tag{1}$$

$$\mathbf{V}_{\text{out,min}} = \mathbf{V}_{\text{out,nom}} + \mathbf{R}_{1} \times \left(\frac{\mathbf{V}_{\text{ref}} - \mathbf{V}_{\text{OH}}}{\mathbf{R}_{3} + \mathbf{R}_{4}}\right)$$

(2)

$$\mathbf{V}_{\text{out,max}} = \mathbf{V}_{\text{out,nom}} + \mathbf{R}_{1} \times \left(\frac{\mathbf{V}_{\text{ref}} - \mathbf{V}_{\text{OL}}}{\mathbf{R}_{3} + \mathbf{R}_{4}}\right)$$

(3)

Where:

- V<sub>out.nom</sub> is the nominal output voltage determined by resistor divider values

- V<sub>OH</sub> is the PWM high-level output voltage

- V<sub>OL</sub> is the PWM low-level output voltage

- V<sub>ref</sub> is the power supply's reference voltage

Based on Equation 2 and Equation 3, the sum of R3 and R4 is determined by the desired margin low or margin high values, whichever results in a smaller R3+R4 value. Equation 4 and Equation 5 can be used to calculate R3+R4 value for margin low and margin high scenarios, respectively.

$$\mathbf{R}_{3} + \mathbf{R}_{4} = \frac{\mathbf{R}_{1} \left( \mathbf{V}_{\text{OH}} - \mathbf{V}_{\text{ref}} \right)}{\mathbf{V}_{\text{out,nom}} - \mathbf{V}_{\text{out,low}}}$$

$$\mathbf{R}_{3} + \mathbf{R}_{4} = \frac{\mathbf{R}_{1} \left( \mathbf{V}_{\text{ref}} - \mathbf{V}_{\text{OL}} \right)}{\mathbf{V}_{\text{out,high}} - \mathbf{V}_{\text{out,nom}}}$$

(4)

$$(4)$$

The above equations still hold true when R2 is not present in some applications.

#### 2.2 DPWM Frequency and V<sub>out</sub> Resolution

The DPWM signals are generated from an internal clock. The number of quantization steps in each DPWM period is inversely proportional to the DPWM frequency. The relation is shown in Equation 6.

$$n = \frac{F_{CLK}}{F_{PWM}}$$

(6)

Where:

- n is the number of quantization steps in a DPWM period

- F<sub>CLK</sub> is the internal clock frequency

- F<sub>PWM</sub> is the DPWM frequency

The DPWM duty cycle can only have integer number of quantization steps. As a result, the  $V_{out}$  controlled by the margin DPWM has finite resolution. The  $V_{out}$  step size equals to the full voltage margining range divided by the number of quantization steps in a period, as shown in Equation 7.

$$\mathbf{V}_{\text{out,step}} = \frac{\mathbf{V}_{\text{out,max}} - \mathbf{V}_{\text{out,min}}}{n} = \frac{\mathbf{V}_{\text{out,max}} - \mathbf{V}_{\text{out,min}}}{F_{\text{CLK}}} F_{\text{PWM}}$$

Apparently, the V<sub>out</sub> step size is proportional to the V<sub>out</sub> margining range and the DPWM frequency.

(7)

**Design Considerations**

www.ti.com

In margin mode and Active Trim mode, the UCD90xxx controls  $V_{out}$  with a very slow feedback loop. The loop is executed approximately once every 500  $\mu$ s. If the sampled  $V_{out}$  is unequal to the target value, the DPWM duty cycle will change by one quantization step towards the direction to minimize the error. Because  $V_{out}$  has voltage ripple and the analog-to-digital converter (ADC) has sampling noise, it can be expected that the DPWM duty cycle will fluctuate by  $\pm 1$  least significant bit (LSB) during margining and Active Trim operations, which will cause  $V_{out}$  to slightly fluctuate around the targeted margin or trim value.

To minimize the voltage fluctuation,  $V_{out}$  step size should be reduced in order for the  $V_{out}$  fluctuation, due to the ±1 LSB duty cycle fluctuation, is acceptable. According to Equation 7, the DPWM frequency can be reduced to achieve this goal. The optimal DPWM frequency is calculated by making  $V_{out,step}$  an acceptable value then deriving the switching frequency accordingly. For example,  $V_{out,step}$  can be arbitrarily set to 1 mV, then the margin DPWM frequency can be determined by Equation 8.

$$F_{PWM} = \frac{V_{out,step} F_{CLK}}{V_{out,max} - V_{out,min}}$$

(8)

(9)

# 2.3 Margin DPWM Output Filtering

The square-wave signal from the margin DPWM should be sufficiently filtered so only the DC component shows effect on  $V_{\mbox{\scriptsize out}}$

There are two filtering mechanisms:

- 1. RC filter in the margining circuit

- 2. Loop response of the power supply

#### 2.3.1 Attenuation by RC Filter

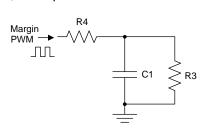

As shown in Figure 1, the RC filter is formed by R4 and C1. The voltage of C1 is connected to FB node through R3. Assuming the error amplifier is ideal, the FB node voltage is a DC voltage equal to the reference voltage. For AC analysis, the equivalent circuit of the RC filter can be drawn as in Figure 3.

Figure 3. Equivalent Circuit of RC Filter

The amplitude of the AC voltage on C1 can be estimated by Equation 9. The lower case v denotes AC voltage component.

$$\mathbf{V}_{C1} = \frac{\mathbf{V}_{PWM,1} \mathbf{R}_{3} \mathbf{Z}_{C1}}{\mathbf{R}_{3} \mathbf{R}_{4} + (\mathbf{R}_{3} + \mathbf{R}_{4}) \mathbf{Z}_{C1}}$$

Where:

- Z<sub>C1</sub> is the C1 impedance at the DPWM frequency

- v<sub>PWM.1</sub> is the amplitude of the fundamental harmonic of the DPWM square-wave output

**Design Considerations**

Only the fundamental harmonic is considered for simplicity. As shown in Equation 10, higher-order harmonics have more attenuation by the power supply's loop response and are, thus, negligible. The  $v_{PWM,1}$  is determined by Fourier series:

$$V_{PWM,1} = \frac{2(V_{OH} - V_{OL})\sin(\pi D)}{\pi}$$

Where:

• D is the duty cycle of the margin DPWM

The biggest  $v_{PWM,1}$  value occurs at D=0.5.

## 2.3.2 Attenuation by Loop Response

The voltage ripple on C1 is further attenuated by the power supply's loop response. The following analysis shows how to estimate the attenuation.

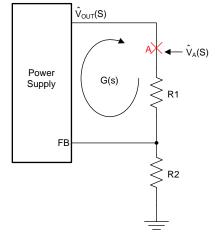

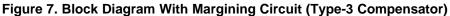

First consider a power supply without the margining circuit. If there is a break in the loop at point A, the compensated open-loop transfer function, G(s), is defined in Figure 4 and Equation 11.

$$G(s) = \frac{\hat{v}_{out}(s)}{\hat{v}_{A}(s)}$$

(11)

G(s) includes both power stage and compensator's transfer functions, which can be obtained from modeling or circuit measurement. G(s) should be available information to power supply designers.

Figure 4. Block Diagram Without Margining Circuit

Copyright © 2016, Texas Instruments Incorporated

5

(10)

**Design Considerations**

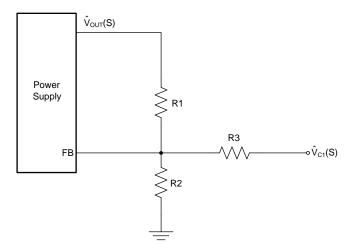

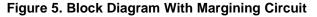

Next consider a power supply with the margining circuit, as shown in Figure 5. The power supply's transfer function from  $V_{C1}$  to  $V_{out}$  is in Equation 12.

$$T(s) = \frac{\hat{v}_{out}(s)}{\hat{v}_{C1}(s)} = \frac{R_{1}}{R_{3}} \frac{G(s)}{1 - G(s)}$$

(12)

Based on Equation 12, it can be predicted that when R1=R3, the transfer function from  $V_{C1}$  to  $V_{out}$  is identical to the closed-loop transfer function of the original power supply. Figure 6 provides simulation results to verify the above conclusion supply: below the cross-over frequency, the closed-loop gain is 0dB, and above the cross-over frequency, the closed-loop gain is equal to open-loop gain.

Open loop gain of the original power supply (with Type-2 compensator)

**Design Considerations**

The power supply's loop gain at the margin DPWM frequency can be observed on the Bode plot, estimated from cross-over frequency, or calculated from the mathematical model. The voltage gain from  $V_{C1}$  to  $V_{out}$  at the margin DPWM frequency can be calculated from Equation 13.

$$\frac{\hat{\mathbf{v}}_{\text{out}}\left(2\pi \mathbf{F}_{\text{PWM}}\right)}{\hat{\mathbf{v}}_{\text{C1}}\left(2\pi \mathbf{F}_{\text{PWM}}\right)} = \frac{\mathbf{R}_{1}}{\mathbf{R}_{3}} \frac{\mathbf{G}\left(2\pi \mathbf{F}_{\text{PWM}}\right)}{1 - \mathbf{G}\left(2\pi \mathbf{F}_{\text{PWM}}\right)} \tag{13}$$

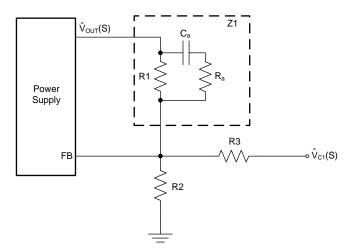

For the Type-3 compensator, there is an R-C network in parallel with R1. In this case, Z1 should be used to replace R1 as shown in Figure 7 and Equation 14.

$$\frac{\hat{v}_{out}(2\pi F_{PWM})}{\hat{v}_{C1}(2\pi F_{PWM})} = \frac{\left|Z_{1}(2\pi F_{PWM})\right|}{R_{3}} \frac{G(2\pi F_{PWM})}{1 - G(2\pi F_{PWM})}$$

$$Z_{1}(2\pi F_{PWM}) = \frac{R_{1}\left(R_{a} + \frac{1}{j2\pi F_{PWM}C_{a}}\right)}{R_{1} + R_{a} + \frac{1}{j2\pi F_{PWM}C_{a}}}$$

For simplicity, the Type-3 compensator can also use Equation 13 instead of Equation 14.

In conclusion, if the margin DPWM frequency is above the loop cross-over frequency, which is usually the case, the compensator will provide significant attenuation. A large R3 value compared to R1 (or Z1) also provides attenuation. The C1 value should be selected to provide additional attenuation in order to eliminate  $V_{out}$  voltage ripple at the margin DPWM frequency.

For switch mode power supply only (not applicable to LDO), an additional frequency component that requires attenuation is the alias generated by the power supply switching frequency (Fsw) and the margin DPWM frequency ( $F_{PWM}$ ). Due to the sampling nature of the PWM, the V<sub>C1</sub> ripple is injected into compensated error signal, which is then sampled at the PWM fall edges. If the V<sub>C1</sub> ripple frequency is greater than ½ Fsw, alias frequencies will occur at output

The alias frequencies can be calculated by Equation 15.

$$F_{alias} = \pm k \times F_{SW} \pm F_{PWM}$$

, k = 1, 2, 3...

(15)

7

(14)

Design Considerations

The lowest alias frequency (Fa) occurs in the first Nyquist zone ( $\leq \frac{1}{2}$  Fsw), which is the most difficult to filter. Fa frequency can be calculated by Equation 16.

$$m = floor\left(\frac{F_{PWM}}{F_{SW}}\right)$$

$$F_{a} = min\left(\left|F_{PWM} - m \times F_{SW}\right|, \left|F_{PWM} - (m+1) \times F_{SW}\right|\right)$$

(16)

The margin DPWM frequency should be selected such that Fa is at its highest possible value (1/2 Fsw).

$$F_{PWM} = \left(m + \frac{1}{2}\right) \times F_{SW}, m = 0, 1, 2...$$

(17)

## 2.4 Impact on Power Supply Normal Operation

When not in margin or Active Trim mode, the margin DPWM pin is in high-impedance state. The branch formed by R3 and C1 is in parallel with R2, as shown in Figure 8.

Figure 8. Equivalent Circuit in Normal Operation

Assuming the error amplifier in the controller is an ideal op-amp, the VFB is a DC voltage equal to the reference voltage. In this case, there is no small-signal current flowing through the R3-C1 branch, thus, it has no impact to the power supply's loop transfer function.

Real-world error amplifier has limited gain-bandwidth product, but the op-amp gain at the cross-over frequency should be still greater than 100. Consider the case where there is a voltage disturbance on  $V_{out}$  at the cross-over frequency. Because the closed-loop gain is 1 at cross-over frequency and the error amplifier still has a gain of 100, the voltage disturbance on VFB is about 1/100 of that on  $V_{out}$ . Assuming R3=10-R1, the small-signal current flowing through R3 is only 0.1% of that flowing through R1. Therefore, the impact of the R3-C1 branch on the power supply's transfer function is negligible.

# 2.5 Impact on Power Supply Soft Start

During closed-loop soft start, the FB node voltage ramps up with the reference voltage. C1 voltage is initially zero. Current must flow from FB node to C1 to charge the capacitor. The additional charge current to C1 is from  $V_{out}$  flowing through R1. Therefore, when C1 is charging,  $V_{out}$  will be higher than the reference voltage determined value. At the end of the soft start ramp, there is a possibility to overshoot.

In reality, the actual  $V_{out}$  ramp lags VFB ramp because the system has a steady state error for a slope input. At the end of VFB ramp, The  $V_{out}$  lag will cancel the overshoot. The VFB ramp is often flattened near the end of the ramp, which reduces the current in R3 and thus reduces the overshoot. Therefore, the actual overshoot is often invisible. The following simplified math model is for sanity check and for reference only.

Assuming the soft start ramp is strictly linear, the VFB can be expressed as a function of time.

$$V_{FB}(t) = \frac{V_{ref}}{t_{rise}} \times t$$

(18)

Where:

• t<sub>rise</sub> is the soft start rise time

If the ramp is infinitely long, the R3 current will achieve a steady state.

$$I_{R3}(\infty) = \frac{V_{ref}}{t_{rise}} \times C_1$$

(19)

The R3 current as a function of time can then be derived as:

$$I_{R3}(t) = I_{R3}(\infty) \times \left(1 - e^{\frac{-t}{R_{3x}C_{1}}}\right)$$

(20)

At the end of soft start ramp, the voltage overshoot caused by C1 charging is:

$$\Delta V_{out} = I_{R3} \left( t_{rise} \right) \times R_1 = \frac{V_{ref}}{t_{rise}} \times R_1 \times C_1 \times \left( 1 - e^{\frac{-t_{rise}}{R_3 \times C_1}} \right)$$

(21)

Equation 21 can be used to check overshoot voltage at the end of soft start ramp. The actual overshoot amount is often ~50-mV smaller than predicted because the soft start ramp is often flattened and gradually merges into steady state near the end. This calculation is for information only. If the overshoot is too large, the C1 value needs to be decreased.

To minimize C1 value needed:

- 1. Make R3=R4 (R3+R4 is fixed, which is discussed in Section 2.1).

- 2. Reduce the Margin High/Low range so that the larger R3+R4 value can be used.

- 3. Increase the R1 value so that larger R3+R4 value can be used.

4. Allow a higher ripple at V<sub>out</sub>.

Alternately, increasing soft start rise time can also reduce overshoot.

#### 2.6 Initial Duty Cycle

The UCD90xxx adjusts the margin DPWM duty cycle by one LSB every 500  $\mu$ s. If the initial duty cycle setting is far from the steady state value, it will cause sudden V<sub>out</sub> change when margining and Active Trim function is activated.

The suggested initial duty cycle is calculated by Equation 22. The margin DPWM's initial DC output voltage equals to the reference voltage, which will allow the UCD90xxx to gradually bring  $V_{out}$  to the targeted Margin High/Low level.

$$\mathbf{D}_{\text{init}} = \frac{\mathbf{V}_{\text{ref}} - \mathbf{V}_{\text{OL}}}{\mathbf{V}_{\text{OH}} - \mathbf{V}_{\text{OL}}}$$

(22)

#### Design Procedure

#### 3 Design Procedure

**Step 1**: Use Equation 23 to calculate nominal output voltage. V<sub>ref</sub> is the reference voltage of the power supply controller.

$$\mathbf{V}_{\text{out,nom}} = \mathbf{V}_{\text{ref}} \times \frac{\mathbf{R}_1 + \mathbf{R}_2}{\mathbf{R}_2}$$

(23)

**Step 2**: Use Equation 24 to calculate initial margin DPWM duty cycle.  $V_{OH}$  and  $V_{OL}$  are output high and output low voltage levels of DPWM pins. Typical values are  $V_{OH} = 3.2$  V and  $V_{OL} = 0$  V.

$$D_{init} = \frac{V_{ref} - V_{OL}}{V_{OH} - V_{OL}}$$

(24)

**Step 3**: Use Equation 25 and Equation 26 to estimate the margin DPWM pin current.  $V_{out,low}$  is the margin-low output voltage, which must be less than  $V_{out,nom}$ .  $V_{out,high}$  is the margin-high output voltage, which must be greater than  $V_{out,nom}$ .

If the higher current value of the two is greater than 1 mA, increase the R1 and R2 values. In general, larger R1 and R2 values are preferred to reduce margin DPWM pin's current.

$$I_{DPWM} = \frac{V_{out,high} - V_{out,nom}}{R_1}$$

$$I_{DPWM} = \frac{V_{out,nom} - V_{out,low}}{R_1}$$

(25)

(26)

**Step 4**: Use Equation 27 and Equation 28 to calculate R3 and R4 values. The smaller value of the two should be selected. The actual resistor value must be equal to or less than the calculated value.

$$\mathbf{R}_{3} = \mathbf{R}_{4} = \frac{\mathbf{R}_{1} \left( \mathbf{V}_{\text{OH}} - \mathbf{V}_{\text{ref}} \right)}{2 \left( \mathbf{V}_{\text{out,nom}} - \mathbf{V}_{\text{out,low}} \right)}$$

$$\mathbf{R}_{3} = \mathbf{R}_{4} = \frac{\mathbf{R}_{1} \left( \mathbf{V}_{\text{ref}} - \mathbf{V}_{\text{OL}} \right)}{2 \left( \mathbf{V}_{\text{out,high}} - \mathbf{V}_{\text{out,nom}} \right)}$$

(27)

$$(27)$$

**Step 5**: Use Equation 29 to calculate maximum margin DPWM frequency that provides sufficient  $V_{out}$  resolution.

$$F_{PWM,max} = \frac{V_{out,step} F_{CLK}}{V_{out,max} - V_{out,min}}$$

(29)

$V_{out,step}$  is the allowed  $V_{out}$  fluctuation in margining and Active Trim mode. Larger  $V_{out,step}$  allows for higher margin DPWM frequency. A good starting point is  $V_{out,step} = 0.1\% V_{out,nom}$ .

$V_{out,min}$  and  $V_{out,max}$  are the output voltage levels when margin DPWM is at 100% and 0% duty cycle, respectively. The voltage levels can be calculated from Equation 30 and Equation 31.

$$\mathbf{V}_{\text{out,min}} = \mathbf{V}_{\text{out,nom}} + \mathbf{R}_{1} \times \left(\frac{\mathbf{V}_{\text{ref}} - \mathbf{V}_{\text{OH}}}{\mathbf{R}_{3} + \mathbf{R}_{4}}\right)$$

10

(30)

www.ti.com

(31)

$$\mathbf{V}_{\text{out,max}} = \mathbf{V}_{\text{out,nom}} + \mathbf{R}_{1} \times \left(\frac{\mathbf{V}_{\text{ref}} - \mathbf{V}_{\text{OL}}}{\mathbf{R}_{3} + \mathbf{R}_{4}}\right)$$

$\mathsf{F}_{\mathsf{CLK}}$  is the internal clock frequency of UCD90xxx devices:

- 1. Use 80 MHz for UCD90240 and UCD90320's Margin pins.

- 2. Use 500 MHz for UCD9090(A), UCD90120(A), UCD90124(A), and UCD90160(A)'s FPWM pins.

- Use 15.625 MHz for UCD9090(A), UCD90120(A), UCD90124(A), and UCD90160(A)'s PWM3 and PWM4 pins.

**Step 6**: Use Equation 32 to calculate optimal margin DPWM frequency,  $F_{PWM}$ .  $F_{SW}$  is power supply's switching frequency.

$$m = \max\left(1, \operatorname{round}\left(\frac{F_{PWM, \max}}{F_{SW}}\right)\right)$$

$$F_{PWM} = \min\left(F_{PWM, \max}, \left(m - \frac{1}{2}\right) \times F_{SW}\right)$$

(32)

Step 7: Use Equation 33 to calculate the lowest alias frequency, Fa.

$$n = floor\left(\frac{F_{PWM}}{F_{SW}}\right)$$

$$F_{a} = min\left(\left|F_{PWM} - n \times F_{SW}\right|, \left|F_{PWM} - (n+1) \times F_{SW}\right|\right)$$

(33)

**Step 8**: Use Equation 34 to estimate switch mode power supply's open loop gain at frequency Fa, assuming:

(a) The loop bandwidth is approximately 20% of switching frequency

(b) The gain slope is -20dB/decade between crossover frequency and Fa

$$\operatorname{Gain}_{OL}\left(2\pi F_{a}\right) = \frac{0.2F_{SW}}{F_{a}}$$

(34)

This value can be also obtained from experimental result.

For the margining LDO output, use 1 for this value.

Step 9: Use Equation 35 to estimate closed-loop gain from  $V_{C1}$  ripple to  $V_{out}$ .

$$\operatorname{Gain}_{\operatorname{VC1\_to\_Vout}}\left(2\pi F_{a}\right) = \min\left(\frac{R_{1}}{R_{3}}, \operatorname{Gain}_{OL}\left(2\pi F_{a}\right)\frac{R_{1}}{R_{3}}\right)$$

(35)

Copyright © 2016, Texas Instruments Incorporated

Design Procedure

www.ti.com

(Optional for Type-3 compensator)

$$\operatorname{Gain}_{\operatorname{VC1_to}_{\operatorname{Vout}}}\left(2\pi F_{a}\right) = \min\left(\frac{\left|Z_{1}\left(2\pi F_{a}\right)\right|}{R_{3}}, \operatorname{Gain}_{\operatorname{OL}}\left(2\pi F_{a}\right)\frac{\left|Z_{1}\left(2\pi F_{a}\right)\right|}{R_{3}}\right)$$

(36)

Where:

• Z1 is defined in Figure 7.

$$\left| Z_{1} \left( 2\pi F_{a} \right) \right| = R_{1} \sqrt{\frac{4C_{a}^{2} F_{a}^{2} \pi^{2} R_{a}^{2} + 1}{4C_{a}^{2} F_{a}^{2} \pi^{2} \left( R_{1} + R_{a} \right)^{2} + 1}}$$

(37)

For simplicity, Equation 35 can be used for Type-3 compensator.

**Step 10**: Use Equation 38 to calculate the required total gain so the margin DPWM square-wave signal is attenuated to an acceptable  $V_{out}$  ripple, that is,  $V_{out,step}$  defined in Step 5. This step takes into account the worst case scenario where the margin DPWM duty cycle is 50%.

$$Gain_{total} = V_{out,step} \times \frac{\pi}{2(V_{OH} - V_{OL})}$$

(38)

**Step 11**: Use Equation 39 to calculate the gain required to attenuate the margin DPWM square wave to the required  $V_{c1}$  ripple.

$$Gain_{RC} = \frac{Gain_{total}}{Gain_{VC1_{to}_{Vout}} \left(2\pi F_{a}\right)}$$

(39)

**Step 12**: Use Equation 40 to calculate the C1 value. If  $Gain_{RC}$  is greater than R4/(R3+R4), C1 is not needed.

$$C_{1} = \frac{\sqrt{R_{3}^{2} - \text{Gain}_{RC}^{2} (R_{3} + R_{4})^{2}}}{2\pi F_{PWM} \text{Gain}_{RC} R_{3} R_{4}}$$

(40)

Use Equation 41 to predict overshoot at the end of soft start ramp. trise is the soft start rise time.

The actual overshoot is often ~50-mV smaller than predicted because the soft start ramp is often flattened and gradually merges into steady state near the end. This calculation is for information only.

If the overshoot is too large, the following measures can be used:

- 1. Reduce unnecessarily wide Margin High/Low range to reduce the C1 value.

- 2. Increase the allowed V<sub>out</sub> ripple so as to increase DPWM frequency and, thus, decreases the C1 value.

- 3. Increase the soft start rise time to reduce overshoot directly.

- 4. Increase the R1 value to reduce C1 value needed for filtering.

$$\Delta \mathbf{V}_{\text{out}} = \frac{\mathbf{V}_{\text{ref}}}{\mathbf{t}_{\text{rise}}} \times \mathbf{R}_{1} \times \mathbf{C}_{1} \times \left(1 - e^{\frac{-\mathbf{t}_{\text{rise}}}{\mathbf{R}_{3} \times \mathbf{C}_{1}}}\right)$$

(41)

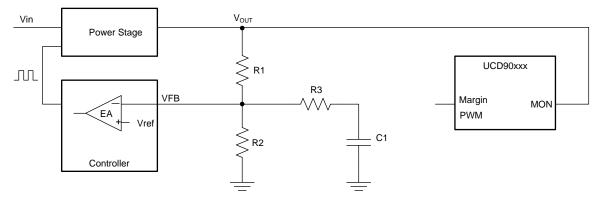

## 4 Fusion GUI Configuration

The margin DPWM setting can be configured in the Fusion Digital Power<sup>™</sup> Designer (referred to as Fusion GUI).

The margin DPWM pin assignment can be configured in the pin assignment window. Click the button under *Trim/Margin PWM* column to assign a FPWM or PWM pin.

For UCD9090(A), UCD90120(A), UCD90124(A), and UCD90160(A), FPWM pins have higher resolution than PWM pins, so FPWM pings are preferred for the margining and trimming purpose. The PWM1 and PWM2 pins have fixed low switching frequency and are, thus, not recommended for margining function.

For UCD90240 and UCD90320, all Margin pins can be used for margining function.

|          | Rail Name | Voltage      | Temperature                  | Current                         | Enable             | Trim/Margin PWM                 | Actions          |

|----------|-----------|--------------|------------------------------|---------------------------------|--------------------|---------------------------------|------------------|

| Rail #1  | Rail #1   | Pin 1 MON1   | < <u>Click to Assign&gt;</u> | < <u>Click to Assign&gt;</u>    | Pin 11 GPIO1       | <click assign="" to=""></click> | Delete Configure |

| Rail #2  | Rail #2   | Pin 2 MON2   | < <u>Click to Assign&gt;</u> | < <u>Click to Assign&gt;</u>    | Pin 12 GPIO2       | <click assign="" to=""></click> | Delete Configure |

| Rail #3  | Rail #3   | Pin 3 MON3   | < <u>Click to Assign&gt;</u> | < <u>Click to Assign&gt;</u>    | Pin 13 GPIO3       | <click assign="" to=""></click> | Delete Configure |

| Rail #4  | Rail #4   | Pin 4 MON4   | < <u>Click to Assign&gt;</u> | < <u>Click to Assign&gt;</u>    | Pin 14 GPIO4       | <click assign="" to=""></click> | Delete Configure |

| Rail #5  | Rail #5   | Pin 5 MON5   | < <u>Click to Assign&gt;</u> | < <u> Click to Assign&gt;</u>   | Pin 25 GPIO 13     | <click assign="" to=""></click> | Delete Configure |

| Rail #6  | Rail #6   | Pin 6 MON6   | < <u>Click to Assign&gt;</u> | < <u>Click to Assign&gt;</u>    | Pin 33 GPIO 16     | <click assign="" to=""></click> | Delete Configure |

| Rail #7  | Rail #7   | Pin 59 MON7  | < Click to Assign >          | < Click to Assign >             | Pin 34 GPIO 17     | < <u>Click to Assign&gt;</u>    | Delete Configure |

| Rail #8  | Rail #8   | Pin 62 MON8  | < <u>Click to Assign&gt;</u> | < <u>Click to Assign&gt;</u>    | Pin 35 GPIO 18     | <click assign="" to=""></click> | Delete Configure |

| Rail #9  | Rail #9   | Pin 63 MON9  | < <u>Click to Assign&gt;</u> | < <u>Click to Assign&gt;</u>    | Pin 36 TCK GPIO 19 | <click assign="" to=""></click> | Delete Configure |

| Rail #10 | Rail #10  | Pin 50 MON10 | < <u>Click to Assign&gt;</u> | < Click to Assign >             | Pin 37 TDO GPIO20  | <click assign="" to=""></click> | Delete Configure |

| Rail #11 | Rail #11  | Pin 52 MON11 | < <u>Click to Assign&gt;</u> | < <u>Click to Assign&gt;</u>    | Pin 38 TDI GPIO21  | <click assign="" to=""></click> | Delete Configure |

| Rail #12 | Rail #12  | Pin 54 MON12 | Pin 56 MON13                 | <click assign="" to=""></click> | Pin 39 TMS GPIO22  | <click assign="" to=""></click> | Delete Configure |

|  | Figure | 9. | Pin | Assignment | Window |

|--|--------|----|-----|------------|--------|

|--|--------|----|-----|------------|--------|

Fusion GUI Configuration

www.ti.com

Once a margin DPWM pin is assigned, click the *Configure* button next to it to configure frequency, initial duty cycle, margin mode, and so on.

| PWM Config:         Duty Cycle:       19 → %         Frequency:       1.000000 → MHz ∨         Frequency:       1.000000 → MHz ∨         Frequency:       1.000000 → MHz ∨         Frequency can be 15.275 kHz to 125 MHz         Margin Mode:         Image:       Tri-State         When not margining, the PWM pin is tri-stated.         Active Trim         When not margining, the PWM duty-cycle is continuously adjusted to keep the voltage at VOUT_COMMAND.         Active Duty Cycle         When not margining, the PWM duty-cycle is set to a fixed duty-cycle.         Ignore faults         When margining is enabled with a pin, this determines if faults (over-voltage and under-voltage) are ignored or not.         Increase Duty Cycle increases Voltage         When margining, this determines if increasing duty cycle will increase or decrease voltage | — Rail #1 Trim/Margining                                        |  |  |  |  |  |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------|--|--|--|--|--|

| Frequency:       1.000000 ⊕ MHz ♥         Frequency can be 15.275 kHz to 125 MHz         Margin Mode:            • Tri-State         When not margining, the PWM pin is tri-stated.             • Active Trim         When not margining, the PWM duty-cycle is continuously         adjusted to keep the voltage at VOUT_COMMAND.             • Active Duty Cycle         When not margining, the PWM duty-cycle is set to a fixed         duty-cycle.             • Ignore faults         When margining is enabled with a pin, this determines if faults         (over-voltage and under-voltage) are ignored or not.             • Increase Duty Cycle         when margining, this determines if increasing duty cycle will                                                                                                                                                 | PWM Config:                                                     |  |  |  |  |  |

| <ul> <li>Frequency can be 15.275 kHz to 125 MHz</li> <li>Margin Mode: <ul> <li>Tri-State</li> <li>When not margining, the PWM pin is tri-stated.</li> </ul> </li> <li>Active Trim <ul> <li>When not margining, the PWM duty-cycle is continuously adjusted to keep the voltage at VOUT_COMMAND.</li> <li>Active Duty Cycle</li> <li>When not margining, the PWM duty-cycle is set to a fixed duty-cycle.</li> </ul> </li> <li>Ignore faults <ul> <li>When margining is enabled with a pin, this determines if faults (over-voltage and under-voltage) are ignored or not.</li> <li>Increase Duty Cycle increases Voltage</li> <li>When margining, this determines if increasing duty cycle will</li> </ul> </li> </ul>                                                                                                                                                           | Duty Cyde: 19 📩 %                                               |  |  |  |  |  |

| Margin Mode:<br><ul> <li>Tri-State<br/>When not margining, the PWM pin is tri-stated.</li> <li>Active Trim<br/>When not margining, the PWM duty-cycle is continuously<br/>adjusted to keep the voltage at VOUT_COMMAND.</li> <li>Active Duty Cycle<br/>When not margining, the PWM duty-cycle is set to a fixed<br/>duty-cycle.</li> <li>Ignore faults<br/>When margining is enabled with a pin, this determines if faults<br/>(over-voltage and under-voltage) are ignored or not.</li> <li>Increase Duty Cycle increases Voltage<br/>When margining, this determines if increasing duty cycle will</li> </ul>                                                                                                                                                                                                                                                                  | Frequency: 1.000000 MHz V                                       |  |  |  |  |  |

| <ul> <li>Tri-State         When not margining, the PWM pin is tri-stated.         <ul> <li>Active Trim             When not margining, the PWM duty-cycle is continuously             adjusted to keep the voltage at VOUT_COMMAND.</li> <li>Active Duty Cycle             When not margining, the PWM duty-cycle is set to a fixed             duty-cycle.</li> </ul> </li> <li>Ignore faults         When margining is enabled with a pin, this determines if faults         (over-voltage and under-voltage) are ignored or not.</li> <li>Increase Duty Cycle increases Voltage         When margining, this determines if increasing duty cycle will</li> </ul>                                                                                                                                                                                                              | Frequency can be 15.275 kHz to 125 MHz                          |  |  |  |  |  |

| <ul> <li>When not margining, the PWM pin is tri-stated.</li> <li>Active Trim<br/>When not margining, the PWM duty-cycle is continuously<br/>adjusted to keep the voltage at VOUT_COMMAND.</li> <li>Active Duty Cycle<br/>When not margining, the PWM duty-cycle is set to a fixed<br/>duty-cycle.</li> <li>Ignore faults<br/>When margining is enabled with a pin, this determines if faults<br/>(over-voltage and under-voltage) are ignored or not.</li> <li>Increase Duty Cycle increases Voltage<br/>When margining, this determines if increasing duty cycle will</li> </ul>                                                                                                                                                                                                                                                                                                | Margin Mode:                                                    |  |  |  |  |  |

| <ul> <li>When not margining, the PWM duty-cycle is continuously adjusted to keep the voltage at VOUT_COMMAND.</li> <li>Active Duty Cycle<br/>When not margining, the PWM duty-cycle is set to a fixed duty-cycle.</li> <li>Ignore faults<br/>When margining is enabled with a pin, this determines if faults (over-voltage and under-voltage) are ignored or not.</li> <li>Increase Duty Cycle increases Voltage<br/>When margining, this determines if increasing duty cycle will</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                    | 0                                                               |  |  |  |  |  |

| <ul> <li>When not margining, the PWM duty-cycle is set to a fixed duty-cycle.</li> <li>Ignore faults</li> <li>When margining is enabled with a pin, this determines if faults (over-voltage and under-voltage) are ignored or not.</li> <li>Increase Duty Cycle increases Voltage</li> <li>When margining, this determines if increasing duty cycle will</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | When not margining, the PWM duty-cycle is continuously          |  |  |  |  |  |

| When margining is enabled with a pin, this determines if faults<br>(over-voltage and under-voltage) are ignored or not.<br>Increase Duty Cycle increases Voltage<br>When margining, this determines if increasing duty cycle will                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | When not margining, the PWM duty-cycle is set to a fixed        |  |  |  |  |  |

| When margining, this determines if increasing duty cycle will                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | When margining is enabled with a pin, this determines if faults |  |  |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | When margining, this determines if increasing duty cycle will   |  |  |  |  |  |

Figure 10. Trim/Margining Configuration Window

Upon completing the configuration, click *Write to Hardware* button on the left side of the Fusion GUI to confirm the changes.

The margining function can be enabled by sending *OPERATION* command or by toggling general purpose input (GPI).

The *OPERATION* command can be sent from Fusion GUI under *Monitor* page. Users can click a button in GUI to start margining a rail.

| Margining -   | Rail #1                          |

|---------------|----------------------------------|

| Margin: 💿 1   | None 🔾 Low 🔿 High                |

| Fault Action: | <ul> <li>Act on Fault</li> </ul> |

|               | 🔘 Ignore Fault                   |

Figure 11. OPERATION Command Window

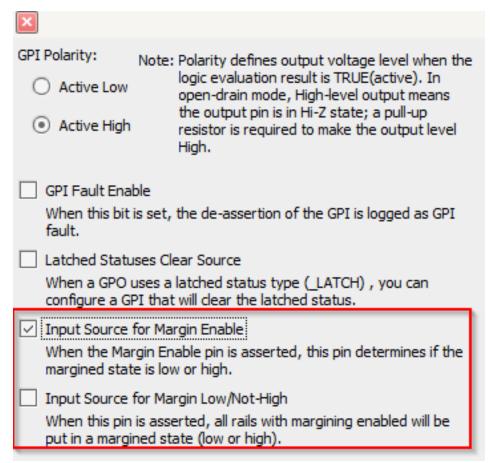

Users can also assign two GPI pins to control the margining function. In the GPI configuration window, a GPI pin can be configured to enable margining for all rails or control the margining direction of all rails.

Figure 12. GPI Configuration Window

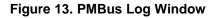

The Fusion GUI sends configuration data to UCD90xxx devices through PMBus commands. Users can also use their own PMBus hosts to send PMBus commands. The related PMBus commands used by the Fusion GUI are shown in the PMBus Log window on the lower-right corner of the Fusion GUI. This information can help users compose PMBus command scripts to configure UCD90xxx devices. The detailed explanation of PMBus commands can be found in UCD90xxx Sequencer and System Health Controller PMBus Command Reference User's Guide.

| PMBus Log                                                                                                                                                                                                                                                       | ٦<br>ب    |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|

| 10:57:33.940: UCD90120A @ 104d: GPO_CONFIG_10 [MFR 40,0xF8]: wrote Unassigned; No Mask<br>[0x00000000000000000000000000000000000                                                                                                                                | ency:     |

| 15.28 kHz; Phase: 0.0 deg [0x80000003BAB8000] to RAM<br>11:10:46.580: UCD90120A @ 104d: MARGIN_CONFIG [MFR 37,0xF5,Rail #1]: wrote Mode: EnableTriState; Increa<br>Cycle decreases Voltage; Ignore Faults: False; PWM Pin: ID 0, # 17 FPWM1_GPIO5 [0x40] to RAM | COLVERS R |

| PMBus Log                                                                                                                                                                                                                                                       | 68        |

## 5 Debugging Hints

- 1. The margining function is not working. Suggestion:

- (a) Check the margin DPWM pin output. If the pin outputs a PWM signal, 3.3 V (100% duty cycle), or 0 V (0% duty cycle), the margining function is working. In that case, check for problems in the external circuit. However, if the pin's voltage is POL's reference voltage, the margining function is not enabled and the pin is in Hi-Z state. In that case, check the device configuration.

- (b) Margining can only be enabled after the rail rises above Power Good On threshold at least once after the rail is enabled. If the rail output voltage stays below Power Good On, the margining function will not start working.

- (c) The rail may be shut down if the Margin High/Low threshold exceeds over voltage (OV) or under voltage (UV) thresholds. The UCD90xxx device allows users to override the fault actions during margining (see Figure 11).

- The margining function is working, but the rail voltage cannot reach configured Margin High/Low levels. Suggestion: The maximum and minimum Margin High/Low voltage is limited by the R3+R4 value (refer to

The maximum and minimum Margin High/Low voltage is limited by the R3+R4 value (refer to Section 2.1). Reduce R3 and/or R4 value to increase margin voltage range.

3. When margining function is enabled, the output voltage ripple is too large. Suggestion:

Check ripple frequency.

- (a) If the output voltage changes every 500 μs, the ripple is due to limited resolution (refer to Section 2.2). In that case, use the Excel worksheet to calculate optimal R3 and R4 value and reduce margin DPWM frequency.

- (b) If the output voltage is at the margin DPWM frequency or its alias frequency, the ripple is due to insufficient attenuation (refer to Section 2.3). In that case, use the Excel worksheet to calculate optimal R3 and R4 value and optimal margin DPWM frequency and increase C1 value.

- 4. There is a sudden output voltage drop or surge when margining function is enabled. Suggestion:

The initial duty cycle is not properly configured (refer to Section 2.6). Use the Excel worksheet to calculate optimal initial duty cycle and set the configuration accordingly (see Figure 10).

# 6 Conclusion

The UCD90xxx devices provide functions to closed-loop margining and trim power supply output voltage with high accuracy. This application report discussed design considerations and provided a design procedure to achieve optimal design.

#### **IMPORTANT NOTICE**

Texas Instruments Incorporated and its subsidiaries (TI) reserve the right to make corrections, enhancements, improvements and other changes to its semiconductor products and services per JESD46, latest issue, and to discontinue any product or service per JESD48, latest issue. Buyers should obtain the latest relevant information before placing orders and should verify that such information is current and complete. All semiconductor products (also referred to herein as "components") are sold subject to TI's terms and conditions of sale supplied at the time of order acknowledgment.

TI warrants performance of its components to the specifications applicable at the time of sale, in accordance with the warranty in TI's terms and conditions of sale of semiconductor products. Testing and other quality control techniques are used to the extent TI deems necessary to support this warranty. Except where mandated by applicable law, testing of all parameters of each component is not necessarily performed.

TI assumes no liability for applications assistance or the design of Buyers' products. Buyers are responsible for their products and applications using TI components. To minimize the risks associated with Buyers' products and applications, Buyers should provide adequate design and operating safeguards.

TI does not warrant or represent that any license, either express or implied, is granted under any patent right, copyright, mask work right, or other intellectual property right relating to any combination, machine, or process in which TI components or services are used. Information published by TI regarding third-party products or services does not constitute a license to use such products or services or a warranty or endorsement thereof. Use of such information may require a license from a third party under the patents or other intellectual property of the third party, or a license from TI under the patents or other intellectual property of TI.

Reproduction of significant portions of TI information in TI data books or data sheets is permissible only if reproduction is without alteration and is accompanied by all associated warranties, conditions, limitations, and notices. TI is not responsible or liable for such altered documentation. Information of third parties may be subject to additional restrictions.

Resale of TI components or services with statements different from or beyond the parameters stated by TI for that component or service voids all express and any implied warranties for the associated TI component or service and is an unfair and deceptive business practice. TI is not responsible or liable for any such statements.

Buyer acknowledges and agrees that it is solely responsible for compliance with all legal, regulatory and safety-related requirements concerning its products, and any use of TI components in its applications, notwithstanding any applications-related information or support that may be provided by TI. Buyer represents and agrees that it has all the necessary expertise to create and implement safeguards which anticipate dangerous consequences of failures, monitor failures and their consequences, lessen the likelihood of failures that might cause harm and take appropriate remedial actions. Buyer will fully indemnify TI and its representatives against any damages arising out of the use of any TI components in safety-critical applications.

In some cases, TI components may be promoted specifically to facilitate safety-related applications. With such components, TI's goal is to help enable customers to design and create their own end-product solutions that meet applicable functional safety standards and requirements. Nonetheless, such components are subject to these terms.

No TI components are authorized for use in FDA Class III (or similar life-critical medical equipment) unless authorized officers of the parties have executed a special agreement specifically governing such use.

Only those TI components which TI has specifically designated as military grade or "enhanced plastic" are designed and intended for use in military/aerospace applications or environments. Buyer acknowledges and agrees that any military or aerospace use of TI components which have *not* been so designated is solely at the Buyer's risk, and that Buyer is solely responsible for compliance with all legal and regulatory requirements in connection with such use.

TI has specifically designated certain components as meeting ISO/TS16949 requirements, mainly for automotive use. In any case of use of non-designated products, TI will not be responsible for any failure to meet ISO/TS16949.

| Products<br>Audio<br>Amplifiers<br>Data Converters<br>DLP® Products | www.ti.com/audio<br>amplifier.ti.com<br>dataconverter.ti.com<br>www.dlp.com | Applications<br>Automotive and Transportation<br>Communications and Telecom<br>Computers and Peripherals<br>Consumer Electronics | www.ti.com/automotive<br>www.ti.com/communications<br>www.ti.com/computers<br>www.ti.com/consumer-apps |

|---------------------------------------------------------------------|-----------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------|

| DSP                                                                 | dsp.ti.com                                                                  | Energy and Lighting                                                                                                              | www.ti.com/energy                                                                                      |

| Clocks and Timers                                                   | www.ti.com/clocks                                                           | Industrial                                                                                                                       | www.ti.com/industrial                                                                                  |

| Interface                                                           | interface.ti.com                                                            | Medical                                                                                                                          | www.ti.com/medical                                                                                     |

| Logic                                                               | logic.ti.com                                                                | Security                                                                                                                         | www.ti.com/security                                                                                    |

| Power Mgmt                                                          | power.ti.com                                                                | Space, Avionics and Defense                                                                                                      | www.ti.com/space-avionics-defense                                                                      |

| Microcontrollers                                                    | microcontroller.ti.com                                                      | Video and Imaging                                                                                                                | www.ti.com/video                                                                                       |

| RFID                                                                | www.ti-rfid.com                                                             |                                                                                                                                  |                                                                                                        |

| OMAP Applications Processors                                        | www.ti.com/omap                                                             | TI E2E Community                                                                                                                 | e2e.ti.com                                                                                             |

| Wireless Connectivity                                               | www.ti.com/wirelessconne                                                    | ctivity                                                                                                                          |                                                                                                        |

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2016, Texas Instruments Incorporated