SNAA311-September 2017

# **Clocking for Medical Ultrasound Systems**

Ravindra Munvar, Christian Schmoeller, Julian Hagedorn, Leni Skariah, Arvind Sridhar

## ABSTRACT

This application note discusses the importance of clocking in Ultrasound and also illustrates how some key TI devices achieve very low end to end jitter and phase noise. The application note also demonstrates how various stages have very low additive jitter.

### Contents

| 1 | Introduction           | 2 |

|---|------------------------|---|

| 2 | Clock Tree             | 4 |

| 3 | Summary and Conclusion | 8 |

## List of Figures

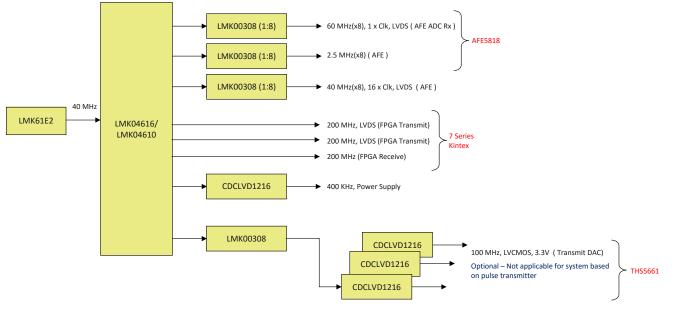

| 1  | Front End Unit and Back End Unit   | 4 |

|----|------------------------------------|---|

| 2  | Front End Alone                    | 4 |

| 3  | Different Clocking Components      | 5 |

| 4  | Demonstration 1, LMK61E2           | 5 |

| 5  | Demonstration 2, LMK04803          | 6 |

| 6  | Demonstration 2, LMK04610          | 6 |

| 7  | Demonstration 3, LMK0030X          | 6 |

| 8  | Comparison of LMK04803 to LMK0030X | 7 |

| 9  | Comparison of LMK0461X Series      | 7 |

| 10 | LMK0461X Frequency Combinations    | 7 |

|    |                                    |   |

### List of Tables

| 1 | Clock Requirement for 128-Channel Cart-Based Ultrasound System | 3 |

|---|----------------------------------------------------------------|---|

| 2 | REF IN                                                         | 4 |

## Trademarks

All trademarks are the property of their respective owners.

# 1 Introduction

Medical Ultrasound systems use Sound waves to generate images of the body. They do this by transmitting an Ultrasound wave into the body and then receiving the echo. This echo is processed to generate an image.

This transmission and reception of the ultrasound signals has to be highly synchronized – to achieve the best results. Precision Clocking is crucial to ensure that the information displayed has minimum artifacts.

Phase noise (frequency domain) or Jitter (time domain) is a measure of how much a clock signal's phase or switching edge deviates from its ideal position and is an important parameter that can determine the impact of reference clocks on the ultrasound image. For example, ultrasound often uses the Doppler Effect to determine the direction and magnitude of blood flow. Higher phase noise can lead to artifacts occurring in Doppler images – such as speckles – which represent errors in the calculation and display of blood flow. In Doppler imaging, the strong reflection from close surfaces and weak signals from higher depths – results in a high dynamic range and jitter on the reference clock can potentially create undesired artifacts.

TI's high performance AFEs need a jitter performance of less than 800 fs to 1 ps to perform optimally especially in the CW Doppler mode.

There are various subsystems in the Ultrasound systems which need clocking:

- 1. Front End:

- (a) Transmit Pulsers Need several copies of very low jitter, high frequency clocks in the range of 160 MHz+ to achieve good beam focusing. (An example of ultra-low jitter reference source from TI is the LMK61E2 family of crystal oscillators. Examples of ultra-low additive jitter buffers from TI that can be used to distribute low noise reference clocks are CDCLVC1310, LMK0030X, and so forth)

- (b) Receive AFEs Require several low skew copies of highly synchronized clocks for all the AFEs to ensure that the data is sampled simultaneously. Frequencies are in the range of 40 to 80 MHz. (An example of a low skew distribution buffer family from TI is LMK0030X.)

- (c) CW Doppler Requires two very-low phase noise clocks which are crucial to determine the frequency shift. Range from 2 to 128 MHz. (An example of a high performance dual-loop jitter attenuator/clock generator device family from TI suitable for generating CW Doppler clocks is LMK048xx or LMK0461x.)

- (d) Beam-forming FPGAs For transmit and receive beam-forming the clocks need to be highly synchronized (LMK0030x fanout buffers). Transmit beam-forming focuses the ultrasound wavefront. Precise timing is required and any variation in the clock edges (jitter) can lead to loss of focus. The losses of precise synchronization between transmit and receive beamforming can also result in loss of image resolution.

- (e) FPGAs can also be used to generate the clocks needed for transmit and receive timing, but the jitter performance of these clocks is typically not nearly as good as specialized clocking ICs. The jitter then needs to be cleaned by external jitter cleaners. (Examples of high-performance, dual-loop jitter attenuators from TI include LMK04610 and LMK0480x.)

- 2. Power Supply:

- (a) All the power supplies within the Ultrasound system are often synchronized to one master clock to avoid the effects of switching noise appearing as artifacts in the image (through filtering). These power supplies typically operate in the range of 100 kHz to 1 MHz. Higher switching frequencies often result in smaller magnetic components but also operate closer to the dynamic range of the ultrasound signals themselves. Synchronizing all switching power supplies to the same (lower) frequency and then filtering at that frequency can avoid any coupling of this noise into the ultrasound signal chain. In addition, spread spectrum clocking can help to reduce EMI effects. (Examples of flexible clock generators with spread-spectrum generation capability used to minimize EMI in the system includes CDCE913 and CDCE6214)

- (b) Once the signals are digitized and provided to the digital post-processing sub-systems, the jitter is then not as critical. However it is desirable to have clean clocks throughout the entire system – to ensure maximum performance and lower overall noise in the system.

- (a) FPGAs for image processing require frequencies which include the sampling frequency and others needed for communication and internal logic blocks. (CDCM6208, LMK033x8, CDCE6214, LMK60xx)

- (b) DSPs and Processors for image processing require common frequencies like 100 MHz. (CDCM6208, LMK03328, CDCE6214)

- (c) External communication PCI, PCI Express, USB, Ethernet, and so forth, that typically require 24-, 48-, and 100-MHz clocks (CDCM6208, CDCE6214)

System designers prefer using clocks with the features as listed as follows:

- 1. Low power dissipation (LMK04610, CDCE6214)

- 2. Programmability and scalability to support additional features or variations at a later date without change in hardware. (LMK61E2 reference oscillator, any LMK or CDC clock generator)

- 3. High integration (less number of parts and smaller board real estate) (LMK04610, LMK04803, LMK03328, CDCE913, and so on.)

- 4. Fully-differential clocking wherever possible in the signal chain (common mode noise rejection).

Precision clocking can be achieved by having ultra-low noise clock sources, generators/dividers, distributors and buffers. The clocks generators are accurate and typically have lower phase noise when integer mode PLL and output dividers are used versus fractional mode PLL and/or fractional output dividers – that could introduce additional phase noise and potentially some small frequency synthesis error.

The impact can be minimized by ensuring that the front-end signal chain uses exclusively integer dividers to generate the clocks needed for the front end.

For the fanout of clock signals it is important to select buffers with very low additive jitter, otherwise the noise floor of a high quality source clock (that is, LMK61E2) would degrade significantly each time it is buffered. Suitable Buffers for this kind of application are the LMK0030x family (differential) and the CDCLVC1310 (LVCMOS), that have very low additive jitter.

TI's clock generator, dividers and low jitter buffers are some key components which help achieve this required performance.

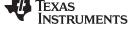

Table 1 and the Figure 1 show a typical clock tree for an Ultrasound system. This clock tree demonstrates the use of various reference clocks for different building blocks – Transmit, Receive, FPGAs, Processors, power supply, and so on.

| NO OF CLKS | FREQUENCY          | FORMAT | TARGET          | PERFORMANCE      |

|------------|--------------------|--------|-----------------|------------------|

| 128        | 100 MHz            | LVCMOS | DAC + AMP Clock | Good Phase Noise |

| 2          | 40 MHz             | LVCMOS | CW Mixer        | Good Phase Noise |

| 2          | 120 MHz            | LVDS   | FPGA (AWG)      |                  |

| 2          | 200 MHz            | LVDS   | FPAG (Transmit) |                  |

| 1          | 200 MHz            | LVDS   | FPGA (Receive)  |                  |

| 16         | 100 kHz to 500 kHz | LVCMOS | Power Supply    |                  |

| 8          | 128 MHz            | LVDS   | AFE             | Good Phase Noise |

| 8          | 80 MHz             | LVDS   | AFE             | Good Phase Noise |

| 8          | 8 MHz              | LVDS   | AFE             | Good Phase Noise |

| 1          | 122.88 MHz         | LVDS   | DSP             |                  |

| 3          | 100 MHz            | LVDS   | DSP             |                  |

| 1          | 24.576 MHz         | LVCMOS | Audio Codec     |                  |

Table 1. Clock Requirement for 128-Channel Cart-Based Ultrasound System

Introduction

### Table 2. REF IN

| VALUE  |        |         |         |         |         |  |  |

|--------|--------|---------|---------|---------|---------|--|--|

| 80 MHz | 96 MHz | 100 MHz | 160 MHz | 200 MHz | 320 MHz |  |  |

## 2 Clock Tree

Example 1: Clock tree for 128-channel ultrasound cart-based system.

Figure 1. Front End Unit and Back End Unit

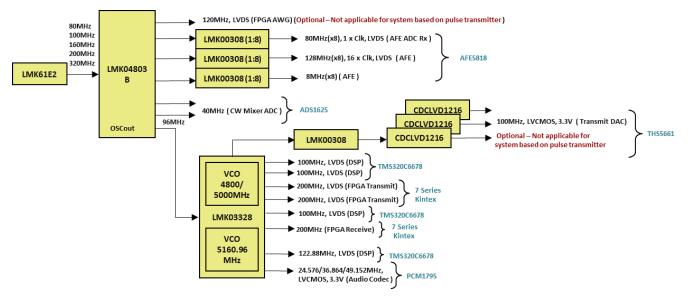

**Example 2:** Clock tree for 128-channel cart-based ultrasound system (for front end alone) using low-power, ultra-low-jitter clock generator – LMK04610 or LMK04616

Tests were conducted to demonstrate the total additive jitter and also jitter in various clock configurations for the clock tree by using individual evaluation modules from the different clocking components.

Figure 3. Different Clocking Components

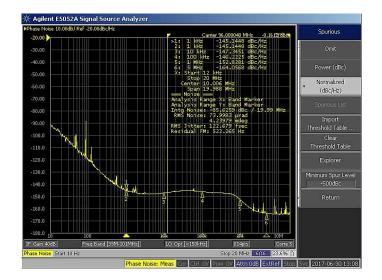

The following graphs demonstrate the noise performance of the actual signals as measured on a signal source analyzer.

## **Demonstration 1:**

Reference = 80 MHz LVDS (Output signal with and without Spurs) Integrated. Integrated RMS Jitter (10 kHz – 20 MHz) – 122 fs

## Figure 4. Demonstration 1, LMK61E2

### Clock Tree

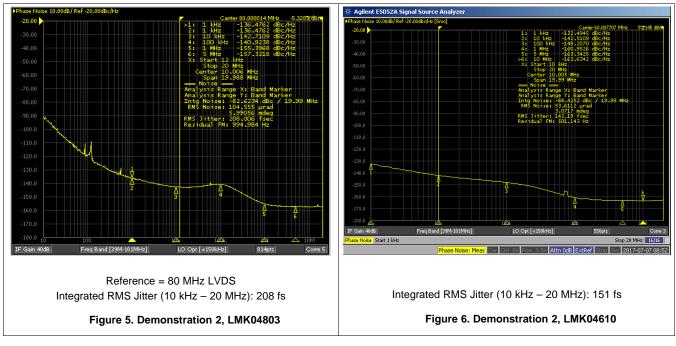

## **Demonstration 2:**

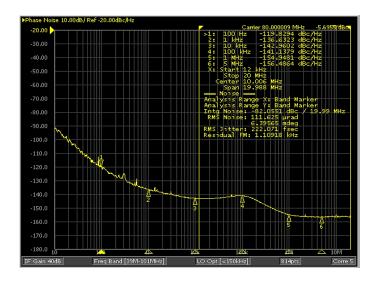

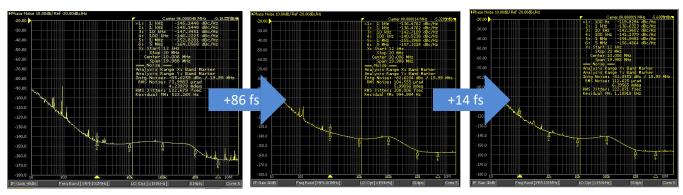

**Demonstration 3:**

80 MHz Integrated RMS Jitter (10 kHz – 20 MHz) – 222 fs

## Figure 7. Demonstration 3, LMK0030X

A comparison of all the three demonstrates the following:

- The integrated RMS jitter from the output of LMK61E2 to LMK04803 increases by +86 fs. The integrated RMS jitter from the output of LMK04803 to LMK0030X increases by 14 fs.

- The total increase in the integrated RMS Jitter from Source to destination is just 100 fs.

Figure 8. Comparison of LMK04803 to LMK0030X

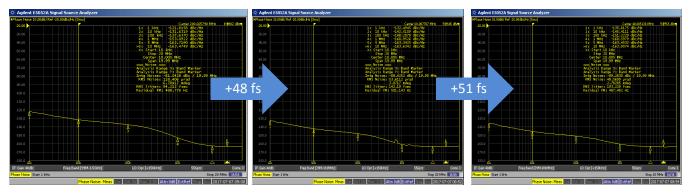

Using LMK0461X series device helps reduce the total additive jitter as in Figure 9.

Figure 9. Comparison of LMK0461X Series

Using LMK0461X certain frequency combinations can also result in lower jitter as shown in Figure 10. Even if the input Jitter is high, the LMK04610 acts as a jitter cleaner and can deliver much better results – 94 fs Jitter against the input jitter of 122 fs. Figure 10 has input of 40 MHz and an output of 200 MHz. So an appropriate selection of input and output frequencies can deliver good phase noise and jitter along with appropriate Clock generator devices

#### Summary and Conclusion

Figure 10. LMK0461X Frequency Combinations

## 3 Summary and Conclusion

- The TI LMK series of Clock devices offer excellent additive jitter performance throughout the entire clock chain – which are ideally suited for Ultrasound applications.

- As noted above, the end to end jitter is well within the required limits of TI's high performance AFEs to achieve optimal performance. This low end to end jitter of TI's clock devices allows system designers sufficient headroom to take care of other factors and noise that might impact the clock performance in the system.

- For typical Ultrasound applications it is possible to achieve superior clocking performance by ensuring very low reference clock phase noise and edge jitter.

- With the scheme and block diagram presented in the previous sections, a 320-MHz source provided the best overall clocking system performance.

- If different reference frequencies are selected, TI provides a wide choice of other high performance dual-loop jitter attenuator/clock generator devices like the LMK046XX family – which offers additional benefits as:

- 1. Lower noise floor

- 2. Higher phase detector operating rates that reduces PLL noise further

- 3. Better VCO noise performance

- 4. Integrated LDOs

- 5. Low power

### IMPORTANT NOTICE FOR TI DESIGN INFORMATION AND RESOURCES

Texas Instruments Incorporated ('TI") technical, application or other design advice, services or information, including, but not limited to, reference designs and materials relating to evaluation modules, (collectively, "TI Resources") are intended to assist designers who are developing applications that incorporate TI products; by downloading, accessing or using any particular TI Resource in any way, you (individually or, if you are acting on behalf of a company, your company) agree to use it solely for this purpose and subject to the terms of this Notice.

TI's provision of TI Resources does not expand or otherwise alter TI's applicable published warranties or warranty disclaimers for TI products, and no additional obligations or liabilities arise from TI providing such TI Resources. TI reserves the right to make corrections, enhancements, improvements and other changes to its TI Resources.

You understand and agree that you remain responsible for using your independent analysis, evaluation and judgment in designing your applications and that you have full and exclusive responsibility to assure the safety of your applications and compliance of your applications (and of all TI products used in or for your applications) with all applicable regulations, laws and other applicable requirements. You represent that, with respect to your applications, you have all the necessary expertise to create and implement safeguards that (1) anticipate dangerous consequences of failures, (2) monitor failures and their consequences, and (3) lessen the likelihood of failures that might cause harm and take appropriate actions. You agree that prior to using or distributing any applications. TI has not conducted any testing other than that specifically described in the published documentation for a particular TI Resource.

You are authorized to use, copy and modify any individual TI Resource only in connection with the development of applications that include the TI product(s) identified in such TI Resource. NO OTHER LICENSE, EXPRESS OR IMPLIED, BY ESTOPPEL OR OTHERWISE TO ANY OTHER TI INTELLECTUAL PROPERTY RIGHT, AND NO LICENSE TO ANY TECHNOLOGY OR INTELLECTUAL PROPERTY RIGHT OF TI OR ANY THIRD PARTY IS GRANTED HEREIN, including but not limited to any patent right, copyright, mask work right, or other intellectual property right relating to any combination, machine, or process in which TI products or services are used. Information regarding or referencing third-party products or services does not constitute a license to use such products or services, or a warranty or endorsement thereof. Use of TI Resources may require a license from a third party under the patents or other intellectual property of the third party, or a license from TI under the patents or other intellectual property of TI.

TI RESOURCES ARE PROVIDED "AS IS" AND WITH ALL FAULTS. TI DISCLAIMS ALL OTHER WARRANTIES OR REPRESENTATIONS, EXPRESS OR IMPLIED, REGARDING TI RESOURCES OR USE THEREOF, INCLUDING BUT NOT LIMITED TO ACCURACY OR COMPLETENESS, TITLE, ANY EPIDEMIC FAILURE WARRANTY AND ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, AND NON-INFRINGEMENT OF ANY THIRD PARTY INTELLECTUAL PROPERTY RIGHTS.

TI SHALL NOT BE LIABLE FOR AND SHALL NOT DEFEND OR INDEMNIFY YOU AGAINST ANY CLAIM, INCLUDING BUT NOT LIMITED TO ANY INFRINGEMENT CLAIM THAT RELATES TO OR IS BASED ON ANY COMBINATION OF PRODUCTS EVEN IF DESCRIBED IN TI RESOURCES OR OTHERWISE. IN NO EVENT SHALL TI BE LIABLE FOR ANY ACTUAL, DIRECT, SPECIAL, COLLATERAL, INDIRECT, PUNITIVE, INCIDENTAL, CONSEQUENTIAL OR EXEMPLARY DAMAGES IN CONNECTION WITH OR ARISING OUT OF TI RESOURCES OR USE THEREOF, AND REGARDLESS OF WHETHER TI HAS BEEN ADVISED OF THE POSSIBILITY OF SUCH DAMAGES.

You agree to fully indemnify TI and its representatives against any damages, costs, losses, and/or liabilities arising out of your noncompliance with the terms and provisions of this Notice.

This Notice applies to TI Resources. Additional terms apply to the use and purchase of certain types of materials, TI products and services. These include; without limitation, TI's standard terms for semiconductor products <a href="http://www.ti.com/sc/docs/stdterms.htm">http://www.ti.com/sc/docs/stdterms.htm</a>), evaluation modules, and samples (<a href="http://www.ti.com/sc/docs/stdterms.htm">http://www.ti.com/sc/docs/stdterms.htm</a>), evaluation

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2017, Texas Instruments Incorporated