# **LC75843UGA**

# Application Note Design method of the LCD system using static (1/1-duty) LCD panel

# Overview

This application note explains the design method of the LCD (Liquid Crystal Display) system using LCD driver IC (LC75843UGA). The LC75843UGA is the 1/1 to 1/4 duty general-purpose LCD driver that can be used in applications such as automotive display by control with the controller.

In addition, this IC is able to drive up to 100 segments directly, and can also control up to four general-purpose output ports. Moreover, it has a built-in 3ch PWM (Pulse Width Modulation) function for brightness adjustment of LED (Light Emitting Diode). Furthermore, because of built-in the oscillator circuit, it is possible to reduce external resister and external capacitor for oscillation.

<sup>•</sup> CCB is ON Semiconductor® 's original format. All addresses are managed by ON Semiconductor® for this format.

<sup>•</sup> CCB is a registered trademark of Semiconductor Components Industries, LLC.

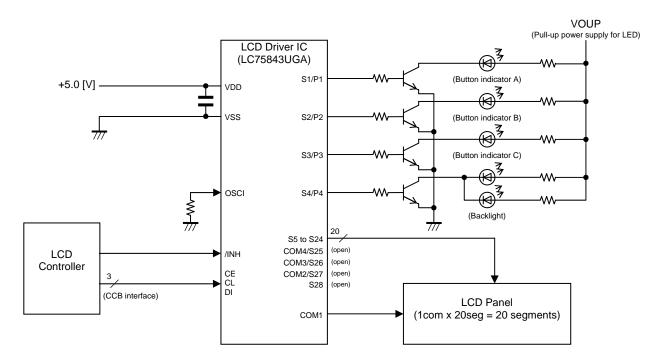

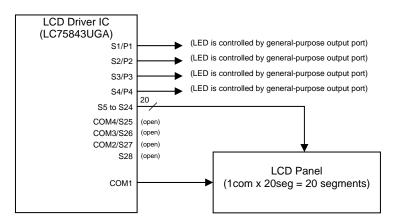

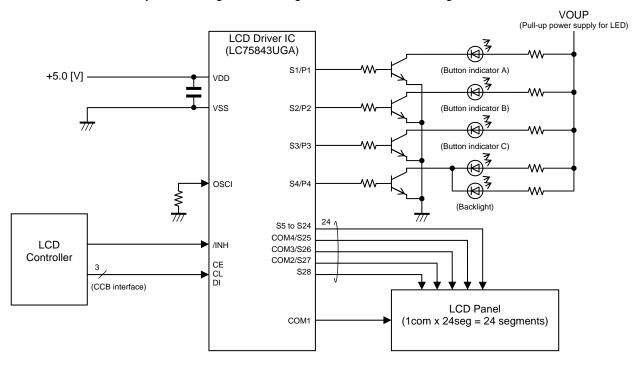

# **LCD System Configuration Example**

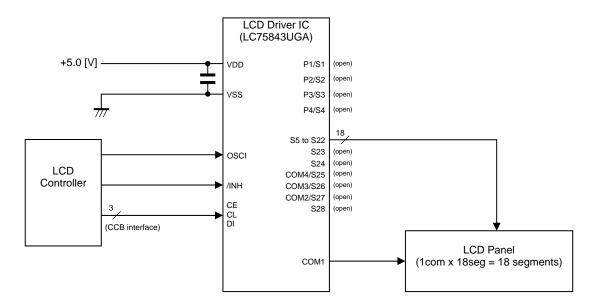

This application note explains various function explanations and setting method example of serial control data in the LCD system configuration using LCD driver IC (LC75843UGA) as shown below.

Figure 1. LCD system configuration using LCD driver IC (LC75843UGA)

### < Operation specifications of the LCD system >

| LCD driver IC (LC75843UGA) specifications                                                                                                                                                                                                 | LCD system specifications of Figure 1                                                                                                            |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------|

| Support for static (1/1-duty) or 1/2-duty or 1/3-duty or 1/4-duty drive. (Capable of driving the LCD up to 100 segments directly)                                                                                                         | The LCD panel to use has 20-segments and 1-common. Total display segments are 20-segments. Therefore, LCD drive duty ratio is static (1/1-duty). |

| Built-in LCD drive bias voltage stabilization circuit.                                                                                                                                                                                    | Unused.                                                                                                                                          |

| Support for up to four general-purpose output ports                                                                                                                                                                                       | The four general-purpose output ports are used.                                                                                                  |

| Support for the PWM output function of a maximum of 3ch.                                                                                                                                                                                  | Control of the LED by PWM function.                                                                                                              |

| Support for clock output function of 1ch.                                                                                                                                                                                                 | Unused.                                                                                                                                          |

| Incorporation of an oscillator circuit (Incorporation of resistor and capacitor for an oscillation), and setting of the "Internal oscillator operating mode" or "External clock input operating mode" is possible by serial control data. | Internal oscillator operating mode is used.                                                                                                      |

| Serial control data input supports CCB* format communication with the system controller. (Support 3.3V and 5.0V operation)                                                                                                                | Used. (Controlled by LCD controller)                                                                                                             |

| Adjustment of the frame frequency of the LCD drive waveform is possible by serial control data.                                                                                                                                           | Frame frequency is adjusted, but frequency value is undecided.                                                                                   |

| Adjustment of the frame frequency of the PWM drive waveform is possible by serial control data.                                                                                                                                           | PWM is controlled, but frequency value is undecided.                                                                                             |

| Setting of the power saving mode or the all segments turn off mode is possible by serial control data.                                                                                                                                    | Used. (Controlled by LCD controller)                                                                                                             |

| The /INH pin allows the display to be forced off state.                                                                                                                                                                                   | Used. (Controlled by LCD controller)                                                                                                             |

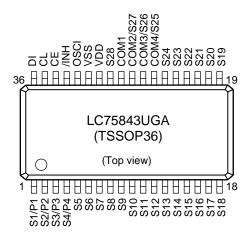

# **Pin Assignment**

The following figure shows the pin assignment of LCD driver IC (LC75843UGA).

Figure 2. Pin Assignment of LCD driver IC (LC75843UGA)

Table 1. Pin function of LCD driver IC (LC75843UGA)

| Pin name  | Pin function                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|-----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| S1/P1     | General-purpose port output pin. The S1/P1 pin can be used as a segment drive pin by control data (P0 to P2).                                                                                                                                                                                                                                                                                                                                             |

| S2/P2     | General-purpose port output pin.  The S2/P2 pin can be used as a segment drive pin by control data (P0 to P2).                                                                                                                                                                                                                                                                                                                                            |

| S3/P3     | General-purpose port output pin.  The S3/P3 pin can be used as a segment drive pin by control data (P0 to P2).                                                                                                                                                                                                                                                                                                                                            |

| S4/P4     | General-purpose port output pin.  The S4/P4 pin can be used as a segment drive pin by control data (P0 to P2).                                                                                                                                                                                                                                                                                                                                            |

| S5 to S24 | Segment drive output pins.                                                                                                                                                                                                                                                                                                                                                                                                                                |

| S28       | Segment drive output pin. When "S28 output off mode (DN=0)", S28 is VSS level output. When "S28 output on mode (DN=1)", S28 is segment output.                                                                                                                                                                                                                                                                                                            |

| COM1      | Common drive output pin.                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| COM2/S27  | Common drive or segment drive output pin. The COM2/S27 pin can be used as a segment drive pin by control data (DT0, DT1).                                                                                                                                                                                                                                                                                                                                 |

| COM3/S26  | Common drive or segment drive output pin. The COM3/S26 pin can be used as a segment drive pin by control data (DT0, DT1).                                                                                                                                                                                                                                                                                                                                 |

| COM4/S25  | Common drive or segment drive output pin. The COM4/S25 pin can be used as a segment drive pin by control data (DT0, DT1).                                                                                                                                                                                                                                                                                                                                 |

| OSCI      | External clock input pin.  When "Internal oscillator operating mode (OC=0)", make sure to connect OSCI to GND.  When "External clock input mode (OC=1)", OSCI is used to input the external clock.                                                                                                                                                                                                                                                        |

| CE        | Serial data transfer chip enable input pin.                                                                                                                                                                                                                                                                                                                                                                                                               |

| CL        | Serial data transfer synchronization clock input pin.                                                                                                                                                                                                                                                                                                                                                                                                     |

| DI        | Serial data transfer data input pin.                                                                                                                                                                                                                                                                                                                                                                                                                      |

| /INH      | Display off control input pin. /INH=High (VDD): Display ON /INH=Low (VSS): Display forced off General-purpose output port pins (S1/P1 to S4/P4) are VSS level. Segment output pins (S5 to S24, and S28) are VSS level. Common output pins (COM1, COM2/S27, COM3/S26 and COM4/S25) are VSS level. The internal oscillator circuit is stopped. External clock input is inhibited. The reception of serial control data is possible. (Registers are updated) |

| VDD       | Logic power supply pin for LCD driver IC. A power supply voltage of +4.5 [V] to +6.3 [V].                                                                                                                                                                                                                                                                                                                                                                 |

| VSS       | Ground pin. Must be connected all each board to the ground.                                                                                                                                                                                                                                                                                                                                                                                               |

# **Serial Control Data Transfer Explanation**

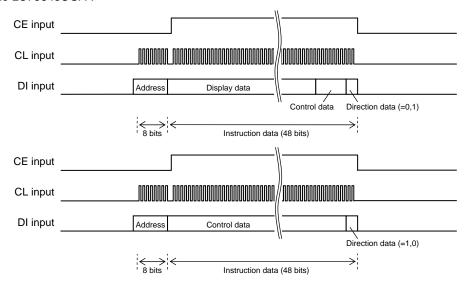

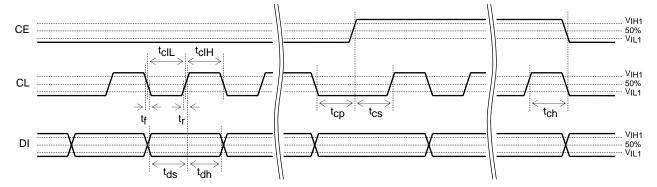

### (1) Basic Timing

The LC75843UGA has several internal registers. These internal registers are written by CCB interface (Serial interface). Structure of transfer bits consists of CCB address and instruction data. First eight bits are CCB address (44h). The bit number of instruction data is different depending on an instruction. The serial control data is taken by the positive edge of the CL signal, which is latched by the negative edge of the CE signal. When the number of data in CE=VDD period is different from the defined number (48-bits), IC does not execute the instruction and holds the old state. Even when CL signal stops at high level, the CCB interface can be received. However, serial Control Data transfer timing (transfer form) is different. Therefore, when designing equipment, refer to the "Delivery specification for the LC75843UGA".

Figure 3. Basic timing when CL signal is stopped at the Low Level

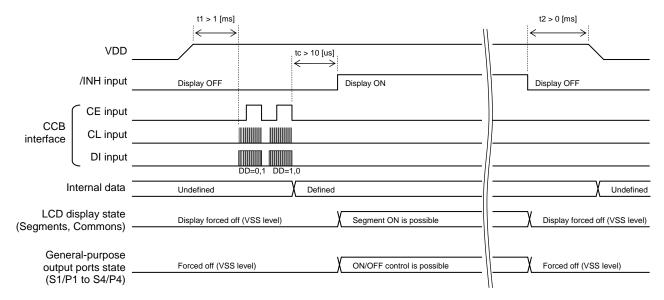

Since the IC internal data is undefined when power supply is first applied, applications should set the /INH pin=Low (VSS) at the same time as power supply is applied to turn off the display (The S1/P1 to S4/P4, S5 to S24, COM4/S25, COM3/S26, COM2/S27, COM1 and S28 pins are outputted at the VSS level), and during this period send serial control data from the controller. The controller should then set the /INH pin=High (VDD) after the data transfer has completed. This procedure prevents meaningless display at power supply on.

Figure 4. Basic timing of serial control data transfer

# (2) Allowable Operating Ranges of the Serial Control Data Transfer

The following figure shows the specifications of the allowable operating ranges when CL signal is stopped at the low level.

Figure 5. Allowable operating ranges of serial control data transfer

Table 2. Allowable operating ranges

| Parameter                                               | Symbol           | Conditions                                  | Min.                | Тур. | Max.                | Unit |

|---------------------------------------------------------|------------------|---------------------------------------------|---------------------|------|---------------------|------|

| Power Supply Voltage                                    | $V_{DD}$         | VDD                                         | 4.5                 |      | 6.3                 | V    |

| Input High Level Voltage                                | V <sub>IH1</sub> | CE, CL, DI, /INH                            | 0.4 V <sub>DD</sub> |      | 6.3                 | V    |

| Input Low Level Voltage                                 | V <sub>IL1</sub> | CE, CL, DI, /INH                            | 0                   |      | 0.2 V <sub>DD</sub> | V    |

| Serial Data Transfer<br>Synchronization Clock Frequency | <sup>f</sup> cl  | CL, 1/(t <sub>CIL</sub> +t <sub>CIH</sub> ) |                     |      | 3.125               | MHz  |

| Data Setup Time                                         | t <sub>ds</sub>  | CL, DI                                      | 160                 |      |                     | ns   |

| Data Hold Time                                          | <sup>t</sup> dh  | CL, DI                                      | 160                 |      |                     | ns   |

| CE Wait Time                                            | t <sub>cp</sub>  | CE, CL                                      | 160                 |      |                     | ns   |

| CE Setup Time                                           | t <sub>CS</sub>  | CE, CL                                      | 160                 |      |                     | ns   |

| CE Hold Time                                            | t <sub>ch</sub>  | CE, CL                                      | 160                 |      |                     | ns   |

| High Level Clock Pulse Width                            | <sup>t</sup> clH | CL                                          | 160                 |      |                     | ns   |

| Low Level Clock Pulse Width                             | t <sub>CIL</sub> | CL                                          | 160                 |      |                     | ns   |

| Rise Time                                               | t <sub>r</sub>   | CE, CL, DI                                  |                     | 160  |                     | ns   |

| Fall Time                                               | t <sub>f</sub>   | CE, CL, DI                                  |                     | 160  |                     | ns   |

| /INH Switching Time                                     | t <sub>C</sub>   | /INH, CE                                    | 10                  |      |                     | us   |

These specifications show an example, and, we have a case to change these specifications without a notice for improvement. Therefore, it is not guaranteed for design as the mass production equipment. When designing equipment, refer to the "Delivery specification for the LC75843UGA".

Functional operation above the stresses listed in the Recommended Operating Ranges is not implied. Extended exposure to stresses beyond the Recommended Operating Ranges limits may affect device reliability.

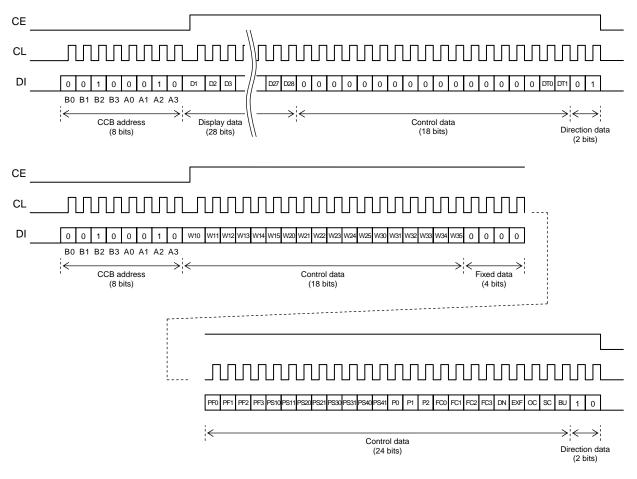

### (3) Allotment of Serial Control Data

The following figure shows the serial control data transfer form when the "Static (1/1-duty) drive mode" and CL signal is stopped at the low level.

B0 to B3, A0 to A3 : CCB address. (=44h)

D1 to D28 : Display data setting registers.

DT0, DT1

: LCD drive type (Duty ratio, Bias ratio) setting registers.

W10 to W15

: PWM duty setting registers of the PWM output function (ch1).

W20 to W25

: PWM duty setting registers of the PWM output function (ch2).

W30 to W35

PF0 to PF3

PS10, PS11

PS20, PS21

PS30, PS31

PS40, PS41

PS40, PS40, PS41

PS40, PS40, PS41

PS40, PS40, PS41

PS40, P

P0 to P2 : S1/P1 to S4/P4 output pins function setting registers.

FC0 to FC3 : LCD drive waveform frame frequency setting registers.

DN : S28 pin function setting register.

EXF : External clock operating frequency setting register. (When OC=1, EXF is valid.)

OC : Fundamental clock operating mode setting register. SC : All segments turn off mode setting register.

BU : Power saving mode setting register.

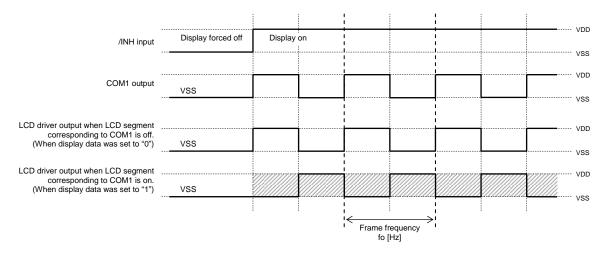

# **Explanation of the LCD drive control**

Figure 6. Peripheral circuits configuration example of the LCD driver outputs

# (1) LCD Drive Waveform

It is explanation about the drive type of the static (1/1-duty). The common output (COM1) repeat VDD level and VSS level in turn. On the other hand, the segment outputs (S5 to S28) repeat VSS level and VDD level by a state of display ON/OFF (Display data setting register is 1/0). When the LCD segment is ON (It interrupt light), the potential difference of segment output and common output becomes VDD level. When the LCD segment is OFF (It penetrate light), the potential difference of segment output and common output becomes zero. This drive method assigns all frames to control of ON/OFF of one segment. Thus, this drive method is called the "Static drive" or "1/1-duty drive". When set the "Static (1/1-duty) drive mode", the following figure shows the LCD drive waveform.

Figure 7. LCD driver output waveform

### (2) LCD Drive Type Setting (DT0, DT1)

The registers of the DT0 and DT1 can set the LCD drive type from 1/1-duty to 1/4-duty. The LCD system configuration example is LCD panel of the static (1/1-duty) drive used. Therefore, this system sets DT0=1 and DT1=1.

| DT0 | DT1 | LCD drive type                   | LCD drive type | Output p | Output pins state |          |  |

|-----|-----|----------------------------------|----------------|----------|-------------------|----------|--|

| DIO | ווט | LCD drive type                   | COM1           | COM2/S27 | COM3/S26          | COM4/S25 |  |

| 0   | 0   | 1/4-duty and 1/3-bias drive type | COM1           | COM2     | COM3              | COM4     |  |

| 1   | 0   | 1/3-duty and 1/3-bias drive type | COM1           | COM2     | COM3              | S25      |  |

| 0   | 1   | 1/2-duty and 1/2-bias drive type | COM1           | COM2     | S26               | S25      |  |

| 1   | 1   | Static (1/1-duty) drive type     | COM1           | S27      | S26               | S25      |  |

# (3) S28 Pin Function Setting (DN)

The DN register can set the "Segment output of the S28 output pin" or "VSS level output of the S28 output pin". The LCD system configuration example does not use S28 output pin. Therefore, this system sets DN=0.

| DN | S28 output pin state |

|----|----------------------|

| 0  | VSS level output     |

| 1  | S28 segment output   |

### (4) Display Data Setting (D1 to D28)

The registers from D1 to D28 set the LCD segment ON/OFF, or these registers set the general-purpose output port (P1 to P4) of high level output or low level output. The LCD system configuration example is the "Static (1/1-duty) drive mode", and LCD segments from S5 to S24 used. Therefore, set the LCD display data from D5 to D24. In addition, the pins from S1/P1 to S4/P4 use general-purpose output port function. Therefore, set the general-purpose output ports (P1 to P4) of high level output or low level output by the LCD display data from D1 to D4. About the control method of "Display data setting registers (D1 to D4)", refer to paragraph (3) of "Explanation of the LED Control by General-purpose Output Ports".

When set the "Static (1/1-duty) drive mode", the following table shows the relation between the "Display data setting registers (D5 to D24)" and the segment outputs and the common outputs.

| Output pin | COM1 | Notes                                              |

|------------|------|----------------------------------------------------|

| S5         | D5   |                                                    |

| S6         | D6   |                                                    |

| <b>S</b> 7 | D7   |                                                    |

| S8         | D8   |                                                    |

| S9         | D9   |                                                    |

| S10        | D10  |                                                    |

| S11        | D11  |                                                    |

| S12        | D12  |                                                    |

| S13        | D13  |                                                    |

| S14        | D14  |                                                    |

| S15        | D15  |                                                    |

| S16        | D16  |                                                    |

| S17        | D17  |                                                    |

| S18        | D18  |                                                    |

| S19        | D19  |                                                    |

| S20        | D20  |                                                    |

| S21        | D21  |                                                    |

| S22        | D22  |                                                    |

| S23        | D23  |                                                    |

| S24        | D24  |                                                    |

| COM4/S25   | D25  | This display data is unused, and D25 sets the "0". |

| COM3/S26   | D26  | This display data is unused, and D26 sets the "0". |

| COM2/S27   | D27  | This display data is unused, and D27 sets the "0". |

| S28        | D28  | This display data is unused, and D28 sets the "0". |

For example, the following table shows the relation between the "Display data setting register" and S5 output pin state.

| Display data | CE output pip state                       |

|--------------|-------------------------------------------|

| D5           | S5 output pin state                       |

| 0            | LCD segment corresponding to COM1 is off. |

| 1            | LCD segment corresponding to COM1 is on.  |

# **Explanation of the LED Control by General-purpose Output Ports**

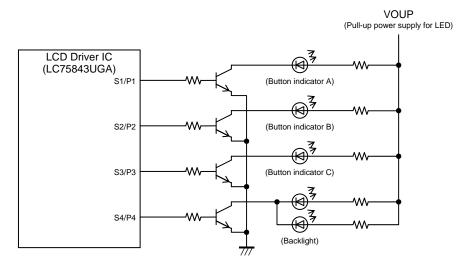

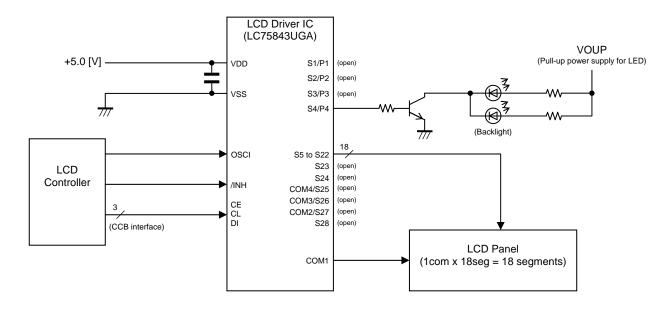

Figure 8. Peripheral circuits configuration example of the general-purpose output ports

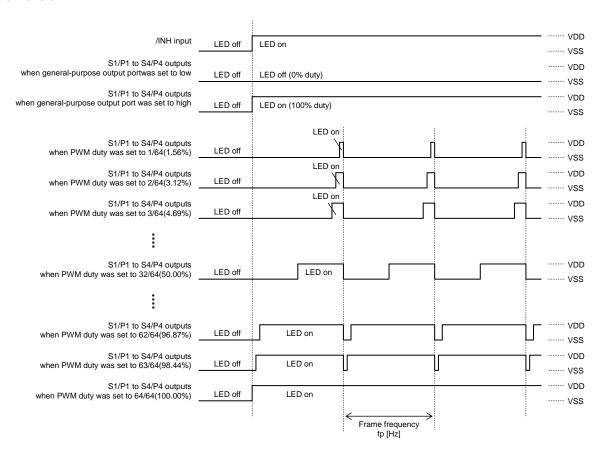

### (1) LED Control Waveform

The LC75843UGA has up to four general-purpose output ports. In addition, the PWM output function has up to 3ch and can perform brightness adjustment of the LED individually for each channel. The brightness of the LED has a method to adjust a forward current of LED flowing at the time of ON, or there is pulse width modulation (PWM) control to adjust the apparent brightness by repeating ON and OFF at high speed. The LED looks bright if the ON time per unit time by PWM control is long. In addition, it looks dark if the ON time per unit time by PWM control is short. When LED is always turn on (Brightness is 100%), the consumption electric current is maximum. When LED is ON, the LED uses electricity, and when LED is OFF, the LED does not use electricity. Thus, it can set the low power consumption by PWM control. When used the general-purpose output port, the following figure shows the LED control waveform.

Figure 9. General-purpose port output waveform

# (2) S1/P1 to S4/P4 Output Pins Function Setting (P0 to P2)

The registers from P0 to P2 can set the "Output pins from S1/P1 to S4/P4 of the segment output port" or "Output pins from S1/P1 to S4/P4 of the general-purpose output port". The LCD system configuration example controls LED by general-purpose output port of the S1/P1 to S4/P4 output pins. Therefore, this system sets P0=1, P1=0 and P2=0.

| P0 | P1 | P2 | Output pin state |       |       |       |

|----|----|----|------------------|-------|-------|-------|

| PU | PI | P2 | S1/P1            | S2/P2 | S3/P3 | S4/P4 |

| 0  | 0  | 0  | S1               | S2    | S3    | S4    |

| 0  | 0  | 1  | P1               | S2    | S3    | S4    |

| 0  | 1  | 0  | P1               | P2    | S3    | S4    |

| 0  | 1  | 1  | P1               | P2    | P3    | S4    |

| 1  | 0  | 0  | P1               | P2    | P3    | P4    |

| 1  | 0  | 1  | S1               | S2    | S3    | S4    |

| 1  | 1  | 0  | S1               | S2    | S3    | S4    |

| 1  | 1  | 1  | S1               | S2    | S3    | S4    |

S1 to S4 : Segment output ports P1 to P4 : General-purpose output ports

# (3) General-purpose Ports (P1 to P4) Function Setting (PS10,PS11,PS20,PS21,PS30,PS31,PS40 and PS41)

The registers from PS10 and PS11 can set the "General-purpose output function", "Clock output function", or "PWM output function" of the general-purpose output port (P1). In addition, PS20, PS21, PS30, PS31, PS40 and PS41 registers can set the "General-purpose output function" or "PWM output function" of the general-purpose output ports (P2 to P4). The general-purpose output function outputs general-purpose output ports (P1 to P4) of high level or low level by "Display data setting registers (D1 to D4)". The clock output function outputs internal oscillator clock (fosc) or external clock input (fck) of the 1/2 frequency division or 1/8 frequency division. This function can set only general-purpose output port (P1). Therefore, when stop the clock, the "Display data setting register (D1)" by general-purpose output function sets the "0", and general-purpose output port (P1) outputs low level. The PWM output function has up to 3ch and can perform brightness adjustment of the LED individually for each channel. However, PWM duty setting register (W10 to W15, W20 to W25, and W30 to W35) does not have a setting function of 0%-duty. Therefore when you want to turn off the LED, the "Display data setting registers (D1 to D4)" by general-purpose output function set the "0", and general-purpose output ports (P1 to P4) output low level.

| PS10 | PS11 | General-purpose output port (P1) function                                          |

|------|------|------------------------------------------------------------------------------------|

| 0    | 0    | General-purpose output function : High level or low level output                   |

| 1    | 0    | Clock output function : Outputs a clock of the fosc/2 frequency                    |

| 0    | 1    | Clock output function : Outputs a clock of fosc/8 frequency                        |

| 1    | 1    | PWM output function (ch1): Controlled by PWM duty setting register from W10 to W15 |

| PS20 | PS21 | General-purpose output port (P2) function                                          |

|------|------|------------------------------------------------------------------------------------|

| 0    | 0    | General-purpose output function : High level or low level output                   |

| 1    | 0    | PWM output function (ch1): Controlled by PWM duty setting register from W10 to W15 |

| 0    | 1    | PWM output function (ch2): Controlled by PWM duty setting register from W20 to W25 |

| 1    | 1    | PWM output function (ch3): Controlled by PWM duty setting register from W30 to W35 |

| PS30 | PS31 | General-purpose output port (P3) function                                          |

|------|------|------------------------------------------------------------------------------------|

| 0    | 0    | General-purpose output function : High level or low level output                   |

| 1    | 0    | PWM output function (ch1): Controlled by PWM duty setting register from W10 to W15 |

| 0    | 1    | PWM output function (ch2): Controlled by PWM duty setting register from W20 to W25 |

| 1    | 1    | PWM output function (ch3): Controlled by PWM duty setting register from W30 to W35 |

| PS40 | PS41 | General-purpose output port (P4) function                                          |

|------|------|------------------------------------------------------------------------------------|

| 0    | 0    | General-purpose output function : High level or low level output                   |

| 1    | 0    | PWM output function (ch1): Controlled by PWM duty setting register from W10 to W15 |

| 0    | 1    | PWM output function (ch2): Controlled by PWM duty setting register from W20 to W25 |

| 1    | 1    | PWM output function (ch3): Controlled by PWM duty setting register from W30 to W35 |

The LCD system configuration example uses general-purpose output port function from S1/P1 to S4/P4. The following table shows the relation between the "Display data setting registers (D1 to D4)" and general-purpose output ports (P1 to P4) of high level or low level.

| Display data | Controlled output pin | Notes                                                                                                                                                                                         |

|--------------|-----------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| D1           | S1/P1                 | When PS10=0, PS11=0 and D1=0, S1/P1 is outputted at the low level. When PS10=0, PS11=0 and D1=1, S1/P1 is outputted at the high level. When "PS10, PS11" are not "0, 0", D1 is invalid.       |

| D2           | S2/P2                 | When PS20=0, PS21=0 and D2=0, S2/P2 is outputted at the low level. When PS20=0, PS21=0 and D2=1, S2/P2 is outputted at the high level. When "PS20, PS21" are not "0, 0", D2 is invalid.       |

| D3           | S3/P3                 | When PS30=0, PS31=0 and D3=0, S3/P3 is outputted at the low level.<br>When PS30=0, PS31=0 and D3=1, S3/P3 is outputted at the high level.<br>When "PS30, PS31" are not "0, 0", D3 is invalid. |

| D4           | S4/P4                 | When PS40=0, PS41=0 and D4=0, S4/P4 is outputted at the low level. When PS40=0, PS41=0 and D4=1, S4/P4 is outputted at the high level. When "PS40, PS41" are not "0, 0", D4 is invalid.       |

When control the LED in the system configuration example of the Figure 8, a register setting example is shown below.

### (Case 1) When all LED were set to OFF.

|      | purpose ou<br>(P1) contro |    |      | purpose ou<br>(P2) contro |    |      | purpose ou<br>(P3) contro |    | General-purpose output port (P4) control |      |    |  |

|------|---------------------------|----|------|---------------------------|----|------|---------------------------|----|------------------------------------------|------|----|--|

|      | OFF                       |    |      | OFF                       |    |      | OFF                       |    |                                          | OFF  |    |  |

| PS10 | PS11                      | D1 | PS20 | PS21                      | D2 | PS30 | PS31                      | D3 | PS40                                     | PS41 | D4 |  |

| 0    | 0                         | 0  | 0    | 0                         | 0  | 0    | 0                         | 0  | 0                                        | 0    | 0  |  |

### (Case 2) When backlight-LED was set to ON (Brightness is 50%).

|   | General- | purpose ou  | utput port | General- | purpose ou  | tput port | General- | purpose ou  | utput port | General- | purpose ou  | tput port  |

|---|----------|-------------|------------|----------|-------------|-----------|----------|-------------|------------|----------|-------------|------------|

|   | (        | (P1) contro | I          |          | (P2) contro | l         | (        | (P3) contro | l          | (        | (P4) contro | l          |

|   |          | OFF         |            |          | OFF         |           |          | OFF         |            |          | to W35=1,   | 1,1,1,1,0) |

|   | PS10     | PS11        | D1         | PS20     | PS21        | D2        | PS30     | PS31        | D3         | PS40     | PS41        | D4         |

| Ī | 0        | 0           | 0          | 0        | 0           | 0         | 0        | 0           | 0          | 1        | 1           | 0          |

### (Case 3) When backlight-LED was set to ON (Brightness is 50%) and button indicator A-LED was set to ON (Brightness is 50%).

|   | General-                   | purpose ou  | tput port | General- | purpose ou  | tput port | General- | purpose ou  | utput port | General-                    | purpose ou | tput port |  |

|---|----------------------------|-------------|-----------|----------|-------------|-----------|----------|-------------|------------|-----------------------------|------------|-----------|--|

|   |                            | (P1) contro | l         | (        | (P2) contro | l i       | (        | (P3) contro | I          | (P4) control                |            |           |  |

| Ī | ON (W10 to W15=1,1,1,1,1,0 |             |           | OFF      |             |           |          | OFF         |            | ON (W30 to W35=1,1,1,1,1,0) |            |           |  |

|   | PS10                       | PS11        | D1        | PS20     | PS21        | D2        | PS30     | PS31        | D3         | PS40                        | PS41       | D4        |  |

|   | 1                          | 1           | 0         | 0        | 0           | 0         | 0        | 0           | 0          | 1                           | 1          | 0         |  |

### (Case 4) When backlight-LED was set to ON (Brightness is 50%) and button indicator B-LED was set to ON (Brightness is 50%).

| General- | purpose ou                      | utput port | General- | purpose ou | utput port | General- | purpose ou  | tput port | General- | purpose ou  | tput port |

|----------|---------------------------------|------------|----------|------------|------------|----------|-------------|-----------|----------|-------------|-----------|

| 1        | (P1) control (P2) control       |            |          |            |            |          | (P3) contro | I         | (        | (P4) contro | ı         |

|          | OFF ON (W10 to W15=1,1,1,1,1,0) |            |          |            |            | OFF      |             | ON (W30   | to W35=1 | 1,1,1,1,0)  |           |

| PS10     | PS11                            | D1         | PS20     | PS21       | D2         | PS30     | PS31        | D3        | PS40     | PS41        | D4        |

| 0        | 0                               | 0          | 1        | 0          | 0          | 0        | 0           | 0         | 1        | 1           | 0         |

### (Case 5) When backlight-LED was set to ON (Brightness is 50%) and button indicator A/B/C-LED were set to ON (Brightness is 50%).

| •                                             | _           |           | ,        | •           | •         |           |             |            |           | , .         |           |

|-----------------------------------------------|-------------|-----------|----------|-------------|-----------|-----------|-------------|------------|-----------|-------------|-----------|

| General-                                      | purpose ou  | tput port | General- | purpose ou  | tput port | General-  | purpose ou  | utput port | General-  | purpose ou  | tput port |

|                                               | (P1) contro | I         |          | (P2) contro | I         |           | (P3) contro | I          | (         | (P4) contro | l i       |

| ON (W10 to W15=1,1,1,1,1,0) ON (W10 to W15=1, |             |           |          | 1,1,1,1,0)  | ON (W20   | to W25=1, | ,1,1,1,1,0) | ON (W30    | to W35=1, | 1,1,1,1,0)  |           |

| PS10                                          | PS11        | D1        | PS20     | PS21        | D2        | PS30      | PS31        | D3         | PS40      | PS41        | D4        |

| 1                                             | 1           | 0         | 1        | 0           | 0         | 0         | 1           | 0          | 1         | 1           | 0         |

### (Case 6) When button indicator C-LED was changed from 50% to 79.69%.

| Gene  | ral-purpose               | output port                                  | General- | purpose ou | utput port                  | General-     | purpose ou | utput port | General-     | purpose ou  | tput port |

|-------|---------------------------|----------------------------------------------|----------|------------|-----------------------------|--------------|------------|------------|--------------|-------------|-----------|

|       | (P1) control (P2) control |                                              |          |            |                             | (P3) control |            |            | (P4) control |             |           |

| ON (V | V10 to W15=               | W15=1,1,1,1,1,0) ON (W10 to W15=1,1,1,1,1,0) |          |            | ON (W20 to W25=0,1,0,0,1,1) |              |            | ON (W30    | to W35=1     | ,1,1,1,1,0) |           |

| PS1   | 0 PS11                    | D1                                           | PS20     | PS21       | D2                          | PS30         | PS31       | D3         | PS40         | PS41        | D4        |

| 1     | 1                         | 0                                            | 1        | 0          | 0                           | 0            | 1          | 0          | 1            | 1           | 0         |

### (Case 7) When backlight-LED was set to OFF.

| Gener | al-purpose o | utput port  | General- | purpose ou  | utput port | General-                    | purpose ou  | utput port | General-     | purpose ou | utput port |

|-------|--------------|-------------|----------|-------------|------------|-----------------------------|-------------|------------|--------------|------------|------------|

|       | (P1) contro  | ol          |          | (P2) contro | I          |                             | (P3) contro | l i        | (P4) control |            |            |

| ON (W | 0 to W15=1   | ,1,1,1,1,0) | ON (W10  | to W15=1,   | 1,1,1,1,0) | ON (W20 to W25=0,1,0,0,1,1) |             |            |              | OFF        |            |

| PS10  | PS11         | D1          | PS20     | PS21        | D2         | PS30                        | PS31        | D3         | PS40         | PS41       | D4         |

| 1     | 1            | 0           | 1        | 0           | 0          | 0                           | 1           | 0          | 0            | 0          | 0          |

(Case 8) When all LED were set to ON (Brightness is 100%).

| Gen   | eral- | purpose ou | tput port  | General-     | purpose ou | utput port | General-                    | purpose ou  | tput port | General- | purpose ou  | tput port  |

|-------|-------|------------|------------|--------------|------------|------------|-----------------------------|-------------|-----------|----------|-------------|------------|

|       | (     | P1) contro | l i        | (P2) control |            |            |                             | (P3) contro | l i       | (        | (P4) contro | l i        |

| ON (\ | W10   | to W15=1,  | 1,1,1,1,1) | ON (W10      | to W15=1,  | 1,1,1,1,1) | ON (W20 to W25=1,1,1,1,1,1) |             |           | ON (W30  | to W35=1    | 1,1,1,1,1) |

| PS1   | 10    | PS11       | D1         | PS20         | PS21       | D2         | PS30                        | PS31        | D3        | PS40     | PS41        | D4         |

| 1     |       | 1          | 0          | 1            | 0          | 0          | 0                           | 1           | 0         | 1        | 1           | 0          |

or

| ( | General- | purpose ou  | tput port | General- | purpose ou  | utput port | General- | purpose ou  | utput port | General- | purpose ou  | utput port |

|---|----------|-------------|-----------|----------|-------------|------------|----------|-------------|------------|----------|-------------|------------|

|   | (        | (P1) contro |           |          | (P2) contro | l          |          | (P3) contro |            | (        | (P4) contro |            |

|   | ON ON    |             |           |          | ON          |            | ON       |             |            |          | ON          |            |

|   | PS10     | PS11        | D1        | PS20     | PS21        | D2         | PS30     | PS31        | D3         | PS40     | PS41        | D4         |

|   | 0        | 0           | 1         | 0        | 0           | 1          | 0        | 0           | 1          | 0        | 0           | 1          |

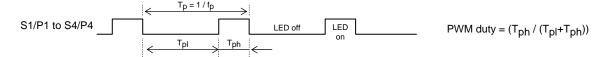

# (4) PWM Duty Setting (W10 to W15, W20 to W25, W30 to W35)

The registers from W10 to W15, from W20 to W25, and from W30 to W35 can set the pulse width of the PWM output. The PWM duty setting has up to 3ch and can perform brightness adjustment of the LED individually for each channel. However, the PWM duty setting register (W10 to W15, W20 to W25, and W30 to W35) does not have a setting function of the 0%-duty. Therefore when you want to turn off the LED, the "Display data setting registers (D1 to D4)" by general-purpose output function set the "0", and general-purpose output ports (P1 to P4) output low level.

| Wx0   | Wx1 | Wx2  | Wx3   | Wx4 | Wx5  | PWM output pulse width |

|-------|-----|------|-------|-----|------|------------------------|

| 117.0 | *** | **** | 117.0 | *** | **** | (PWM duty)             |

| 0     | 0   | 0    | 0     | 0   | 0    | 1/64 (1.56%)           |

| 1     | 0   | 0    | 0     | 0   | 0    | 2/64 (3.12%)           |

| 0     | 1   | 0    | 0     | 0   | 0    | 3/64 (4.69%)           |

| 1     | 1   | 0    | 0     | 0   | 0    | 4/64 (6.25%)           |

| 0     | 0   | 1    | 0     | 0   | 0    | 5/64 (7.81%)           |

| 1     | 0   | 1    | 0     | 0   | 0    | 6/64 (9.38%)           |

| 0     | 1   | 1    | 0     | 0   | 0    | 7/64 (10.94%)          |

| 1     | 1   | 1    | 0     | 0   | 0    | 8/64 (12.50%)          |

| 0     | 0   | 0    | 1     | 0   | 0    | 9/64 (14.06%)          |

| 1     | 0   | 0    | 1     | 0   | 0    | 10/64 (15.62%)         |

| 0     | 1   | 0    | 1     | 0   | 0    | 11/64 (17.19%)         |

| 1     | 1   | 0    | 1     | 0   | 0    | 12/64 (18.75%)         |

| 0     | 0   | 1    | 1     | 0   | 0    | 13/64 (20.31%)         |

| 1     | 0   | 1    | 1     | 0   | 0    | 14/64 (21.87%)         |

| 0     | 1   | 1    | 1     | 0   | 0    | 15/64 (23.44%)         |

| 1     | 1   | 1    | 1     | 0   | 0    | 16/64 (25.00%)         |

| 0     | 0   | 0    | 0     | 1   | 0    | 17/64 (26.56%)         |

| 1     | 0   | 0    | 0     | 1   | 0    | 18/64 (28.12%)         |

| 0     | 1   | 0    | 0     | 1   | 0    | 19/64 (29.69%)         |

| 1     | 1   | 0    | 0     | 1   | 0    | 20/64 (31.25%)         |

| 0     | 0   | 1    | 0     | 1   | 0    | 21/64 (32.81%)         |

| 1     | 0   | 1    | 0     | 1   | 0    | 22/64 (34.37%)         |

| 0     | 1   | 1    | 0     | 1   | 0    | 23/64 (35.94%)         |

| 1     | 1   | 1    | 0     | 1   | 0    | 24/64 (37.50%)         |

| 0     | 0   | 0    | 1     | 1   | 0    | 25/64 (39.06%)         |

| 1     | 0   | 0    | 1     | 1   | 0    | 26/64 (40.62%)         |

| 0     | 1   | 0    | 1     | 1   | 0    | 27/64 (42.19%)         |

| 1     | 1   | 0    | 1     | 1   | 0    | 28/64 (43.75%)         |

| 0     | 0   | 1    | 1     | 1   | 0    | 29/64 (45.31%)         |

| 1     | 0   | 1    | 1     | 1   | 0    | 30/64 (46.87%)         |

| 0     | 1   | 1    | 1     | 1   | 0    | 31/64 (48.44%)         |

| 1     | 1   | 1    | 1     | 1   | 0    | 32/64 (50.00%)         |

| Wx0 | Wx1 | Wx2 | Wx3 | Wx4 | Wx5 | PWM output pulse width (PWM duty) |

|-----|-----|-----|-----|-----|-----|-----------------------------------|

| 0   | 0   | 0   | 0   | 0   | 1   | 33/64 (51.56%)                    |

| 1   | 0   | 0   | 0   | 0   | 1   | 34/64 (53.12%)                    |

| 0   | 1   | 0   | 0   | 0   | 1   | 35/64 (54.69%)                    |

| 1   | 1   | 0   | 0   | 0   | 1   | 36/64 (56.25%)                    |

| 0   | 0   | 1   | 0   | 0   | 1   | 37/64 (57.81%)                    |

| 1   | 0   | 1   | 0   | 0   | 1   | 38/64 (59.37%)                    |

| 0   | 1   | 1   | 0   | 0   | 1   | 39/64 (60.94%)                    |

| 1   | 1   | 1   | 0   | 0   | 1   | 40/64 (62.50%)                    |

| 0   | 0   | 0   | 1   | 0   | 1   | 41/64 (64.06%)                    |

| 1   | 0   | 0   | 1   | 0   | 1   | 42/64 (65.62%)                    |

| 0   | 1   | 0   | 1   | 0   | 1   | 43/64 (67.19%)                    |

| 1   | 1   | 0   | 1   | 0   | 1   | 44/64 (68.75%)                    |

| 0   | 0   | 1   | 1   | 0   | 1   | 45/64 (70.31%)                    |

| 1   | 0   | 1   | 1   | 0   | 1   | 46/64 (71.87%)                    |

| 0   | 1   | 1   | 1   | 0   | 1   | 47/64 (73.44%)                    |

| 1   | 1   | 1   | 1   | 0   | 1   | 48/64 (75.00%)                    |

| 0   | 0   | 0   | 0   | 1   | 1   | 49/64 (76.56%)                    |

| 1   | 0   | 0   | 0   | 1   | 1   | 50/64 (78.12%)                    |

| 0   | 1   | 0   | 0   | 1   | 1   | 51/64 (79.69%)                    |

| 1   | 1   | 0   | 0   | 1   | 1   | 52/64 (81.25%)                    |

| 0   | 0   | 1   | 0   | 1   | 1   | 53/64 (82.81%)                    |

| 1   | 0   | 1   | 0   | 1   | 1   | 54/64 (84.37%)                    |

| 0   | 1   | 1   | 0   | 1   | 1   | 55/64 (85.94%)                    |

| 1   | 1   | 1   | 0   | 1   | 1   | 56/64 (87.50%)                    |

| 0   | 0   | 0   | 1   | 1   | 1   | 57/64 (89.06%)                    |

| 1   | 0   | 0   | 1   | 1   | 1   | 58/64 (90.62%)                    |

| 0   | 1   | 0   | 1   | 1   | 1   | 59/64 (92.19%)                    |

| 1   | 1   | 0   | 1   | 1   | 1   | 60/64 (93.75%)                    |

| 0   | 0   | 1   | 1   | 1   | 1   | 61/64 (95.31%)                    |

| 1   | 0   | 1   | 1   | 1   | 1   | 62/64 (96.87%)                    |

| 0   | 1   | 1   | 1   | 1   | 1   | 63/64 (98.44%)                    |

| 1   | 1   | 1   | 1   | 1   | 1   | 64/64 (100.00%)                   |

x:1 to 3

# **Explanation of the Instruction Data**

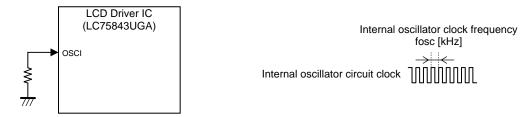

(1) Fundamental Clock Operating Mode Setting (OC, EXF)

Figure 10. Peripheral circuits configuration example of the external clock input pin

The OC register can set the "Internal oscillator operating mode" or "External clock input operating mode". Furthermore, when OC register sets the "External clock input operating mode (OC=1)", the EXF register can set the division ratio. The EXF register can set the division ratio a clock to input from OSCI pin becomes 300 [kHz](Typ.) and 38 [kHz](Typ.). However, when set the "External clock 38kHz input mode (OC=1 and EXF=1)", please be careful because PWM output function is invalidity. The LCD system configuration example sets OC=0 and EXF=0 to use the "Internal oscillator operating mode".

| OC | EXF | Fundamental clock operating mode   | OSCI input pin state              |

|----|-----|------------------------------------|-----------------------------------|

| 0  | 0/1 | Internal oscillator operating mode | Connect to GND                    |

| 1  | 0   | External clock 300kHz input mode   | Inputs a clock of 300 [kHz](Typ.) |

| 1  | 1   | External clock 38kHz input mode    | Inputs a clock of 38 [kHz](Typ.)  |

The explanation mentioned above is used only to explain internal operation and how to IC, and the characteristic of the products is uneven by a production variation and the terms of use of the IC (Power supply voltage, temperature, etc.). Therefore, the customer should always evaluate and test devices mounted in the customer's products or equipment.

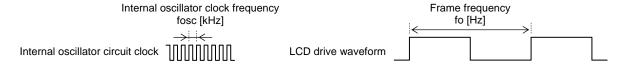

### (2) LCD Drive Waveform Frame Frequency Setting (FC0 to FC3)

The registers from FC0 to FC3 can set the frame frequency (fo) of the common and segment output waveform. The frame frequency (frame ratio) setting of the LCD drive waveform is different by "Fundamental clock operating mode setting register (OC)" and "External clock operating frequency setting register (EXF)".

The LCD system configuration example sets OC=0 to use the "Internal oscillator operating mode". When sets OC=0, the following table shows the frame frequency of the LCD drive waveform.

|         |     |        |                                | Internal oscillator operating mode (OC=0)                                                                         |        |  |

|---------|-----|--------|--------------------------------|-------------------------------------------------------------------------------------------------------------------|--------|--|

| FC0 FC1 | FC2 | C2 FC3 | LCD drive waveform frame ratio | LCD drive waveform frame frequency<br>fo [Hz]<br>(Internal oscillator clock frequency is<br>fosc=300 [kHz](typ.)) |        |  |

| 0       | 0   | 0      | 0                              | fosc / 6144                                                                                                       | 48.83  |  |

| 0       | 0   | 0      | 1                              | fosc / 5376                                                                                                       | 55.80  |  |

| 0       | 0   | 1      | 0                              | fosc / 4608                                                                                                       | 65.10  |  |

| 0       | 0   | 1      | 1                              | fosc / 3840                                                                                                       | 78.12  |  |

| 0       | 1   | 0      | 0                              | fosc / 3456                                                                                                       | 86.80  |  |

| 0       | 1   | 0      | 1                              | fosc / 3072                                                                                                       | 97.66  |  |

| 0       | 1   | 1      | 0                              | fosc / 2688                                                                                                       | 111.61 |  |

| 0       | 1   | 1      | 1                              | fosc / 2304                                                                                                       | 130.21 |  |

| 1       | 0   | 0      | 0                              | fosc / 2112                                                                                                       | 142.04 |  |

| 1       | 0   | 0      | 1                              | fosc / 1920                                                                                                       | 156.25 |  |

| 1       | 0   | 1      | 0                              | fosc / 1728                                                                                                       | 173.61 |  |

| 1       | 0   | 1      | 1                              | fosc / 1536                                                                                                       | 195.31 |  |

| 1       | 1   | 0      | 0                              | fosc / 1344                                                                                                       | 223.21 |  |

| 1       | 1   | 0      | 1                              | fosc / 1152                                                                                                       | 260.42 |  |

| 1       | 1   | 1      | 0                              | fosc / 960                                                                                                        | 312.50 |  |

| 1       | 1   | 1      | 1                              | fosc / 768                                                                                                        | 390.62 |  |

The explanation mentioned above is used only to explain internal operation and how to IC, and the characteristic of the products is uneven by a production variation and the terms of use of the IC (Power supply voltage, temperature, etc.). Therefore, the customer should always evaluate and test devices mounted in the customer's products or equipment.

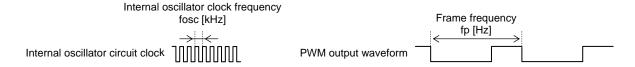

### (3) PWM Output Waveform Frame Frequency Setting (PF0 to PF3)

The registers from PF0 to PF3 can set the PWM output frame frequency (fp) of the general-purpose output port. When set the "External clock input operating mode setting (OC = 1)" and "External clock 38kHz input mode setting (EXF=1)", these registers are invalid.

The LCD system configuration example is "Internal oscillator operating mode" operated. Therefore, this system sets OC=0. When sets OC=0, the following table shows the frame frequency (fp) of the PWM output waveform.

|         |     |     | Internal oscillato              | or operating mode (OC=0)                                                                                           |         |

|---------|-----|-----|---------------------------------|--------------------------------------------------------------------------------------------------------------------|---------|

| PF0 PF1 | PF2 | PF3 | PWM output waveform frame ratio | PWM output waveform frame frequency<br>fp [Hz]<br>(Internal oscillator clock frequency is<br>fosc=300 [kHz](typ.)) |         |

| 0       | 0   | 0   | 0                               | fosc / 1536                                                                                                        | 195.31  |

| 1       | 0   | 0   | 0                               | fosc / 1408                                                                                                        | 213.07  |

| 0       | 1   | 0   | 0                               | fosc / 1280                                                                                                        | 234.37  |

| 1       | 1   | 0   | 0                               | fosc / 1152                                                                                                        | 260.42  |

| 0       | 0   | 1   | 0                               | fosc / 1024                                                                                                        | 292.97  |

| 1       | 0   | 1   | 0                               | fosc / 896                                                                                                         | 334.82  |

| 0       | 1   | 1   | 0                               | fosc / 768                                                                                                         | 390.62  |

| 1       | 1   | 1   | 0                               | fosc / 640                                                                                                         | 468.75  |

| 0       | 0   | 0   | 1                               | fosc / 512                                                                                                         | 585.94  |

| 1       | 0   | 0   | 1                               | fosc / 384                                                                                                         | 781.25  |

| 0       | 1   | 0   | 1                               | fosc / 256                                                                                                         | 1171.87 |

| 1       | 1   | 0   | 1                               | fosc / 896                                                                                                         | 334.82  |

| 0       | 0   | 1   | 1                               | fosc / 896                                                                                                         | 334.82  |

| 1       | 0   | 1   | 1                               | fosc / 896                                                                                                         | 334.82  |

| 0       | 1   | 1   | 1                               | fosc / 896                                                                                                         | 334.82  |

| 1       | 1   | 1   | 1                               | fosc / 896                                                                                                         | 334.82  |

The explanation mentioned above is used only to explain internal operation and how to IC, and the characteristic of the products is uneven by a production variation and the terms of use of the IC (Power supply voltage, temperature, etc.). Therefore, the customer should always evaluate and test devices mounted in the customer's products or equipment.

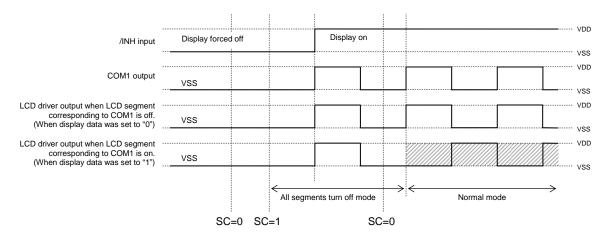

# (4) All Segments Turn Off Mode Setting (SC)

The SC register can set the "Normal mode" or "All segments turn off mode". The LC75843UGA can display forced turn off by the /INH pin. When sets /INH pin=Low (VSS), segment outputs (S5 to S28), common output (COM1) and general-purpose port outputs (S1/P1 to S4/P4) are outputted at the all VSS level. In addition, it can display OFF (turn off the segments) by controllable SC register from the software of the LCD controller. When sets SC=1, segment outputs (S5 to S28) are outputted at the all off waveform.

| /INH       | SC       | Output pin state                     |                         |                                                |  |  |

|------------|----------|--------------------------------------|-------------------------|------------------------------------------------|--|--|

| pin        | register | Segment outputs<br>(S5 to S28)       | Common output<br>(COM1) | General-purpose port outputs (S1/P1 to S4/P4)  |  |  |

| Low (VSS)  | 0/1      | All segment outputs are VSS level    | VSS level               | All general-purpose port outputs are VSS level |  |  |

| High (VDD) | 0        | Segments can output ON waveform      | Scan drive waveform     | General-purpose outputs or PWM waveform        |  |  |

|            | 1        | All segment outputs are OFF waveform | Scan drive waveform     | General-purpose outputs or PWM waveform        |  |  |

The LCD system configuration example is LCD panel of the static (1/1-duty) drive used. Therefore, when set "Static (1/1-duty) drive mode (DT0=1 and DT1=1)", the following figure shows the LCD drive waveform.

Figure 11. LCD driver output waveform when SC is set

# (5) Power Saving Mode Setting (BU)

The BU register can set the "Normal mode" or "Power saving mode". The LC75843UGA built-in the "Power saving mode" as a low power consumption mode. When set the "Power saving mode", the internal oscillator circuit is stopped, and external clock input is inhibited and common / segment output pins are outputted at the VSS level. However, the output pins from S1/P1 to S4/P4 can output of high level or low level as a general-purpose output function by "Display data setting registers (D1 to D4)". (PWM output function is invalid)

| BU | Low power consumption mode | Internal operating conditions                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|----|----------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0  | Normal mode                | Normal mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 1  | Power saving mode          | <ul> <li>When output pins from S1/P1 to S4/P4 set the general-purpose output port, the output pins from S1/P1 to S4/P4 can use only a general-purpose output function of high level or low level.</li> <li>Segment output pins (S5 to S28) are VSS level.</li> <li>Common output pin (COM1) is VSS level.</li> <li>The internal oscillator circuit is stopped.</li> <li>External clock input is inhibited.</li> <li>The reception of serial control data is possible. (Registers are updated)</li> </ul> |

# Software Control Example of the LCD Controller

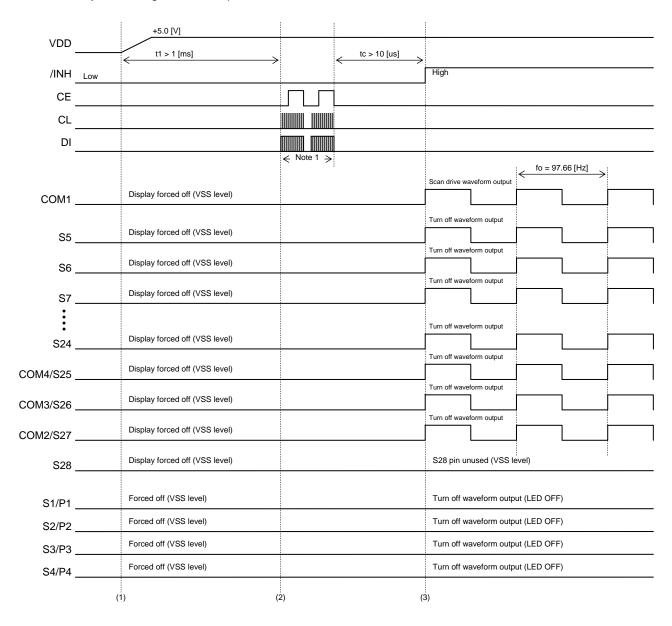

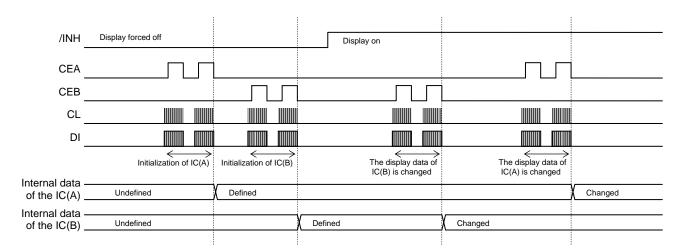

(1) Timing Chart From Power-on State to LCD Display ON

First, the following figure shows the timing waveform from power-on state to initial setting and LCD display ON in the LCD system configuration example.

### < Operation sequence >

- (1) Power-on.

- (2) The initial setting command is transferred after passage of "Serial data input wait time (t1 > 1 [ms])".

- (3) The display forced off is cancelled by setting the /INH pin to High(VDD) after passage of "Command execute wait time (tc > 10 [us])".

### < Transfer instruction data >

```

Note 1: CCB address = (44)h, D1 to D4= all "0" data, D5 to D28= all "0" data, D70=1 and D71=1 (Static (1/1-duty) drive), W10 to W15=1,1,1,1,1,0 (Brightness is 50%), W20 to W25=1,1,1,1,1,1,0 (Brightness is 50%), W30 to W35=1,1,1,1,1,1 (Brightness is 100%), PF0=0, PF1=1, PF2=0 and PF3=0 (fp=234.37 [Hz]), PS10=0 and PS11=0 (S1/P1=Low level general-purpose output), PS20=0 and PS21=0 (S2/P2=Low level general-purpose output), PS30=0 and PS31=0 (S3/P3=Low level general-purpose output), PS40=0 and PS41=0 (S4/P4=Low level general-purpose output), P0=1, P1=0 and P2=0 (S1/P1 to S4/P4 are set by general-purpose output port (P1 to P4)), FC0=0, FC1=1, FC2=0 and FC3=1 (fo=97.66 [Hz]), DN=0 (S28 pin unused), EXF=0 and OC=0 (Internal oscillator operating mode),

```

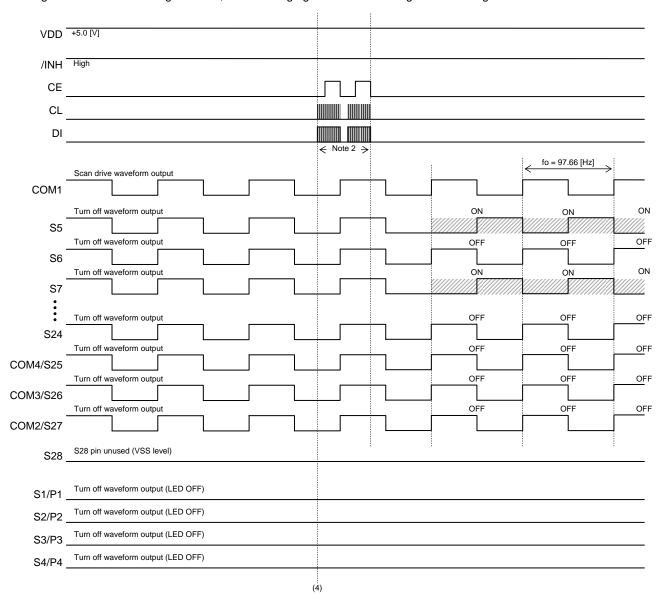

### (2) Timing Chart of the LCD Display Contents Change

Next, the following figure shows the timing waveform of the LCD display contents change. For example, when S5 segment is ON and S7 segment ON, the following figures shows the segment to change.

### < Operation sequence >

(4) The command of the LCD display change is transferred.

# < Transfer instruction data >

```

Note 2 : CCB address = (44)h, D1 to D4=all "0" data, D5=1, D6=0, D7=1. D8 to D28=all "0" data, DT0=1 and DT1=1 (Static (1/1-duty) drive), W10 to W15=1,1,1,1,1,0 (Brightness is 50%), W20 to W25=1,1,1,1,1,0 (Brightness is 50%), W30 to W35=1,1,1,1,1,1 (Brightness is 100%), PF0=0, PF1=1, PF2=0 and PF3=0 (fp=234.37 [Hz]), PS10=0 and PS11=0 (S1/P1=Low level general-purpose output), PS20=0 and PS31=0 (S2/P2=Low level general-purpose output), PS30=0 and PS31=0 (S3/P3=Low level general-purpose output), PS40=0 and PS41=0 (S4/P4=Low level general-purpose output), P0=1, P1=0 and P2=0 (S1/P1 to S4/P4 are set by general-purpose output port (P1 to P4)), FC0=0, FC1=1, FC2=0 and FC3=1 (f0=97.66 [Hz]), DN=0 (S28 pin unused), EXF=0 and OC=0 (Internal oscillator operating mode), SC=0 ("All segment turn off mode" was cancelled), BU=0 ("Power saving mode" was cancelled).

```

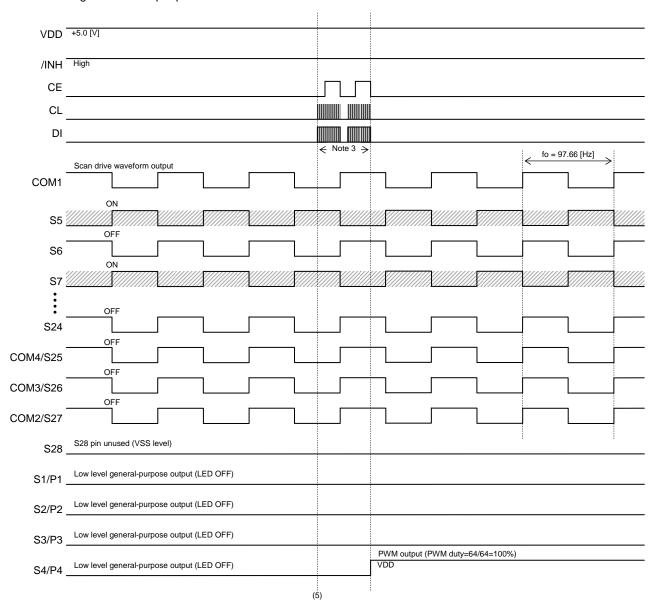

### (3) Timing Chart of the Setting to Turn on the LED of Backlight

Next, the following figure shows the timing waveform of turn on the LED of backlight (Brightness is 100%) connecting to S4/P4 output pin.

### < Operation sequence >

(5) The command of the LED control is transferred.

### < Transfer instruction data >

```

Note 3: CCB address = (44)h, D1 to D4=all "0" data, D5=1, D6=0, D7=1, D8 to D28=all "0" data,

DT0=1 and DT1=1 (Static (1/1-duty) drive),

W10 to W15=1,1,1,1,1,0 (Brightness is 50%),

W20 to W25=1,1,1,1,1,0 (Brightness is 50%),

W30 to W35=1,1,1,1,1,1 (Brightness is 100%),

PF0=0, PF1=1, PF2=0 and PF3=0 (fp=234.37 [Hz]),

PS10=0 and PS11=0 (S1/P1=Low level general-purpose output),

PS20=0 and PS21=0 (S2/P2=Low level general-purpose output),

PS30=0 and PS31=0 (S3/P3=Low level general-purpose output),

PS40=1 and PS41=1 (S4/P4=PWM output function (ch3) setting).

P0=1, P1=0 and P2=0 (S1/P1 to S4/P4 are set by general-purpose output port (P1 to P4)),

FC0=0, FC1=1, FC2=0 and FC3=1 (fo=97.66 [Hz]),

DN=0 (S28 pin unused), EXF=0 and OC=0 (Internal oscillator operating mode),

SC=0 ("All segment turn off mode" was cancelled), BU=0 ("Power saving mode" was cancelled).

```

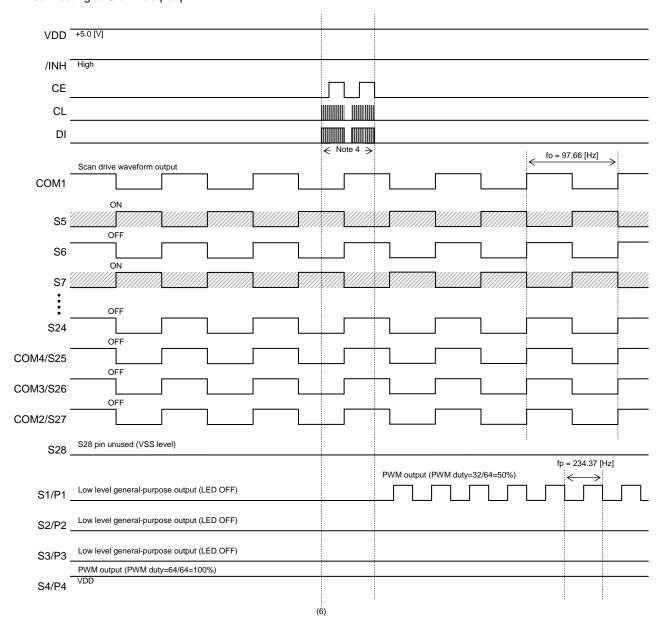

### (4) Timing Chart of the Setting to Turn on the LED of Button Indicator A

Next, the following figure shows the timing waveform of turn on the LED of button indicator A (Brightness is 50%) connecting to S1/P1 output pin.

### < Operation sequence >

(6) The command of the LED control is transferred.

### < Transfer instruction data >

Note 4 : CCB address = (44)h, D1 to D4=all "0" data, D5=1, D6=0, D7=1, D8 to D28=all "0" data, DT0=1 and DT1=1 (Static (1/1-duty) drive),

W10 to W15=1,1,1,1,1,0 (Brightness is 50%),

W20 to W25=1,1,1,1,1,0 (Brightness is 50%),

W30 to W35=1,1,1,1,1,1 (Brightness is 100%),

PF0=0, PF1=1, PF2=0 and PF3=0 (fp=234.37 [Hz]),

PS10=1 and PS11=1 (S1/P1=PWM output function (ch1) setting).

PS20=0 and PS21=0 (S2/P2=Low level general-purpose output),

PS30=0 and PS31=0 (S3/P3=Low level general-purpose output),

PS40=1 and PS41=1 (S4/P4=PWM output function (ch3) setting),

P0=1, P1=0 and P2=0 (S1/P1 to S4/P4 are set by general-purpose output port (P1 to P4)),

FC0=0, FC1=1, FC2=0 and FC3=1 (fo=97.66 [Hz]),

DN=0 (S28 pin unused), EXF=0 and OC=0 (Internal oscillator operating mode),

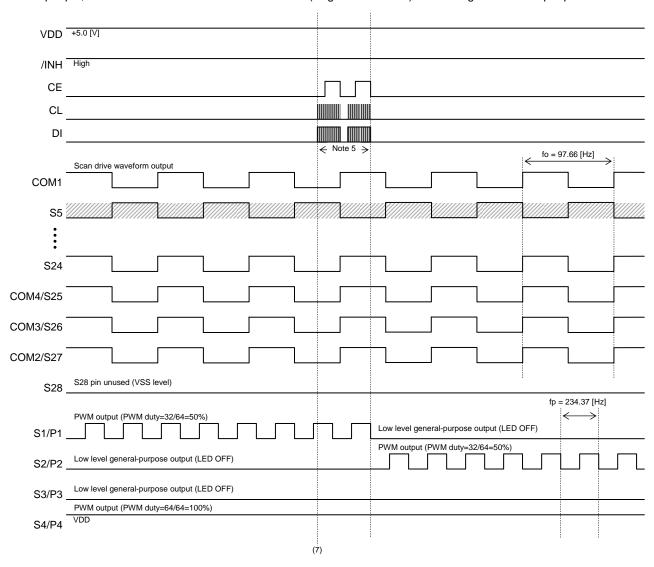

### (5) Timing Chart of the Setting to Turn on the LED of Button Indicator B

Next, the following figure shows the timing waveform of turn off the LED of button indicator A connecting to S1/P1 output pin, and turn on the LED of button indicator B (Brightness is 50%) connecting to S2/P2 output pin.

### < Operation sequence >

(7) The command of the LED control is transferred.

# < Transfer instruction data >

Note 5: CCB address = (44)h, D1 to D4=all "0" data, D5=1, D6=0, D7=1, D8 to D28=all "0" data, DT0=1 and DT1=1 (Static (1/1-duty) drive),

W10 to W15=1,1,1,1,1,0 (Brightness is 50%),

W20 to W25=1,1,1,1,1,0 (Brightness is 50%),

W30 to W35=1,1,1,1,1,1 (Brightness is 100%),

PF0=0, PF1=1, PF2=0 and PF3=0 (fp=234.37 [Hz]),

### PS10=0 and PS11=0 (S1/P1=Low level general-purpose output), PS20=1 and PS21=0 (S2/P2=PWM output function (ch1) setting),

PS30=0 and PS31=0 (S3/P3=Low level general-purpose output),

PS40=1 and PS41=1 (S4/P4=PWM output function (ch3) setting),

P0=1, P1=0 and P2=0 (S1/P1 to S4/P4 are set by general-purpose output port (P1 to P4)),

FC0=0, FC1=1, FC2=0 and FC3=1 (fo=97.66 [Hz]),

DN=0 (S28 pin unused), EXF=0 and OC=0 (Internal oscillator operating mode),

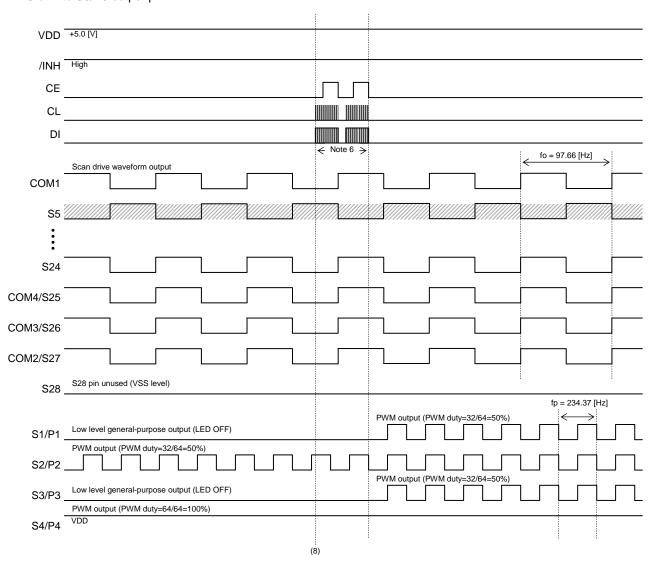

### (6) Timing Chart of the Setting to Turn on the LED of Button Indicator A to C

Next, the following figure shows the timing waveform of turn on the LED of button indicator A to C connecting to S1/P1 to S3/P3 output pin.

### < Operation sequence >

(8) The command of the LED control is transferred.

# < Transfer instruction data >

Note 6 : CCB address = (44)h, D1 to D4=all "0" data, D5=1, D6=0, D7=1, D8 to D28=all "0" data,

DT0=1 and DT1=1 (Static (1/1-duty) drive),

W10 to W15=1,1,1,1,1,0 (Brightness is 50%),

W20 to W25=1,1,1,1,1,0 (Brightness is 50%),

W30 to W35=1,1,1,1,1,1 (Brightness is 100%),

PF0=0, PF1=1, PF2=0 and PF3=0 (fp=234.37 [Hz]),

PS10=1 and PS11=1 (S1/P1=PWM output function (ch1) setting),

PS20=1 and PS21=0 (S2/P2=PWM output function (ch1) setting), PS30=0 and PS31=1 (S3/P3=PWM output function (ch2) setting),

PS40=1 and PS41=1 (S4/P4=PWM output function (ch2) setting

P0=1, P1=0 and P2=0 (S1/P1 to S4/P4 are set by general-purpose output port (P1 to P4)),

FC0=0, FC1=1, FC2=0 and FC3=1 (fo=97.66 [Hz]),

DN=0 (S28 pin unused), EXF=0 and OC=0 (Internal oscillator operating mode),

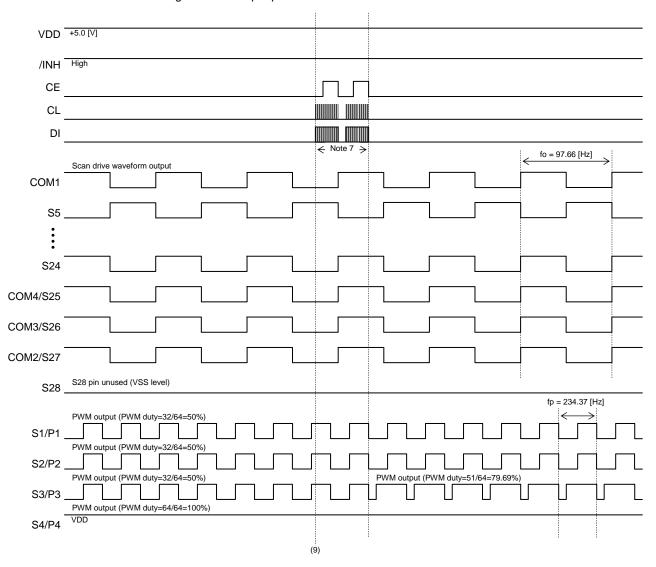

### (7) Timing Chart of the Setting to Change the Brightness of the LED

Next, the following figure shows the timing waveform of the LED brightness change (Brightness is 79.69%) of button indicator C connecting to S3/P3 output pin.

### < Operation sequence >

(9) The command of the LED control is transferred.

# < Transfer instruction data >

Note 7 : CCB address = (44)h, D1 to D4=all "0" data, D5=1, D6=0, D7=1, D8 to D28=all "0" data, DT0=1 and DT1=1 (Static (1/1-duty) drive), W10 to W15=1,1,1,1,1,0 (Brightness is 50%),

# W20 to W25=0,1,0,0,1,1 (Brightness is 79.69%),

W30 to W35=1,1,1,1,1,1 (Brightness is 100%),

PF0=0, PF1=1, PF2=0 and PF3=0 (fp=234.37 [Hz]),

PS10=1 and PS11=1 (S1/P1=PWM output function (ch1) setting),

PS20=1 and PS21=0 (S2/P2=PWM output function (ch1) setting),

PS30=0 and PS31=1 (S3/P3=PWM output function (ch2) setting),

PS40=1 and PS41=1 (S4/P4=PWM output function (ch3) setting),

P0=1, P1=0 and P2=0 (S1/P1 to S4/P4 are set by general-purpose output port (P1 to P4)),

FC0=0, FC1=1, FC2=0 and FC3=1 (fo=97.66 [Hz]),

DN=0 (S28 pin unused), EXF=0 and OC=0 (Internal oscillator operating mode),

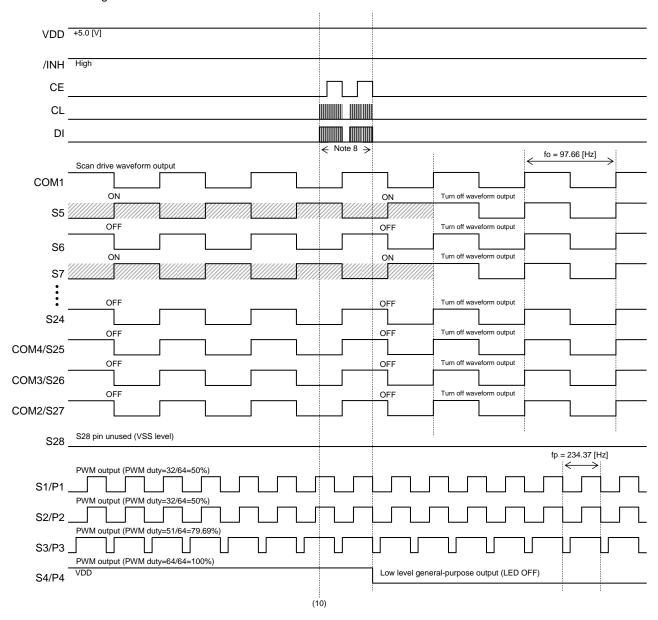

# (8) Timing Chart of the Setting to Turn off the Segments and Turn off the LED of Backlight

Next, the following figure shows the timing waveform of the display OFF (turn off the all segments) and turn off the LED of backlight.

### < Operation sequence >

(10) The command of the turn off the segments and turn off the LED of backlight setting is transferred.

### < Transfer instruction data >

```

Note 8: CCB address = (44)h, D1 to D4=all "0" data, D5=1, D6=0, D7=1, D8 to D28=all "0" data, DT0=1 and DT1=1 (Static (1/1-duty) drive), W10 to W15=1,1,1,1,1,0 (Brightness is 50%), W20 to W25=0,1,0,0,1,1 (Brightness is 79.69%), W30 to W35=1,1,1,1,1,1 (Brightness is 100%), PF0=0, PF1=1, PF2=0 and PF3=0 (fp=234.37 [Hz]), PS10=1 and PS11=1 (S1/P1=PWM output function (ch1) setting), PS20=1 and PS21=0 (S2/P2=PWM output function (ch1) setting), PS30=0 and PS31=1 (S3/P3=PWM output function (ch2) setting), PS40=0 and PS41=0 (S4/P4=Low level general-purpose output), P0=1, P1=0 and P2=0 (S1/P1 to S4/P4 are set by general-purpose output port (P1 to P4)), FC0=0, FC1=1, FC2=0 and FC3=1 (fo=97.66 [Hz]), DN=0 (S28 pin unused), EXF=0 and OC=0 (Internal oscillator operating mode), SC=1 (Set the "All segment turn off mode"),

```

BU=0 ("Power saving mode" was cancelled).

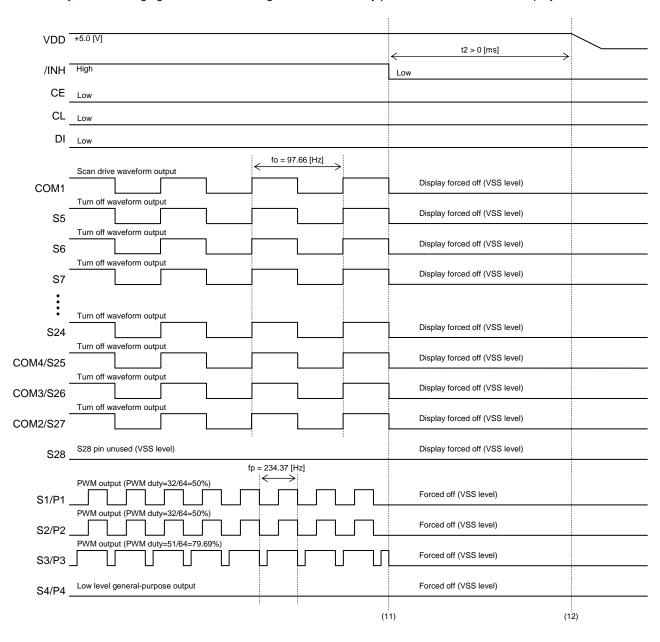

# (9) Timing Chart from LCD Display OFF to Power-off State

Finally, the following figure shows the timing waveform to set by power-off state from LCD display OFF.

### < Operation sequence >

- (11) The display forced off is set by setting the /INH pin to Low (VSS).

- (12) Power-off.

# **Application Circuit**

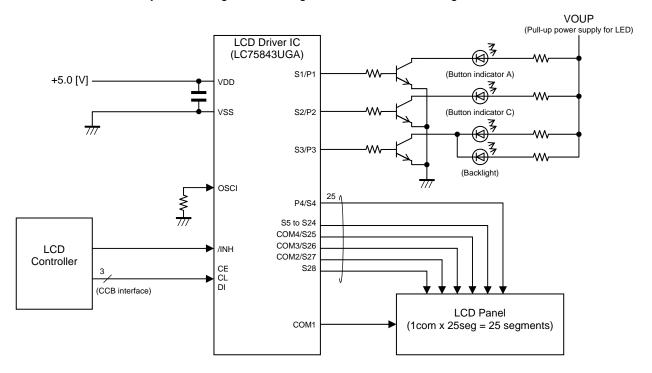

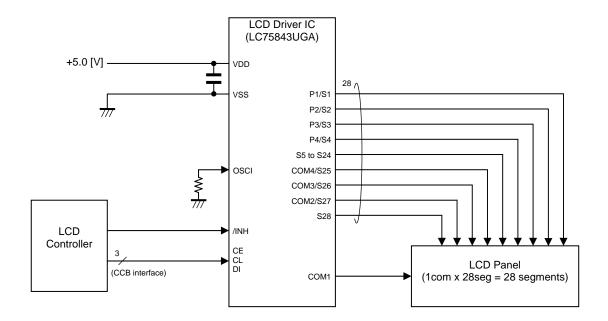

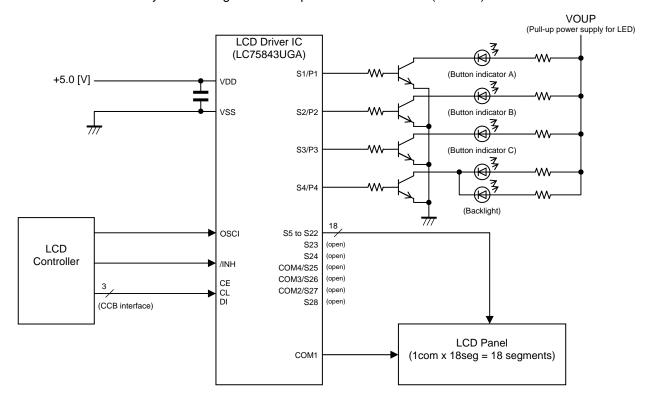

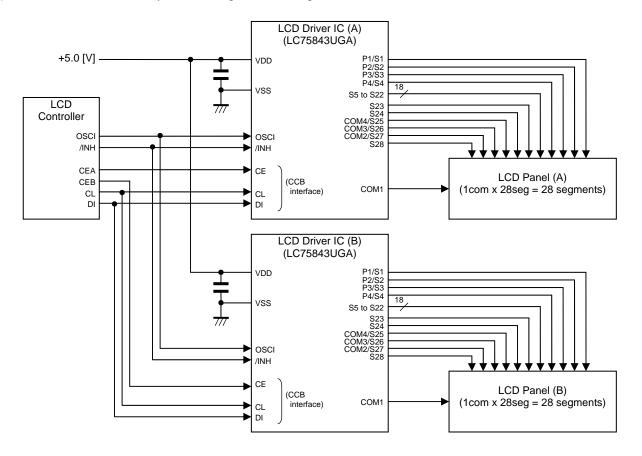

(1) In the Case of the LCD System Configuration Using the LCD Panel of 24 Segments

Figure 12. LCD system configuration using the LCD panel of 24 segments

The LC75843UGA is able to drive up to 24 segments the LCD panel of the static (1/1-duty) when the output pins from S1/P1 to S4/P4 used general-purpose output ports (P1 to P4).

The following explains a setting method example of serial control data in this case.

This system sets DT0=1 and DT1=1 to use an LCD panel of the static (1/1-duty) drive.

| DT0 DT1 | DT4            | LCD drive type                   | Output pins state |          |          |      |  |

|---------|----------------|----------------------------------|-------------------|----------|----------|------|--|

|         | LCD drive type | COM1                             | COM2/S27          | COM3/S26 | COM4/S25 |      |  |

| 0       | 0              | 1/4-duty and 1/3-bias drive type | COM1              | COM2     | COM3     | COM4 |  |