Is Now Part of

## **ON Semiconductor**®

To learn more about ON Semiconductor, please visit our website at <u>www.onsemi.com</u>

ON Semiconductor and the ON Semiconductor logo are trademarks of Semiconductor Components Industries, LLC dba ON Semiconductor or its subsidiaries in the United States and/or other countries. ON Semiconductor owns the rights to a number of patents, trademarks, copyrights, trade secrets, and other intellectual property. A listing of ON Semiconductor's product/patent coverage may be accessed at www.onsemi.com/site/pdf/Patent-Marking.pdf. ON Semiconductor reserves the right to make changes without further notice to any products herein. ON Semiconductor makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does ON Semiconductor assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. Buyer is responsible for its products and applications using ON Semiconductor dates sheds, regardless of any support or applications information provided by ON Semiconductor. "Typical" parameters which may be provided in ON Semiconductor dates sheds and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. ON Semiconductor does not convey any license under its patent rights of others. ON Semiconductor products are not designed, intended, or authorized for use on similar classification in a foreign jurisdiction or any devices intended for implantation in the human body. Should Buyer purchase or use ON Semiconductor and its officers, employees, subsidiaries, affliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out or i, directly or indirectly, any lay bed ON Semiconductor and its officers, employees, ween if such claim alleges that ON Semiconductor was negligent regarding the d

# AN-4157 Thermal Analysis of SPS in Multi-Phase Application

## Abstract

Thermal performance is one of the key validation items for power devices in most systems, especially in multi-phase power applications. The main factors that impact the thermal performance of power MOSFET device include: power losses, PCB stack-up, airflow, and heat sink. The purpose of this application note is to evaluate the effects of these factors on the Smart Power Stage (SPS) thermal performance.

## Introduction

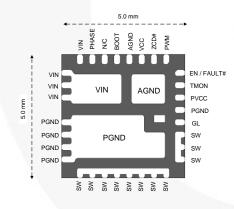

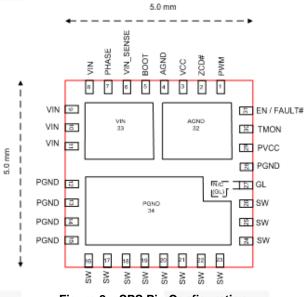

The Smart Power Stage (SPS) is a family of highly efficient synchronous buck power stages. The SPS packages three discrete dies to form a 5 mm x 5 mm power-stage solution using PowerTrench® MOSFETs and a lower impedance, lower dead time, gate driver. The top-side transparent view of SPS is shown in Figure 1.

Top Side Transparent View

Figure 1. Top-Side Transparent View

High-performance PQFN package with "flip-chip" low-side (LS) MOSFET improves thermals and lowers LS source inductance. Flip chip low-side MOSFETs use the PGND plane to pull heat away from LS MOSFET and add a top-side heat slug for dual cooling. The pin configuration of SPS is shown in Figure 2.

Figure 2. SPS Pin Configuration

## Thermal Analysis

## Thermal Effect of PCB Stack-up

This section explains the key features of PCB stack-up for thermal performance. The board configuration and test setup for thermal validation are shown in Table 1.

Table 1. Validation Configuration

| Jane II Janaanon Sonngananon |                                       |  |  |

|------------------------------|---------------------------------------|--|--|

| Smart Power Stage            | FDMF5821DC                            |  |  |

| Switching Frequency          | 350 kHz                               |  |  |

| Input Voltage                | 12.2 V                                |  |  |

| Output Voltage               | 1.8 V Output with<br>1.05mΩ Load Line |  |  |

| Choke                        | FP1007R3-R17-R<br>(170 nH, 0.29 mΩ)   |  |  |

| Number of Phases Active      | 5 Phases                              |  |  |

| Soaking Time                 | 20 min. for Each Load                 |  |  |

| Temperature Sense            | K-Type Thermal Couple                 |  |  |

APPLICATION NOTE

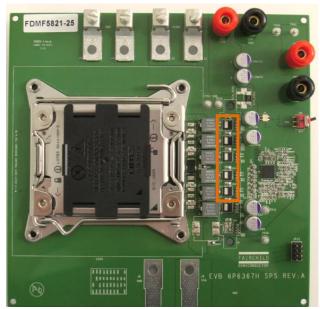

#### 6P6367H\_SPS\_A00 Demo Board

The 6P6367H\_SPS\_A00 Demo Board is used for SPS multi-phase characterization. The board specifications and structure are shown in Table 2, Figure 3, and Figure 4.

| Table 2. | Evaluation | Board | Structure |

|----------|------------|-------|-----------|

|          |            |       |           |

| Dimension       | 165 mm*162mm        |  |  |

|-----------------|---------------------|--|--|

| No. of Layers   | 8 Layers            |  |  |

| Total Thickness | 1.575 mm            |  |  |

| PCB Stack-up    | 2-2-2-2-2-2-2 (oz.) |  |  |

| 1 | Cu 1.5oz+ Plating 0.5oz | TOP (Signal/GND/PWR) : total 2oz, 0.061 mm |

|---|-------------------------|--------------------------------------------|

|   | Prepreg 0.203mm         |                                            |

| 2 | Cu                      | IN1 (GND) : 2oz , 0.061 mm                 |

|   | Core 0.106mm            |                                            |

| 3 | Cu                      | IN2 (Signal/GND) : 2oz , 0.061 mm          |

|   | Prepreg 0.18mm          |                                            |

| 4 | Cu                      | IN3 (GND/PWR) : 2oz, 0.061 mm              |

|   | Core 0.106mm            |                                            |

| 5 | Cu                      | IN4 (GND/PWR) : 2oz, 0.061 mm              |

|   | Prepreg 0.18mm          |                                            |

| 6 | Cu                      | IN5 (Signal/GND) : 2oz , 0.061 mm          |

|   | Core 0.106mm            |                                            |

| 7 | Cu                      | IN6 (GND) : 2oz , 0.061 mm                 |

|   | Prepreg 0.203mm         |                                            |

| 8 | Cu 1.5oz+ Plating 0.5oz | BOT (Signal/GND/PWR) : total 2oz, 0.061 mm |

Figure 3. Evaluation Board Stack-up

The 5-phase placement area marked in Figure 4 is 45 mm x 11.5 mm.

Figure 4. Board Photograph (A00 and A01)

### **Thermal Validation Results**

The 6P6367H\_SPS\_A00 Demo Board thermal test results are shown in Table 3. The total loss includes 5-phase choke, SPS, and PCB power loss. The module loss per phase is without choke loss.

#### Table 3. Thermal without Airflow or Heat Sink

| Output Load (A)           | 85    | 120    | 150    |

|---------------------------|-------|--------|--------|

| Total Loss (W)            | 8.525 | 13.054 | 18.267 |

| Module Loss per Phase (W) | 1.505 | 2.328  | 3.276  |

| Temp. (°C) at Phase 1     | 57.08 | 78.21  | 102.89 |

| Temp. (°C) at Phase 2     | 58.07 | 79.80  | 105.13 |

| Temp. (°C) at Phase 3     | 54.12 | 73.17  | 95.23  |

| Temp. (°C) at Phase 4     | 58.94 | 80.86  | 106.57 |

| Temp. (°C) at Phase 5     | 53.83 | 73.49  | 96.01  |

#### 6P6367H\_SPS \_A01 Demo Board

The 6P6367H\_SPS\_A01 Demo Board is used for SPS multi-phase characterization validation. The board specifications and structure are shown in Table 4 and Figure 5. The board photograph is the same with 6P6367H\_SPS\_A00 board as Figure 4.

| Table 4. | Evaluation | Board | Structure |

|----------|------------|-------|-----------|

|----------|------------|-------|-----------|

|   | Dimension                                  | 165 mm*162 mm                              |

|---|--------------------------------------------|--------------------------------------------|

|   | No. of Layers                              | 8 Layers                                   |

| ٦ | Fotal Thickness                            | 1.531 mm                                   |

|   | PCB Stack-up                               | 2-1-1-2-2-1-1-2 (oz.)                      |

| 1 | Cu 1.5oz+ Plating 0.5oz<br>Prepreg 0.203mm | TOP (Signal/GND/PWR) : total 2oz, 0.061 mm |

| 2 | Cu                                         | IN1 (GND) : 1oz , 0.030 mm                 |

| 3 | Core 0.106mm                               | IN2 (Signal/GND) : 1oz , 0.030 mm          |

| 4 | Prepreg 0.18mm<br>Cu                       | IN3 (GND/PWR) : 2oz, 0.061 mm              |

| 5 | Core 0.106mm<br>Cu                         | IN4 (GND/PWR) : 2oz, 0.061 mm              |

| 6 | Prepreg 0.18mm<br>Cu                       | IN5 (Signal/GND) : 1oz , 0.030 mm          |

| 7 | Core 0.106mm                               | IN6 (GND) : 1oz, 0.030 mm                  |

|   | Prepreg 0.203mm                            |                                            |

| 8 | Cu 1.5oz+ Plating 0.5oz                    | BOT (Signal/GND/PWR) : total 2oz, 0.061 mm |

Figure 5. Evaluation Board Stack-up

### **Thermal Validation Results**

The 6P6367H\_SPS\_A01 Demo Board thermal test results are shown in Table 5. The total loss includes 5-phase choke, SPS, and PCB power loss. The module loss per phase is without choke loss.

| Table 5. | Thermal without Airflow or Heat Sink |

|----------|--------------------------------------|

|----------|--------------------------------------|

| Output Load (A)           | 85    | 120    | 150    |

|---------------------------|-------|--------|--------|

| Total Loss (W)            | 8.415 | 12.850 | 18.325 |

| Module Loss per Phase (W) | 1.483 | 2.287  | 3.288  |

| Temp. (°C) at Phase 1     | 61.70 | 86.04  | 112.85 |

AN-4157

| Temp. (°C) at Phase 2 | 61.49 | 86.17 | 114.09 |

|-----------------------|-------|-------|--------|

| Temp. (°C) at Phase 3 | 58.19 | 79.76 | 104.25 |

| Temp. (°C) at Phase 4 | 62.66 | 88.19 | 116.69 |

| Temp. (°C) at Phase 5 | 57.87 | 79.97 | 104.91 |

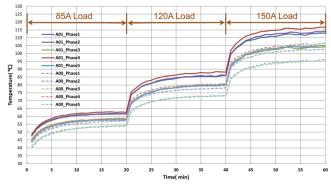

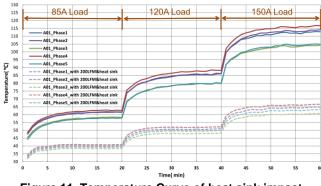

The thermal curve of PCB stack-up impact is shown in Figure 6. The phase 4 SPS is the hotspot and phase 3 SPS temperature is the lowest of five phases.

Figure 6. Temperature Curve of PCB impact

#### Effect of PCB Stack-up

The main factor between Table 3 and Table 5 thermal test results is PCB stack-up. PCB stack-up impacts the thermal performance as shown in Table 6. All eight layers of 6P6367H\_SPS\_A00 Demo Board are 2-oz copper, the thermal performance of it is better. The hotspot temperature gaps of PCB stack-up effect are  $3.72^{\circ}$ C at 1.505 W power loss condition,  $7.33^{\circ}$ C at 2.328 W power loss condition, and  $10.12^{\circ}$ C at 3.276 W power loss condition.

| Table 6. | Temperature | Gap of F | PCB Stack-up |

|----------|-------------|----------|--------------|

|----------|-------------|----------|--------------|

| Output Load (A)                 | 85   | 120  | 150   |

|---------------------------------|------|------|-------|

| T <sub>GAP</sub> (°C) at Phase1 | 4.62 | 7.83 | 9.96  |

| T <sub>GAP</sub> (°C) at Phase2 | 3.42 | 6.37 | 8.96  |

| T <sub>GAP</sub> (°C) at Phase3 | 4.07 | 6.59 | 9.02  |

| T <sub>GAP</sub> (°C) at Phase4 | 3.72 | 7.33 | 10.12 |

| T <sub>GAP</sub> (°C) atPhase5  | 4.04 | 6.48 | 8.90  |

#### Effect of Airflow without Heat Sink

This section explains the effects of airflow on the thermal performance, without heat sink. The board configuration and test setup for thermal validation are shown in Table 7.

| Evaluation Board    | 6P6367H_SPS Demo<br>Board_A01 |

|---------------------|-------------------------------|

| Smart Power Stage   | FDMF5821DC                    |

| Switching Frequency | 350 kHz                       |

| Input Voltage       | 12.2 V                        |

| Output Voltage    | 1.8 V Output with     |

|-------------------|-----------------------|

| Output Voltage    | 1.05 mΩ Load Line     |

| Choke             | FP1007R3-R17-R        |

| Choke             | (170 nH, 0.29 mΩ)     |

| Active Phases     | 5 Phases              |

| Soaking Time      | 20 min for Each Load  |

| Temperature Sense | K-Type Thermal Couple |

|                   |                       |

#### **Thermal Validation Results**

The thermal test results of without airflow and without heat sink are shown in Table 8. The total loss is including 5-phase choke, SPS, and PCB power loss. Based on 120 A output load results, SPS can handle 2.287 W power loss per phase under 90°C at 5-phase applications. The module loss per phase is without choke loss.

| Table 8. Thermal without Airfl | ow or Heat Sink |

|--------------------------------|-----------------|

|--------------------------------|-----------------|

| Output Load (A)           | 85    | 120    | 150    |

|---------------------------|-------|--------|--------|

| Total Loss (W)            | 8.415 | 12.850 | 18.325 |

| Module Loss per Phase (W) | 1.483 | 2.287  | 3.288  |

| Temp. (°C) at Phase 1     | 61.70 | 86.04  | 112.85 |

| Temp. (°C) at Phase 2     | 61.49 | 86.17  | 114.09 |

| Temp. (°C) at Phase 3     | 58.19 | 79.76  | 104.25 |

| Temp. (°C) at Phase 4     | 62.66 | 88.19  | 116.69 |

| Temp. (°C) at Phase 5     | 57.87 | 79.97  | 104.91 |

The thermal test results with 200 LFM airflow and without heat sink are shown in Table 9. The total loss is including 5-phase choke, SPS, and PCB power loss. Based on 150 A output load results, SPS can handle 3.07 W power loss per phase under 90°C at 5-phase applications with 200 LFM airflow. The module loss per phase is without choke loss.

Table 9. Thermal with 200 LFM Airflow, withoutHeat Sink

| Output Load (A)           | 85    | 120    | 150    |

|---------------------------|-------|--------|--------|

| Total Loss (W)            | 8.256 | 12.261 | 17.233 |

| Module Loss per Phase (W) | 1.451 | 2.169  | 3.070  |

| Temp. (°C) at Phase 1     | 48.84 | 65.56  | 85.76  |

| Temp. (°C) at Phase 2     | 48.69 | 65.44  | 86.62  |

| Temp. (°C) at Phase 3     | 45.46 | 60.40  | 77.93  |

| Temp. (°C) at Phase 4     | 49.67 | 66.77  | 88.46  |

| Temp. (°C) at Phase 5     | 45.44 | 60.65  | 79.16  |

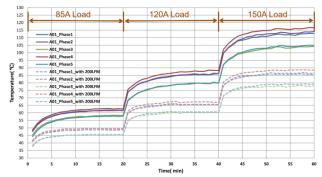

The thermal curve of 200LFM airflow impact is shown in Figure 7. The phase-4 SPS is the hotspot and phase-3 SPS temperature is the lowest of five phases.

AN-4157

Figure 7. Temperature Curve of Air Flow Impact

The main factor difference between Table 8 and Table 9 thermal test results is airflow. The airflow setup is 200 LFM for Table 9 validation results. Airflow impacts the thermal performance, as shown in Table 10. The hotspot temperature gaps of airflow effect are 12.99°C with 0.032 W power loss gap, 21.42°C with 0.118 W power loss gap, and 28.23°C with 0.218 W power loss gap.

| Output Load (A)                  | 85    | 120   | 150   |

|----------------------------------|-------|-------|-------|

| P <sub>GAP</sub> (W) per Phase   | 0.032 | 0.118 | 0.218 |

| T <sub>GAP</sub> (°C) at Phase 1 | 12.86 | 20.48 | 27.09 |

| T <sub>GAP</sub> (°C) at Phase 2 | 12.80 | 20.73 | 27.47 |

| T <sub>GAP</sub> (°C) at Phase 3 | 12.73 | 19.36 | 26.32 |

| T <sub>GAP</sub> (°C) at Phase 4 | 12.99 | 21.42 | 28.23 |

| T <sub>GAP</sub> (°C) at Phase 5 | 12.43 | 19.32 | 25.75 |

Table 10. Temperature Gap of 200LFM Airflow

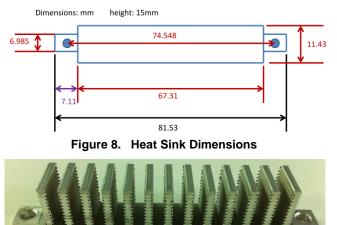

#### Effect of Heat Sink without Airflow

The thermal test results of without airflow and with heat sink are shown in Table 11. The total loss includes 5-phase choke, SPS, and PCB power loss. Based on 150 A output load results, SPS can handle 3.211 W power loss per phase under 100°C at 5-phase applications with heat sink. The module loss per phase is without choke loss.

#### **Heat Sink Dimension**

Figure 9. Heat Sink Photograph

APPLICATION NOTE

| Output Load (A)           | 85    | 120    | 150    |

|---------------------------|-------|--------|--------|

| Total Loss (W)            | 8.437 | 12.533 | 17.938 |

| Module Loss per Phase (W) | 1.487 | 2.224  | 3.2110 |

| Temp. (°C) at Phase 1     | 55.50 | 74.77  | 96.61  |

| Temp. (°C) at Phase 2     | 54.68 | 73.65  | 94.94  |

| Temp. (°C) at Phase 3     | 53.22 | 71.00  | 90.81  |

| Temp. (°C) at Phase 4     | 55.47 | 74.96  | 96.93  |

| Temp. (°C) at Phase 5     | 53.77 | 72.14  | 92.63  |

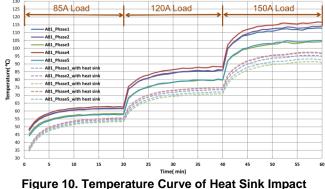

The thermal curve of heat sink impact is shown in Figure 10. The phase-4 SPS is the hotspot and phase-3 SPS temperature is the lowest of five phases.

Figure 10. Temperature Curve of Heat Sink Impact

The main difference between Table 8 and Table 11 thermal test results is the heat sink. The heat sink dimension is described as Figure 8. Heat sink impacts the thermal performance as shown in Table 12. The hotspot temperature gaps of heat sink effect are 7.19°C with 0.004 W power loss gap, 13.23°C with 0.063 W power loss gap, and 28.23°C with 0.078 W power loss gap.

Table 12. Temperature Gap of Heat Sink

| Output Load (A)                  | 85    | 120   | 150   |

|----------------------------------|-------|-------|-------|

| P <sub>GAP</sub> (W) per Phase   | 0.004 | 0.063 | 0.078 |

| T <sub>GAP</sub> (°C) at Phase 1 | 6.20  | 11.27 | 16.24 |

| T <sub>GAP</sub> (°C) at Phase 2 | 6.81  | 12.52 | 19.15 |

| T <sub>GAP</sub> (°C) at Phase 3 | 4.97  | 8.76  | 13.44 |

| T <sub>GAP</sub> (°C) at Phase 4 | 7.19  | 13.23 | 19.76 |

| T <sub>GAP</sub> (°C) at Phase 5 | 4.10  | 7.83  | 12.28 |

#### Effects of Airflow with Heat Sink

The thermal test results with 200 LFM airflow and heat sink are shown in Table 13. The total loss includes 5-phase choke, SPS, and PCB power loss. Based on 150 A output load results, SPS can handle 2.957 W power loss per phase under 70°C at 5-phase applications with 200LFM airflow and heat sink. The module loss per phase is without choke loss.

AN-4157

| Output Load (A)           | 85    | 120    | 150    |

|---------------------------|-------|--------|--------|

| Total Loss (W)            | 8.308 | 12.028 | 16.669 |

| Module Loss per Phase (W) | 1.462 | 2.123  | 2.957  |

| Temp. (°C) at Phase 1     | 40.88 | 52.27  | 66.52  |

| Temp. (°C) at Phase 2     | 39.97 | 51.01  | 64.82  |

| Temp. (°C) at Phase 3     | 38.38 | 48.25  | 60.74  |

| Temp. (°C) at Phase 4     | 40.74 | 52.26  | 66.65  |

| Temp. (°C) at Phase 5     | 39.28 | 49.90  | 63.13  |

Table 13. Thermal with 200 LFM Airflow, Heat Sink

The thermal curve of 200 LFM airflow with heat sink impacts is shown in Figure 11. The phase-4 SPS is the hotspot and phase-3 SPS temperature is the lowest of five phases.

Figure 11. Temperature Curve of heat sink impact

Factors between Table 8 and Table 13 thermal test results are airflow and heat sink. The airflow setup is 200 LFM and the heat sink dimension is described in Figure 8. Airflow and heat sink impact on thermal performance are shown in Table 14. The hotspot temperature gaps of 200 LFM airflow and heat sink effect are 21.92°C with 0.021 W power loss gap, 35.93°C with 0.164 W power loss gap, and 50.04°C with 0.331 W power loss gap.

Table 14. Temperature Gap of 200 LFM Airflowand Heat Sink

| Output Load (A)                  | 85    | 120   | 150   |

|----------------------------------|-------|-------|-------|

| P <sub>GAP</sub> (W) per Phase   | 0.021 | 0.164 | 0.331 |

| T <sub>GAP</sub> (°C) at Phase 1 | 20.82 | 33.77 | 46.33 |

| T <sub>GAP</sub> (°C) at Phase 2 | 21.52 | 35.16 | 49.27 |

| T <sub>GAP</sub> (°C) at Phase 3 | 19.81 | 31.51 | 43.51 |

| T <sub>GAP</sub> (°C) at Phase 4 | 21.92 | 35.93 | 50.04 |

| T <sub>GAP</sub> (°C) at Phase 5 | 18.59 | 30.07 | 41.78 |

## Summary

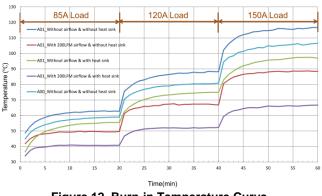

The phase-4 burn-in 20-minute temperature curves of 85 A, 120 A, and 150 A output load are shown in Figure 12. According to the curve, the temperature is thermal balanced after 15 minutes of burn-in.

Figure 12. Burn-in Temperature Curve

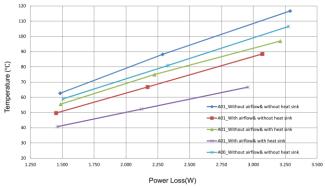

Figure 13 is phase-4 thermal and power loss results based on different conditions. It is helpful to anticipate the temperature of power loss under different conditions. According to this curve, SPS can handle 2.75 W power loss around 102°C without airflow and without heat sink, 87°C with heat sink, 81°C with 200 LFM airflow, and 63°C with heat sink and 200 LFM airflow based on A01 PCB stack up.

Figure 13. Temperature Curve of Power Loss

#### DISCLAIMER

FAIRCHILD SEMICONDUCTOR RESERVES THE RIGHT TO MAKE CHANGES WITHOUT FURTHER NOTICE TO ANY PRODUCTS HEREIN TO IMPROVE RELIABILITY, FUNCTION, OR DESIGN. FAIRCHILD DOES NOT ASSUME ANY LIABILITY ARISING OUT OF THE APPLICATION OR USE OF ANY PRODUCT OR CIRCUIT DESCRIBED HEREIN; NEITHER DOES IT CONVEY ANY LICENSE UNDER ITS PATENT RIGHTS, NOR THE RIGHTS OF OTHERS.

#### LIFE SUPPORT POLICY

FAIRCHILD'S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF THE PRESIDENT OF FAIRCHILD SEMICONDUCTOR CORPORATION. As used herein:

- Life support devices or systems are devices or systems which, (a) are intended for surgical implant into the body, or (b) support or sustain life, or (c) whose failure to perform when properly used in accordance with instructions for use provided in the labeling, can be reasonably expected to result in significant injury to the user.

- A critical component is any component of a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system, or to affect its safety or effectiveness.

ON Semiconductor and are trademarks of Semiconductor Components Industries, LLC dba ON Semiconductor or its subsidiaries in the United States and/or other countries. ON Semiconductor owns the rights to a number of patents, trademarks, copyrights, trade secrets, and other intellectual property. A listing of ON Semiconductor's product/patent coverage may be accessed at <u>www.onsemi.com/site/pdf/Patent-Marking.pdf</u>. ON Semiconductor reserves the right to make changes without further notice to any products herein. ON Semiconductor makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does ON Semiconductor assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. Buyer is responsible for its products and applications using ON Semiconductor products, including compliance with all laws, regulations and safety requirements or standards, regardless of any support or applications information provided by ON Semiconductor. "Typical" parameters which may be provided in ON Semiconductor data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. ON Semiconductor does not convey any license under its patent rights of others. ON Semiconductor products are not designed, intended, or authorized for use as a critical component in life support systems or any FDA Class 3 medical devices or medical devices with a same or similar classification in a foreign jurisdiction or any devices intended for implantation in the human body. Should Buyer purchase or use ON Semiconductor has against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death ass

#### PUBLICATION ORDERING INFORMATION

#### LITERATURE FULFILLMENT:

Literature Distribution Center for ON Semiconductor 19521 E. 32nd Pkwy, Aurora, Colorado 80011 USA Phone: 303-675-2175 or 800-344-3860 Toll Free USA/Canada Fax: 303-675-2176 or 800-344-3867 Toll Free USA/Canada Email: orderlit@onsemi.com N. American Technical Support: 800–282–9855 Toll Free USA/Canada Europe, Middle East and Africa Technical Support: Phone: 421 33 790 2910

Japan Customer Focus Center Phone: 81-3-5817-1050 ON Semiconductor Website: www.onsemi.com

Order Literature: http://www.onsemi.com/orderlit

For additional information, please contact your local Sales Representative

© Semiconductor Components Industries, LLC