# NCV7748 LIN Communication Using Virtual Nodes

Communication speeds are not always fast. LIN protocol allows operation at relatively slow speeds. The NCV7748 allows operation at 10.417 kBit/sec or 19.2 kBit/sec. With wave shaping and these low bit rates, emissions are kept at a minimum.

While low bit rates have low emissions, low bit rates also have their detriment. Latency times would seemingly prohibit the use at low bit rates when controlling multiple nodes required to switch concurrently. Multiple command times would take too long.

ON Semiconductor®

www.onsemi.com

## **APPLICATION NOTE**

The LIN network dynamics also limit the use at 15 nodes and 1 master node. This boundary sets the maximum number of actuator loads at 16 per system time constant limitations. This can be extended with dedicated design focus but is risky.

The use of a LIN virtual node in the NCV7748 expands the number of nodes by a factor of 4. With 8 relay drivers integrated into the NCV7748 and the virtual node implementation, one node can control 32 relay drivers. And since the NCV7748 Output Control Command linked to SAEJ2602 defines 7 Node Address (NAD) locations, system design can support  $7 \times 32 = 224$  relay drivers.

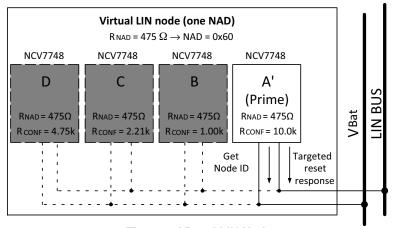

Figure 1. Virtual LIN Node

Figure 1 highlights the concept of a Virtual LIN node used in the NCV7748. The gray box is representative of one slave node on the LIN bus. As you can see there are 4 separate components labeled A', B, C, & D connected directly to the LIN BUS and to the battery (Vbat) located within the node on the LIN BUS.

The programming resistor values listed in Table 1 and Table 2 are the programming values required by the NCV7748 describing their location on the BUS. These programming resistors ( $R_{NAD}$  and  $R_{CONF}$ ) are directly connected on the NAD and CONF pins of the NCV7748 devices to ground. Their sole purpose is to identify the NAD and the location on the NAD (the config [CONF]).

Slave location via these programming resistors is read during the first 10 ms of power–up in the initialization mode by the NCV7748 device (T\_init of the datasheet).

Table 1. VIRTUAL SLAVE NODE ADDRESS (NAD)

| NAD              | 0x60  | 0x62    | 0x64    | 0x66                    | 0x68    | 0x6A    | 0x6C    |

|------------------|-------|---------|---------|-------------------------|---------|---------|---------|

| R <sub>NAD</sub> | 475 Ω | 1.00 kΩ | 2.21 kΩ | $4.75~\mathrm{k}\Omega$ | 10.0 kΩ | 22.1 kΩ | 47.5 kΩ |

Table 2. VIRTUAL SLAVE NODE CONFIGURATION (CONF)

| Slave   | Α     | В                       | С       | D                       | A'              | B'      | C,      | D'       |

|---------|-------|-------------------------|---------|-------------------------|-----------------|---------|---------|----------|

| RConfig | 475 Ω | $1.00~\mathrm{k}\Omega$ | 2.21 kΩ | $4.75~\mathrm{k}\Omega$ | 10.0 k $\Omega$ | 22.1 kΩ | 47.5 kΩ | 100.0 kΩ |

#### AND9423/D

####

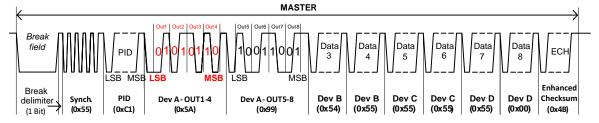

Figure 2. Device Setup

# **Output Control Frame**

Table 3 illustrates the data structure of the Output Control Frame. Prime nodes are included, but not specified in the A, B, C, D labels. To turn outputs on or off, one must simply use the logic as given in Table 4 putting the data into the boxes and sending a LIN command with this information.

# Table 3. OUTPUT CONTROL FRAME

|        |      |            | Structure         |       |        |       |        |       |        |       |

|--------|------|------------|-------------------|-------|--------|-------|--------|-------|--------|-------|

|        | Byte | Content    | Bit 7             | Bit 6 | Bit 5  | Bit 4 | Bit 3  | Bit 2 | Bit 1  | Bit 0 |

|        | 0    | Identifier |                   | PID   |        |       |        |       |        |       |

| Master | 1    | Data 1     | OUT4_A            |       | OUT3_A |       | OUT2_A |       | OUT1_A |       |

|        | 2    | Data 2     | OUT8_A            |       | OUT7_A |       | OUT6_A |       | OUT5_A |       |

|        | 3    | Data 3     | OUT4_B            |       | OUT3_B |       | OUT2_B |       | OUT1_B |       |

|        | 4    | Data 4     | OUT8_B            |       | OUT7_B |       | OUT6_B |       | OUT5_B |       |

|        | 5    | Data 5     | OUT4_C            |       | OUT3_C |       | OUT2_C |       | OUT1_C |       |

|        | 6    | Data 6     | OUT8_C            |       | OUT7_C |       | OUT6_C |       | OUT5_C |       |

|        | 7    | Data 7     | OUT4_D            |       | OUT3_D |       | OUT2_D |       | OUT1_D |       |

|        | 8    | Data 8     | OUT8_D            |       | OUT7_D |       | OUT6_D |       | OUT5_D |       |

|        | 9    | Checksum   | Enhanced Checksum |       |        |       |        |       |        |       |

**Table 4. OUTPUT DECODING**

| OUTx_A[1] | OUTx_A[0] | Output    |

|-----------|-----------|-----------|

| 0         | 0         | No change |

| 0         | 1         | OUTx Off  |

| 1         | 0         | OUTx On   |

| 1         | 1         | No change |

Figure 3 shows what a typical LIN Output Controls Frame would look like. Data for Dev A – OUT 1–4 and Dev OUT 5–8 specify the output state or state change. Special care should be taken when identifying and specifying the LSB and MSB information. It is not intuitive. In this case OUT1,2,3,6, & 8 are commanded on.

The data for OUT1–4 where OUT1,2,& 3 are commanded on (MSB  $\rightarrow$  LSB 01101010 in the table looks like a mirror image LSB  $\rightarrow$  MSB 01010110 in the waveform) is highlighted in red.

Note OUT1 is 1<sup>st</sup> in the waveform and last in the table.

Figure 3. LIN Output Control Frame

## **Prime Nodes**

This virtual node concept works because all potential conflicts have been considered and resolved. Without a device branded as prime, there would be conflicts with commands Get Node ID and Targeted Reset. Without a prime, multiple devices on the same node would respond. In

this case only the Prime device responds. To avoid impedance issues, only the prime device connects an internal 33k pull-up resistor from LIN to VBB. No pullup up is connected for non-prime devices.

#### AND9423/D

## **Output Status**

Each individual IC on the virtual node still responds to its own GET STATUS command for reporting of errors and APPINFO. Error fields are cleared after a read and reported individually. Multiple errors may be retrieved by multiple GET STATUS commands. Reporting of error states are reported from highest priority to lowest priority as shown in Table 5.

Table 5. J2602-1 ERROR FIELD

| ERR2 | ERR1 | ERR0 | Error States             | Priority    |

|------|------|------|--------------------------|-------------|

| 0    | 0    | 0    | No Error                 | 0 (lowest)  |

| 0    | 0    | 1    | Reset                    | 1           |

| 0    | 1    | 0    | Reserved                 | 2           |

| 0    | 1    | 1    | Reserved                 | 3           |

| 1    | 0    | 0    | Data Error               | 4           |

| 1    | 0    | 1    | Data Checksum            | 5           |

| 1    | 1    | 0    | Byte Field Framing Error | 6           |

| 1    | 1    | 1    | ID Parity Error          | 7 (highest) |

#### **Virtual Node Error Detection Considerations**

There may be multiple detections of a single error within a virtual node.

- a. Example Reset status will be reported by all devices on a node after a reset command.

- b. Example Every device on a node will report a checksum error (in status byte) from corrupted checksum and must be cleared individually.

ON Semiconductor and ware trademarks of Semiconductor Components Industries, LLC dba ON Semiconductor or its subsidiaries in the United States and/or other countries. ON Semiconductor owns the rights to a number of patents, trademarks, copyrights, trade secrets, and other intellectual property. A listing of ON Semiconductor's product/patent coverage may be accessed at <a href="https://www.onsemi.com/site/pdf/Patent-Marking.pdf">www.onsemi.com/site/pdf/Patent-Marking.pdf</a>. ON Semiconductor reserves the right to make changes without further notice to any products herein. ON Semiconductor makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does ON Semiconductor assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. Buyer is responsible for its products and applications using ON Semiconductor products, including compliance with all laws, regulations and safety requirements or standards, regardless of any support or applications information provided by ON Semiconductor. "Typical" parameters which may be provided in ON Semiconductor data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. ON Semiconductor does not convey any license under its patent rights nor the rights of others. ON Semiconductor products are not designed, intended, or authorized for use as a critical component in life support systems or any FDA Class 3 medical devices or medical devices with a same or similar classification in a foreign jurisdiction or any devices intended for implantation in the human body. Should Buyer purchase or use ON Semiconductor products for any such unintended or unauthorized application, Buyer shall indemnify a

## **PUBLICATION ORDERING INFORMATION**

#### LITERATURE FULFILLMENT:

Literature Distribution Center for ON Semiconductor 19521 E. 32nd Pkwy, Aurora, Colorado 80011 USA Phone: 303-675-2175 or 800-344-3860 Toll Free USA/Canada Fax: 303-675-2176 or 800-344-3867 Toll Free USA/Canada Email: orderlit@onsemi.com N. American Technical Support: 800–282–9855 Toll Free USA/Canada Europe, Middle East and Africa Technical Support:

Europe, Middle East and Africa Technical Support: Phone: 421 33 790 2910 Japan Customer Focus Center Phone: 81-3-5817-1050 ON Semiconductor Website: www.onsemi.com

Order Literature: http://www.onsemi.com/orderlit

For additional information, please contact your local Sales Representative