# Designing a LED Driver with the NCL30080/81/82/83

# ON Semiconductor®

www.onsemi.com

# **APPLICATION NOTE**

The NCL3008X is a family of 4 controllers in 2 different

packages (Micro 8 and TSOP6). The 8 pin packaged parts

have 2 extra pins for Dimming and thermal/over voltage

#### Introduction

As LED lighting finds its way into low wattage applications, lamp designers are challenged for a variety of conflicting requirements. Size is often dictated by the incumbent lamp and fixture size whether it's A19, GU10, etc. Thermal performance, reliability, safety, and EMC requirements also present design challenges. The NCL3008X family of controllers incorporates all the features and protection needed to design compact low wattage LED drivers with a minimum of external components.

#### **Table 1. PRODUCT MATRIX**

| Packago                                 | Thormal Foldback   | Analog/Digital Dimming | E Stop I OC Dimming |

|-----------------------------------------|--------------------|------------------------|---------------------|

| RIX                                     |                    |                        |                     |

| eeded to design cor<br>ith a minimum of | f external and pro | 1 1 0 1                |                     |

|                                         |                    | 1                      | e                   |

Overview

| Product     | Package | Thermal Foldback | Analog/Digital Dimming | 5 Step LOG Dimming |

|-------------|---------|------------------|------------------------|--------------------|

| NCL30080A/B | TSOP6   | No               | No                     | No                 |

| NCL30081A/B | TSOP6   | No               | No                     | Yes                |

| NCL30082A/B | Micro-8 | Yes              | Yes                    | No                 |

| NCL30083A/B | Micro-8 | Yes              | Soft-start             | Yes                |

In the A versions of the NCL3008X, some protections are latched. In the B versions, all faults are auto-recoverable.

The controllers have a built in control algorithm that allows to precisely regulate the output current of a Flyback converter from the primary side. This eliminates the need for an optocoupler and associated circuitry. The control scheme also support Buck-boost and SEPIC topology. The output current regulation is within  $\pm 2\%$  over a line range of 85-265 V rms.

The power control uses a Critical Conduction Mode (CrM) approach with valley switching to optimize efficiency and EMI filtering. The controller selects the appropriate valley for operation which keeps the frequency within a tighter range than would normally be possible with simple CrM operation.

#### **Constant Current Control**

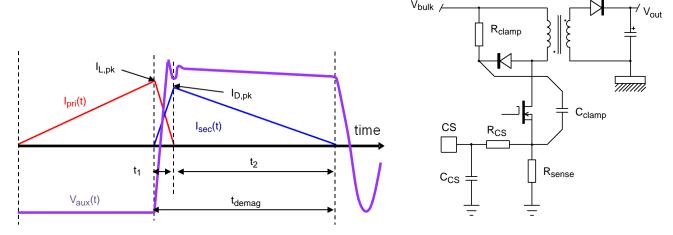

In a Flyback converter, the leakages inductances slow down the primary current decay and the secondary current rise. Thus, the current transfer from primary to secondary side is delayed and the secondary peak current is reduced:

$$I_{D,pk} < \frac{I_{L,pk}}{N_{SD}} \tag{eq. 1} \label{eq:eq. 1}$$

The diode current reaches its peak when the leakage inductor is reset. Thus, in order to accurately regulate the

output current, the leakage inductor current must be taken into account. This is accomplished by sensing the clamping network current. Practically, a node of the clamp capacitor is connected to  $R_{\text{sense}}$  instead of the bulk voltage  $V_{\text{bulk}}$ . Then, by reading the voltage on the CS pin, we have an image of the primary current (red curve in Figure 3).

When the diode conducts, the secondary current decreases linearly from  $I_{D,pk}$  to zero. When the diode current has turned off, the drain voltage begins to oscillate because of the resonating network formed by the inductors  $(L_p + L_{leak})$  and the lump capacitor. This voltage is reflected on the auxiliary winding wired in fly-back mode. Thus, by looking at the auxiliary winding voltage, we can detect the end of the conduction time of secondary diode. The constant current control block picks up the leakage inductor current, the end of conduction of the output rectifier and controls the drain current to maintain the output current  $I_{\text{out}}$  constant. We have:

$$I_{\text{out}} = \frac{V_{\text{REF}}}{2N_{\text{sp}}R_{\text{sense}}}$$

(eq. 2)

The output current value is set by choosing the sense resistor:

$$R_{sense} = \frac{V_{ref}}{2N_{sp}I_{out}}$$

(eq. 3)

1

From (eq.2), the first key point is that the output current is independent of the inductor value. Moreover, the leakage

inductance does not influence the output current value as the reset time is taken into account by the controller.

Figure 1. Fly-back Currents and Auxiliary Winding Voltage in DCM

Figure 2. Fly-back Converter

# **Design Rules for Accurate Current Control**

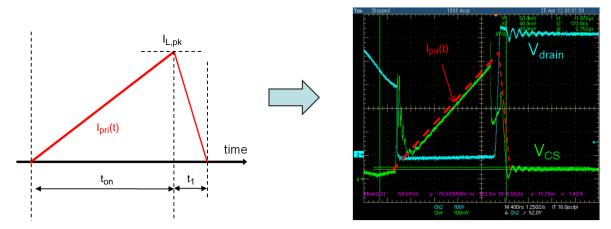

In order to have an accurate regulation of the secondary current, the current-sense voltage shape must be the same as the primary current. Figure 3 portrays the current sense waveform in green for an accurate output current regulation.

Figure 3. Current Sense Voltage Waveform for an Accurate Current Regulation

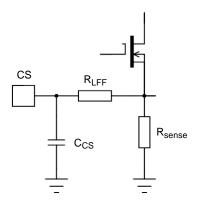

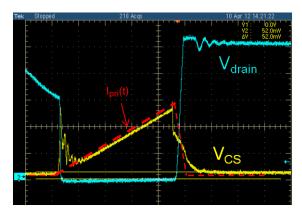

The shape of the current-sense voltage will influence the output current regulation. Indeed, the controller monitors when the current-sense voltage crosses the threshold for leakage inductance reset  $V_{\text{CS(low)}}$  and calculate the output current set-point based on this information. Thus, the shape

of the CS voltage will influence the output current set-point. If the CS pin filter ( $R_{LFF}$ ,  $C_{CS}$ ) is too big, the output current setpoint will vary ( $I_{out}$  higher than expected value). Figure 5 shows the current-sense waveform in such case.

Figure 4. Current-sense Pin

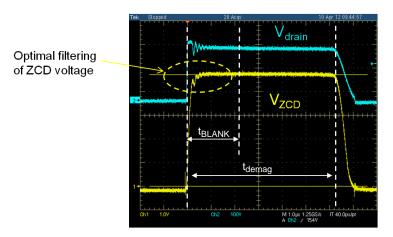

The ZCD pin voltage is used to detect when the secondary current becomes null. It is important to filter the ringing caused by the leakage inductance and the lump capacitor if these oscillations have not decayed when the internal blanking timer  $t_{\rm BLANK}$  has elapsed.

Figure 5. CS Pin Filter Not Optimized: CS Shape Differs from Primary Current Shape

The demagnetization must be longer than  $t_{\rm BLANK}$  for accurate current regulation. If not, the controller will not be able to detect correctly the exact moment when the secondary current becomes null and the current regulation will greatly degrade.

Figure 6. Optimal Filtering of ZCD Pin Voltage

#### **LED Driver Specification**

In order to illustrate the design method that will be described in this document, we consider the following specification for a flyback LED driver:

**Table 2. LED DRIVER SPECIFICATION**

| Description                                  | Symbol                 | Value | Units |

|----------------------------------------------|------------------------|-------|-------|

| LED Driver Specification                     |                        |       |       |

| Minimum Input Voltage                        | $V_{in,min}$           | 85    | V rms |

| Maximum Input Voltage                        | V <sub>in,max</sub>    | 265   | V rms |

| Minimum Output Voltage                       | V <sub>out,min</sub>   | 12    | V     |

| Maximum Output Voltage                       | $V_{out,max}$          | 24    | V     |

| Output Voltage at which the OVP is Activated | V <sub>out(OVP)</sub>  | 28    | V     |

| Output Current (Nominal)                     | l <sub>out</sub>       | 0.5   | А     |

| Output Rectifier Voltage Drop (Estimated)    | V <sub>f</sub>         | 0.6   | V     |

| Input Voltage for Brown-in                   | V <sub>in(start)</sub> | 72    | Vrms  |

| Start-up Time                                | t <sub>startup</sub>   | ≤ 1.5 | S     |

Table 2. LED DRIVER SPECIFICATION (continued)

| Description                              | Symbol              | Value | Units |

|------------------------------------------|---------------------|-------|-------|

| Other Parameters                         |                     |       |       |

| Estimated Efficiency                     | η                   | 85    | %     |

| Estimated Lump Capacitor                 | C <sub>lump</sub>   | 50    | pF    |

| Switching Frequency at Pout,max, Vin,min | F <sub>sw</sub>     | 45    | kHz   |

| Estimated Bulk Voltage Ripple            | V <sub>ripple</sub> | 30    | V     |

#### Sizing the components around the controller

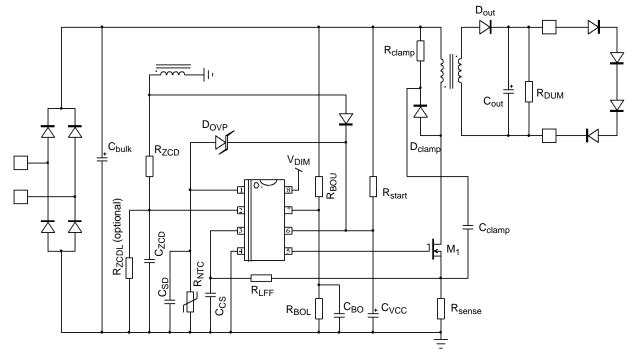

Figure 7. Generic Application Schematic

The  $R_{ZCD}$  resistor limits the current flowing in the ZCD pin. Also, this resistor together with the  $C_{ZCD}$  capacitor delays the zero voltage crossing event and helps to tune the turn-on instant when the drain voltage is in the valley.

To calculate  $R_{ZCD}$ , we must first determine the auxiliary winding voltage value during the on-time and the off-time.

During the on-time, the voltage amplitude will reach its maximum value for the highest input voltage:

$$V_{\text{aux(low)}} = -N_{\text{auxp}}V_{\text{in,max}}\sqrt{2}$$

(eq. 4)

During the off-time, we must consider the maximum output voltage value to calculate the auxiliary winding maximum voltage:

$$V_{aux(high)} = \frac{N_{auxp}}{N_{sp}} (V_{out} + V_f)$$

(eq. 5)

Where:

$N_{auxp}$  is the auxiliary to primary turn ratio:

$$N_{auxp} = N_{aux}/N_p$$

Then, the highest value of the aux winding voltage is used to calculate  $R_{ZCD}$ :

$$R_{ZCD} \ge max \left( \frac{V_{aux(high)}}{I_{ZCD(max+)}}, \frac{V_{aux(low)}}{I_{ZCD(max-)}} \right)$$

(eq. 6)

#### Design Example:

The maximum input voltage is  $V_{in,max} = 265 \text{ V rms}$ .

$$N_{auxp} = 0.17.$$

From the datasheet, we have:  $I_{ZCD(max)} = -2$ , + 5 mA

$$V_{aux(high)} = \frac{N_{auxp}}{N_{sp}} (V_{out,max} + V_f) = \frac{0.17}{0.17} (28 + 0.5) = 28.5 V$$

(eq. 7)

$$V_{aux(low)} = -N_{auxp}V_{in,max}\sqrt{2} = -0.17 \times 265 \times \sqrt{2} =$$

= -63.7V (eq. 8)

$$\begin{split} R_{ZCD} & \geq \text{max} \left( \frac{V_{\text{aux(high)}}}{I_{ZCD(\text{max}+)}}, \frac{V_{\text{aux(low)}}}{I_{ZCD(\text{max}-)}} \right) = \text{max} \left( \frac{28.5}{5\text{m}}, \frac{-63.7}{-2\text{m}} \right) \\ & = \text{max} \left( 5.7\text{k}, 31.8\text{k} \right) = 31.8\,\text{k}\Omega \end{split} \tag{eq. 9}$$

#### Selecting the NTC

There are different ways to select the thermistor depending on the critical parameter for the designer. We will consider the temperature  $T_{TFstart}$  at which the thermal foldback starts and the temperature  $T_{OTP}$  at which the over temperature protection (OTP) must triggers as our design parameters.

The controller starts to reduce the output current when the voltage on SD pin drops below 1 V which correspond to a resistance between SD pin and ground:  $R_{SD} \leq 11.76~k\Omega$ . The current reduction is stopped when  $R_{SD} \leq 8~k\Omega$ : the output current is clamped to 50% of its nominal value. The controllers detects an over temperature and shuts down when  $R_{SD} \leq 5.88~k\Omega$ .

As a starting point, we can try to calculate the sensitivity index or constant B of the material needed to meet our temperature requirements. The formula for B can be found in the thermistor manufacturers' application notes or datasheets. To calculate the B value, it is necessary to know the resistances  $R_1$  and  $R_2$  of the thermistor at the temperatures  $T_1$  and  $T_2$ .

$$B = \frac{T_1 T_2}{T_2 - T_1} \ln \left( \frac{R_1}{R_2} \right)$$

(eq. 10)

In our case, this equation can be translated as follows:

$$B_{x} = \frac{T_{OTP}T_{TFstart}}{T_{OTP}-T_{TFstart}} \ln \left(\frac{R_{TFstart}}{R_{OTP}}\right)$$

(eq. 11)

Where:

*T<sub>TFstart</sub>* is the temperature at which the thermal foldback should start

$R_{TFstart}$  is the corresponding resistance mentioned above:  $R_{TFstart} = 11.76 \text{ k}\Omega$

$T_{OTP}$  is the temperature at which the OTP must trigger  $R_{OTP}$  is the corresponding resistance mentioned above:  $R_{OTP} = 5.88 \text{ k}\Omega$

Generally, the B given by the manufacturer is calculated for  $25^{\circ}$ C and  $85^{\circ}$ C. The value of B depends on the temperatures by which it is calculated. That's why in our case it is an approximate value and we might consider looking for a material within  $\pm 5\%$  of the calculated  $B_x$ .

Then, we can use this  $B_x$  value to approximate the resistance at 25°C of the thermistor needed:

$$R_{25} = \frac{R_{TFstart}}{e^{B_{X}\left(\frac{1}{T_{TFstart}}\frac{1}{25 + 273}\right)}}$$

(eq. 12)

Design Example:

$$T_{TFstart} = 75^{\circ}C = 348 \text{ K}$$

$T_{OTP} = 95^{\circ}C = 368 \text{ K}$

$$B_x = \frac{T_{OTP}T_{TFstart}}{T_{OTP}-T_{TFstart}} \; ln\!\left(\frac{R_{TFstart}}{R_{OTP}}\right) = \frac{348\times368}{368-348} ln\!\left(\frac{11.76k}{5.88k}\right) =$$

$$R_{25} = \frac{R_{TFstart}}{e^{B_X \left(\frac{1}{T_{TFstart}} \frac{1}{25 + 273}\right)}} = \frac{11.76k}{e^{4438 \left(\frac{1}{348} \frac{1}{298}\right)}} = 99.9 \text{ k}\Omega$$

(eq. 14)

Finally, we select a NTC with  $B_{25/85}=4220$  and  $R_{25}=100\ k\Omega.$

From the manufacturer tables of resistance vs temperature R(T), we have the following values:

$R_{75} = 13.16 \text{ k}\Omega$ ,  $R_{80} = 11.06 \text{ k}\Omega$  meaning the temperature foldback point is between 75°C and 80°C.

$R_{95} = 6.74 \text{ k}\Omega$ ,  $R_{100} = 5.76 \text{ k}\Omega$  meaning the OTP trip point is between 95°C and 100°C.

It is also possible to place a resistor in parallel of the NTC to modify its R(T) characteristic.

# Selecting the SD Pin Capacitor

The SD pin capacitor must not exceed **4.7 nF** so that the controller is able to start in every conditions, in particular when  $R_{SD}$  is around 8 k $\Omega$ .

Indeed at startup, the controller waits for 180  $\mu$ s minimum before starting the DRV pulses in order to allow the current source to charge  $C_{SD}$ . If a too big capacitor is used, the SD pin voltage will not be able to increase above 0.5 V before the 180  $\mu$ s timer ends. Thus, the controller will detect an over temperature condition.

# Designing the CS Pin Network (R<sub>LFF</sub>, C<sub>CS</sub>)

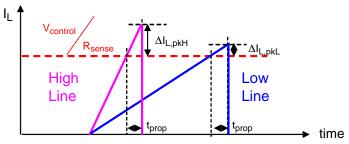

The propagation delay  $t_{prop}$  from the current-sense voltage reaching the programmed internal threshold  $V_{control}$  to the MOSFET off-state influences the output current regulation and must be taken into account. The peak current increase caused by  $t_{prop}$  must be compensated.

Figure 8. Propagation Delay Effect on Peak Current

The propagation delay effect is compensated by applying an offset current proportional to the line voltage on the CS pin during the MOSFET on-time only. The offset current is clamped when  $V_{pinVIN} > 5$  V:  $I_{offset(MAX)} = 76.5 \,\mu\text{A}$  typical.

The offset voltage amount is adjusted by connecting a resistor  $R_{LFF}$  between the CS pin and the sense resistor:

$$V_{CS(offset)} = K_{LFF}V_{pinVIN}R_{LFF}$$

(eq. 15)

As a starting point, the offset resistor value can be estimated with:

$$R_{LFF} = \left(1 + \frac{R_{BOU}}{R_{BOL}}\right) \frac{t_{prop}R_{sense}}{L_{p}K_{LFF}} \tag{eq. 16} \label{eq:RLFF}$$

Where:

$K_{LFF}$  is the voltage to current conversion ratio on VIN pin and can be found in the datasheets of the NCL30080/81/82/83. Its typical value is 17  $\mu$ A/V.

$R_{BOU}$  and  $R_{BOL}$  are the brown-out resistors calculated in the next paragraph.

The parameter t<sub>prop</sub> includes the propagation delay of the controller (50 ns typical from the datasheet) and of the MOSFET gate drive. Thus, it varies with the chosen MOSFET and with the external elements added between the DRV pin and the MOSFET gate (series resistor, PNP transistor, ...). As a consequence, it is difficult to have an exact value for this parameter prior to the LED driver design.

As a first approximation, to calculate  $R_{LFF}$ , start with  $t_{\text{prop}} = 150 \text{ ns.}$

Then, the offset resistor value can be adjusted by experiments to obtain a flat output current.

Using (eq.16), we can calculate the first value of  $R_{LFF}$  for our design:

$$\begin{split} R_{LFF} &= \left(1 + \frac{R_{BOU}}{R_{BOL}}\right) \frac{t_{prop}R_{sense}}{L_{p}K_{LFF}} = \\ &= \left(1 + \frac{9.9 Meg}{100 k}\right) \frac{150 n \times 1.5}{1900 \mu \times 17 \mu} = 696 \ \Omega \end{split}$$

(eq. 17)

After experiments in the lab,  $R_{LFF}$  value was increased to 820  $\Omega$ .

# Selecting the CS Pin Capacitor

The shape of the current-sense voltage influences the output current regulation. If the CS pin filter ( $R_{LFF}$ ,  $C_{CS}$ ) is too big, the output current setpoint will vary ( $I_{out}$  higher than expected value). Thus, once  $R_{LFF}$  has been chosen, it is important to keep the value of  $C_{CS}$  small to have a good regulation of the output current.  $C_{CS}$  should be in the range of 10-100 pF.

#### Selecting the Brown-out Resistors

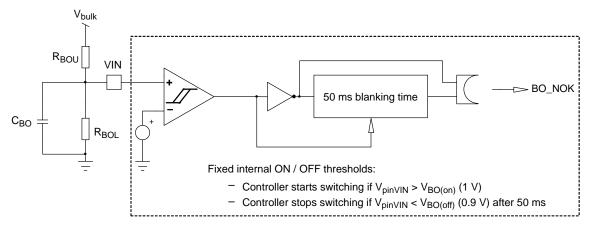

The controller starts switching when  $V_{CC} > V_{CC(on)}$  and when  $V_{pinVIN} > V_{BO(on)}$ .

Figure 9. Brown-out Circuit

First, select a value for  $R_{BOL}$  in the range of  $10~k\Omega$  to  $100~k\Omega$ . In order to decrease the power losses in the resistor network, it is better to choose a resistor in the range of  $62~k\Omega$  to  $100~k\Omega$ .

For our design, we select  $R_{BOL} = 100 \text{ k}\Omega$ .

After that, select the input voltage at which the controller must start switching  $V_{in(start)}$ .

The upper brown-out resistor  $R_{\mbox{\footnotesize{BOU}}}$  value can be calculated with:

$$R_{BOU} = R_{BOL} \left( \frac{V_{in(start)} \sqrt{2}}{V_{BO(on)}} - 1 \right)$$

(eq. 18)

The controller detects a brown-out condition and shuts down when the pin VIN voltage stays below  $V_{BO(off)}$  during 50 ms. Thus, we can deduce the line voltage  $V_{in(stop)}$  at which the controller stops switching:

$$V_{\text{in(stop)}} = \frac{1}{\sqrt{2}} \frac{R_{\text{BOU}} + R_{\text{BOL}}}{R_{\text{BOL}}} V_{\text{BO(off)}}$$

(eq. 19)

**Design Example:**

$$V_{in(start)} = 71 \text{ V rms}$$

$R_{BOL} = 100 \text{ k}\Omega$ .

$$R_{BOU} = R_{BOL} \left( \frac{V_{in(start)} \sqrt{2}}{V_{BO(on)}} - 1 \right) = 100k \left( \frac{71 \sqrt{2}}{1} - 1 \right) =$$

= 9.94 M $\Omega$  (eq. 20)

We choose  $R_{BOU} = 9.9 \text{ M}\Omega$ .

$$\begin{split} V_{\text{in(stop)}} &= \frac{1}{\sqrt{2}} \, \frac{R_{\text{BOU}} + R_{\text{BOL}}}{R_{\text{BOL}}} \, \, V_{\text{BO(off)}} = \\ &= \frac{1}{\sqrt{2}} \, \frac{9.9 M \, + \, 100 k}{100 k} \, \, 0.9 \, = \, 63.6 \, \, \text{Vrms} \end{split} \tag{eq. 21}$$

The controller stops when  $V_{in} < 63.6 \text{ V rms}$ .

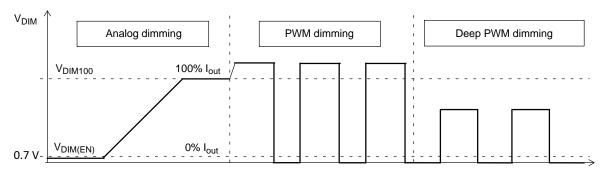

# **Dimming Pin (NCL30082 Only)**

The NCL30082 DIM pin has an enable threshold  $V_{DIM(EN)}$ . In order to start pulsing, the DIM pin voltage must be higher than  $V_{DIM(EN)}$ .

The DIM pin combines analog and PWM dimming capability.

If a signal lower than  $V_{DIM100}$  is applied to this pin, the controller decreases the output current proportionally to the applied voltage. The following equation gives the relationship between the output current and the DIM pin voltage:

$$I_{out}(\%) = \frac{100}{175} V_{DIM} - 0.4$$

(eq. 22)

For normal PWM dimming, apply a signal with a low state value below  $V_{DIM(EN)}$  and high state value above  $V_{DIM100}$ . It is also possible to apply a square signal with a high state value below  $V_{DIM100}$  to further reduce the output current in PWM dimming (Deep PWM dimming in Figure 10).

Figure 10. Analog / PWM Dimming

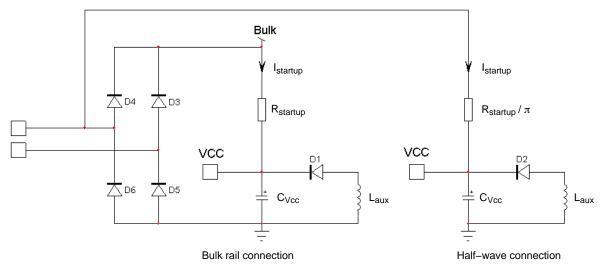

#### STARTUP NETWORK

The NCL3008X consumes a low current during the startup ( $14 \mu A$  typ.,  $30 \mu A$  max.). Thus, depending on the required startup time, high values of startup resistors can be used to reduce the power dissipation in the startup network. However, the device consumes a slightly higher current ( $60 \mu A$  max.) during startup in fault mode, when the 4-s auto-recovery timer is counting. The power supply

# designer must ensure that the startup current noted $I_{\text{startup}}$ on Figure 11 is always above 60 $\mu A$ .

The startup resistor  $R_{startup}$  can either be connected to the bulk rail or to half-wave (Figure 11). Connecting the startup resistor to the half-wave allows decreasing the power dissipated in the startup resistor.

Figure 11. The Startup Resistor can be Connected to the Bulk Rail or to the Half Wave

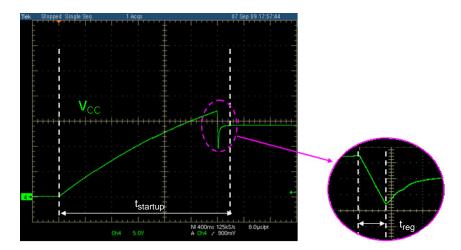

#### **Calculating the Startup Capacitor**

The startup capacitor is calculated to allow the power supply to close the loop before  $V_{CC}$  falls below  $V_{CC(off)}$ . Thus,  $C_{Vcc}$  must be able to supply the controller alone until the auxiliary winding voltage  $V_{aux}$  is high enough to supply the controller. The time duration where the controller is supplied by  $C_{Vcc}$  alone is noted  $t_{reg}$  (Figure 12).

At startup, almost no current will flow through the LED string until the output voltage exceeds the forward threshold

of the LED string. Thus, we can consider that all the current charges the output capacitor. We can then roughly estimate the time  $t_{\text{reg}}$ :

$$t_{\text{reg}} = \frac{C_{\text{out}}}{I_{\text{out}}} (V_{\text{out1}} + V_{\text{f}}) \frac{N_{\text{auxp}}}{N_{\text{sp}}}$$

(eq. 23)

Where:

$V_{out1}$  is the corresponding output voltage at which the auxiliary winding should start to supply the controller

Figure 12. V<sub>CC</sub> Waveform during Startup

The startup capacitor value can be calculated as follows:

$$C_{\text{Vcc}} \ge \frac{(I_{\text{CC2}} + Q_g F_{\text{sw}})t_{\text{reg}}}{V_{\text{CC(on),min}} - V_{\text{CC(off),max}}}$$

(eq. 24)

The current needed to charge  $C_{Vcc}$  alone during the startup is:

$$I_{C_{Vcc}} = \frac{V_{CC(on),max}C_{Vcc}}{t_{startup}}$$

(eq. 25)

#### Design Example:

Four our 10 W LED driver, we chose a 3-A, 800-V MOSFET (STP3NK80 from ST Microelectronics).

The total gate charge is:  $Q_g = 19 \text{ nC}$

The switching frequency at low line, maximum output load is:  $F_{sw} = 55 \text{ kHz}$ .

The total startup time of the LED driver must be below 1.5 second at  $V_{in} = 90$  V rms.

We choose:  $V_{out1} = 15 \text{ V}$

From the datasheet, we can extract the values of the following parameters:

$$I_{CC2} = 2.1 \text{ mA}$$

$V_{CC(on),min} = 16 \text{ V}$

$V_{CC(on),max} = 20 \text{ V}$

$V_{CC(off),max} = 9.4 \text{ V}$

We can deduce:

$$\begin{split} t_{\text{reg}} &= \frac{C_{\text{out}}}{I_{\text{out}}} (V_{\text{out1}} + V_{\text{f}}) \frac{N_{\text{auxp}}}{N_{\text{sp}}} = \\ &= \frac{120 \times 10^{-6}}{0.470} \, (15 + 0.6) \frac{0.17}{0.17} \approx 4 \, \text{ms} \end{split} \tag{eq. 26}$$

$$\begin{split} C_{Vcc} &= \frac{(I_{CC2} + Q_g F_{sw}) t_{reg}}{V_{CC(on),min} - V_{CC(off),max}} = \\ &= \frac{(2.1m + 19n \times 55k) \times 4m}{16 - 9.4} = 1.91 \ \mu F \end{split} \tag{eq. 27}$$

We could choose a 2.2  $\mu F$  capacitor for  $C_{VCC}$  but we must also consider the step dimming case of the NCL30083 where the output current is decreased by discrete steps each time a brown-out condition is detected. Thus, we select a 4.7  $\mu F$  capacitor.

The current needed to charge C<sub>Vcc</sub> is:

$$I_{C_{Vcc}} = \frac{V_{CC(on),max}C_{Vcc}}{t_{startup}} = \frac{20 \times 4.7 \mu}{1.5} \approx 63 \ \mu A \qquad \text{(eq. 28)}$$

# **Startup Resistor Calculation**

#### • Bulk Connection:

If the resistor is connected to the bulk rail, the following formula can be used to calculate its value:

$$R_{\text{startup}} = \frac{V_{\text{in,min}} \sqrt{2}}{I_{\text{Cvcc}} + I_{\text{CC(start)}}}$$

(eq. 29)

Where:

$I_{Cvcc}$  is the current needed to charge the VCC pin capacitor  $I_{CC(start)}$  is the current consumed by the controller during startup

$V_{in,min}$  is the minimum input voltage

The maximum power dissipated by the startup resistor connected to the bulk rail is:

$$P_{\text{startup}} = \frac{\left(V_{\text{in,max}}\sqrt{2} - V_{\text{CC}}\right)^2}{R_{\text{startup}}}$$

(eq. 30)

# • Half-wave Connection:

If the resistor is connected to the half-wave:

$$R_{\text{startup1/2}} = \frac{\frac{V_{\text{in,min}}\sqrt{2}}{\pi}}{I_{\text{Cvcc}} + I_{\text{CC(start)}}} = \frac{R_{\text{startup}}}{\pi} \quad \text{(eq. 31)}$$

The maximum power dissipated by the startup resistor connected to the half-wave is thus:

$$P_{\text{startup1/2}} = \frac{\left(\frac{V_{\text{in,max}}\sqrt{2}}{\pi} - V_{\text{CC}}\right)^2}{R_{\text{startup1/2}}}$$

(eq. 32)

#### Design Example:

From the datasheet, the typical value of  $I_{CC(start)}$  is 14  $\mu A$ . We deduce:

$$R_{\text{startup}} = \frac{V_{\text{in,min}} \sqrt{2}}{I_{\text{Cvcc}} + I_{\text{CC(start),max}}} = \frac{85\sqrt{2}}{63\mu + 14\mu} = 1.56 \text{ M}\Omega$$

(eq. 33)

$$\mathsf{R}_{\text{startup1/2}} = \frac{\frac{\mathsf{V}_{\text{in,min}}\sqrt{2}}{\pi}}{\mathsf{I}_{\text{Cvcc}} + \mathsf{I}_{\text{CC(start)}}} = \frac{\frac{85\sqrt{2}}{\pi}}{63\mu + 14\mu} \approx 497 \text{ k}\Omega \tag{eq. 34}$$

The power dissipated for each resistor at maximum input voltage is:

$$P_{\text{startup}} = \frac{\left(V_{\text{in,max}} \sqrt{2} - V_{\text{CC}}\right)^2}{R_{\text{startup}}} = \frac{\left(265 \sqrt{2} - 20\right)^2}{1.56 \times 10^6} = 81 \,\text{mW}$$

(eq. 35)

$$\mathsf{P}_{\mathsf{startup1/2}} = \frac{\left(\frac{\mathsf{V}_{\mathsf{in,max}}\sqrt{2}}{\pi} - \mathsf{V}_{\mathsf{CC}}\right)^2}{\mathsf{R}_{\mathsf{startup1/2}}} = \frac{\left(\frac{265\sqrt{2}}{\pi} - 20\right)^2}{497\mathsf{k}} = 20\,\mathsf{mW}$$

(eq. 36)

Connecting the startup resistor to the half-wave allows saving 60 mW! Thus, we choose this approach for our LED driver design.

#### FLYBACK TRANSFORMER DESIGN

The transformer is an important part of the power supply design as it will influence the choice of the MOSFET, the output rectifier and the RCD clamp network. The transformer design is a compromise between performance and cost of the solution. For example, allowing higher drain-source voltage excursion will imply to use a MOSFET with a larger breakdown voltage, but it will allow using an output rectifier with a smaller breakdown voltage. It will also decrease the power losses in the RCD clamp as we will be able to use higher clamping resistor value (provided that the leakage inductance of the transformer is kept under control). Reflecting more output voltage will also decrease the maximum necessary primary peak current, but it will increase the secondary peak current.

#### **Turn Ratio Calculation**

The constant current algorithm implemented in the NCL3008X provides a better regulation of the output current if the duty-cycle of the MOSFET is equal or above 50%. The duty-cycle of a quasi-square wave resonant flyback converter operated in the 1<sup>st</sup> valley can be calculated with:

$$D = \frac{V_{out} + V_f}{N_{sp}V_{in} + V_{out} + V_f}$$

(eq. 37)

The duty-cycle varies with the output load and the input voltage. In reality, we cannot have D > 0.5 for all input voltage/output loading conditions. Thus, we will design the transformer in order to have a duty cycle greater than 50% at a chosen operating point, for example maximum output load and minimum input voltage.

$$N_{sp} < \frac{\frac{V_{out,max} + V_f}{0.5} - (V_{out,max} + V_f)}{V_{in min} \sqrt{2}}$$

(eq. 38)

For our LED driver, we decide to have a duty-cycle around 55% at  $V_{out,max}$  and  $V_{in,min}$ :

$$\begin{split} N_{sp} &= \frac{\frac{V_{out,max} + V_f}{0.55} - (V_{out,max} + V_f)}{V_{in,min}} = \frac{\frac{24 + 0.6}{0.55} - (24 + 0.6)}{85\sqrt{2}} \Rightarrow \\ &\Rightarrow N_{sp} = 0.167 \end{aligned}$$

(eq. 39)

#### **Maximum Primary Peak Current and Inductance**

The peak current is highest at minimum input voltage and maximum output load  $P_{out,max}$ . By selecting a switching

frequency for this operating point  $F_{sw,min}$ , we can calculate the maximum peak current and the primary inductance value:

$$\begin{split} I_{L,pk} &= 2 \frac{P_{out,max}}{\eta} \Biggl( \frac{1}{V_{in,min} \sqrt{2} - V_{ripple}} + \frac{N_{sp}}{V_{out(OVP)} + V_f} \Biggr) + \\ &+ \pi \sqrt{\frac{2P_{out,max}C_{lump}F_{sw,min}}{\eta}} \\ L_p &= \frac{2P_{out,max}}{I_{L,pk}} \frac{2P_{out,max}}{F_{sw,min} \eta} \end{split} \tag{eq. 41}$$

Where:

$V_{ripple}$  is the bulk voltage ripple

$C_{lump}$  is the total capacitor at the drain node of the MOFSET. For a first approximation, we can use  $C_{OSS}$  value.

$V_{out(OVP)}$  is the output voltage at which the over voltage protection must triggers

$\eta$  is the estimated efficiency of the power supply

Using equations (40) and (41), we can calculate the maximum peak current and the primary inductance of the flyback transformer:

$$\begin{split} I_{L,pk} &= 2 \frac{P_{out,max}}{\eta} \Biggl( \frac{1}{V_{in,min}\sqrt{2} - V_{ripple}} + \frac{N_{sp}}{V_{out(OVP)} + V_f} \Biggr) + \\ &+ \pi \sqrt{\frac{2P_{out,max}C_{lump}F_{sw,min}}{\eta}} = \\ &= 2 \frac{28 \times 0.5}{0.85} \Biggl( \frac{1}{85\sqrt{2} - 30} + \frac{0.167}{28 + 0.6} \Biggr) + \\ &+ \pi \sqrt{\frac{2 \times 28 \times 0.5 \times 50p \times 50k}{0.85}} \Rightarrow I_{L,pk} = 0.59\,A \\ &+ \mu \sqrt{\frac{2 \times 28 \times 0.5 \times 50p \times 50k}{0.85}} \Longrightarrow I_{L,pk} = 0.59\,A \\ &+ \mu \sqrt{\frac{2 \times 28 \times 0.5 \times 50p \times 50k}{0.85}} \Longrightarrow I_{L,pk} = 0.59\,A \\ &+ \mu \sqrt{\frac{2 \times 28 \times 0.5 \times 50p \times 50k}{0.85}} \Longrightarrow I_{L,pk} = 0.59\,A \\ &+ \mu \sqrt{\frac{2 \times 28 \times 0.5 \times 50p \times 50k}{0.85}} \Longrightarrow I_{L,pk} = 0.59\,A \\ &+ \mu \sqrt{\frac{2 \times 28 \times 0.5 \times 50p \times 50k}{0.85}} \Longrightarrow I_{L,pk} = 0.59\,A \\ &+ \mu \sqrt{\frac{2 \times 28 \times 0.5 \times 50p \times 50k}{0.85}} \Longrightarrow I_{L,pk} = 0.59\,A \\ &+ \mu \sqrt{\frac{2 \times 28 \times 0.5 \times 50p \times 50k}{0.85}} \Longrightarrow I_{L,pk} = 0.59\,A \\ &+ \mu \sqrt{\frac{2 \times 28 \times 0.5 \times 50p \times 50k}{0.85}} \Longrightarrow I_{L,pk} = 0.59\,A \\ &+ \mu \sqrt{\frac{2 \times 28 \times 0.5 \times 50p \times 50k}{0.85}} \Longrightarrow I_{L,pk} = 0.59\,A \\ &+ \mu \sqrt{\frac{2 \times 28 \times 0.5 \times 50p \times 50k}{0.85}} \Longrightarrow I_{L,pk} = 0.59\,A \\ &+ \mu \sqrt{\frac{2 \times 28 \times 0.5 \times 50p \times 50k}{0.85}} \Longrightarrow I_{L,pk} = 0.59\,A \\ &+ \mu \sqrt{\frac{2 \times 28 \times 0.5 \times 50p \times 50k}{0.85}} \Longrightarrow I_{L,pk} = 0.59\,A \\ &+ \mu \sqrt{\frac{2 \times 28 \times 0.5 \times 50p \times 50k}{0.85}} \Longrightarrow I_{L,pk} = 0.59\,A \\ &+ \mu \sqrt{\frac{2 \times 28 \times 0.5 \times 50p \times 50k}{0.85}} \Longrightarrow I_{L,pk} = 0.59\,A \\ &+ \mu \sqrt{\frac{2 \times 28 \times 0.5 \times 50p \times 50k}{0.85}} \Longrightarrow I_{L,pk} = 0.59\,A \\ &+ \mu \sqrt{\frac{2 \times 28 \times 0.5}{0.59^2 \times 50k \times 0.84}} \Longrightarrow I_{L,pk} = 0.59\,A \\ &+ \mu \sqrt{\frac{2 \times 28 \times 0.5}{0.59^2 \times 50k \times 0.84}} \Longrightarrow I_{L,pk} = 0.59\,A \\ &+ \mu \sqrt{\frac{2 \times 28 \times 0.5}{0.59^2 \times 50k \times 0.84}} \Longrightarrow I_{L,pk} = 0.59\,A \\ &+ \mu \sqrt{\frac{2 \times 28 \times 0.5}{0.59^2 \times 50k \times 0.84}} \Longrightarrow I_{L,pk} = 0.59\,A \\ &+ \mu \sqrt{\frac{2 \times 28 \times 0.5}{0.59^2 \times 50k \times 0.84}} \Longrightarrow I_{L,pk} = 0.59\,A \\ &+ \mu \sqrt{\frac{2 \times 28 \times 0.5}{0.59^2 \times 50k \times 0.84}} \Longrightarrow I_{L,pk} = 0.59\,A \\ &+ \mu \sqrt{\frac{2 \times 28 \times 0.5}{0.59^2 \times 50k \times 0.84}} \Longrightarrow I_{L,pk} = 0.59\,A \\ &+ \mu \sqrt{\frac{2 \times 28 \times 0.5}{0.59^2 \times 50k \times 0.84}} \Longrightarrow I_{L,pk} = 0.59\,A \\ &+ \mu \sqrt{\frac{2 \times 28 \times 0.5}{0.59^2 \times 50k \times 0.84}} \Longrightarrow I_{L,pk} = 0.59\,A \\ &+ \mu \sqrt{\frac{2 \times 28 \times 0.5}{0.59^2 \times 50k \times 0.84}} \Longrightarrow I_{L,pk} = 0.59\,A \\ &+ \mu \sqrt{\frac{2 \times 28 \times 0.5}{0.59^2 \times 50k \times 0.84}} \Longrightarrow I_{L,pk} = 0.59\,A \\ &+ \mu \sqrt{\frac{2 \times 28 \times 0.5}{0.59^2 \times 50k \times 0.84}} \Longrightarrow I_{L,$$

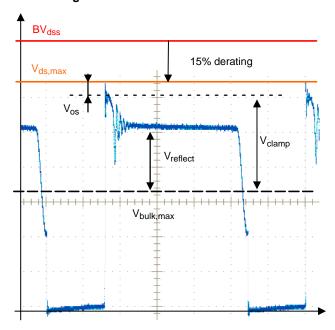

#### **Choosing the MOSFET Breakdown Voltage**

Figure 13. MOSFET Drain-source Voltage at High Line

Figure 13 shows the waveform of the drain-source voltage of a MOSFET operated in the 1<sup>st</sup> valley.

We can estimate the maximum voltage reached on the drain node, considering  $V_{out(OVP)}$  level as the maximum output voltage:

$$V_{ds,max} = V_{in,max} \sqrt{2} + \frac{(V_{out(OVP)} + V_f)}{N_{sp}} k_c + V_{os}$$

(eq. 44)

Where:

$k_c$  is the clamping coefficient ( $k_c = V_{clamp} / V_{reflect}$ ) [1].  $k_c$  should be keep in the range of 1.3 to 1.5 times the reflected voltage.

$V_{os}$  is the drain voltage overshoot caused by the clamping diode recovery time.

After calculating the maximum drain-source voltage, we apply a safety factor of 15% in order to select the breakdown voltage of the MOSFET, meaning that:

$$B_{Vdss} \ge \frac{V_{ds,max}}{(1 - 0.15)}$$

(eq. 45)

The following table gives the maximum drain-source voltage considering a 15% derating factor for MOSFET breakdown voltage found on the market.

Table 3.  $V_{ds,max}$  AFTER 15% DERATING HAS BEEN APPLIED TO  $\mathrm{BV}_{dss}$

| Breakdown Voltage<br>(BV <sub>dss</sub> ) | Maximum drain-source<br>voltage (V <sub>ds,max</sub> ) |

|-------------------------------------------|--------------------------------------------------------|

| 500 V                                     | 425 V                                                  |

| 600 V                                     | 510 V                                                  |

| 650 V                                     | 553 V                                                  |

| 800 V                                     | 680 V                                                  |

Using (eq.44), we calculate the MOSFET  $V_{ds,max}$  in our design:

$$V_{ds,max} = V_{in,max}\sqrt{2} + \frac{(V_{out(OVP)} + V_f)}{N_{sp}}k_c + V_{os} =$$

$$= 265\sqrt{2} + \frac{(28 + 0.6)}{0.167}1.6 + 20 = 668 V$$

(eq. 46)

Looking at Table 3, we select an 800 V MOSFET.

# Choosing the MOSFET R<sub>DSon</sub>

Space is very limited in a LED bulb, and there is no space to add a heatsink for the power MOSET or the output rectifier. Thus, the MOSFET will be chosen such that it can dissipate the power in all conditions without using a heatsink.

Knowing the chosen package thermal resistance  $R_{qJA}$ , we first calculate the power that can be dissipated by this package at a chosen maximum ambient temperature  $T_{A(MAX)}$ .

$$P_{pack} = \frac{T_{J(MAX)} - T_{A(MAX)}}{R_{AJ\Delta}}$$

(eq. 47)

In a quasi-square wave resonant power supply operating at low line and full load, the MOSFET losses are mainly conduction losses. The MOSFET  $R_{DSon}$  at  $T_{J(MAX)}$  can be estimated:

$$R_{DSon(T_J)} = \frac{P_{pack}}{I_{pri,rms}^2}$$

(eq. 48)

In equation (48), I<sub>pri,rms</sub> is the rms current in the primary side of the flyback transformer at lowest input voltage and full output load:

$$I_{pri,rms} = I_{L,pk} \sqrt{\frac{1}{3} \left( \frac{I_{L,pk} L_p F_{sw,min}}{V_{in,min} \sqrt{2} - V_{ripple}} \right)} \quad (eq. 49)$$

We choose a TO-220FP isolated package for the MOSFET. From the manufacturer datasheet, we have:  $R_{\theta JA} = 62.5^{\circ}\text{C/W}$ . We consider a maximum junction temperature of 125°C for this device. The maximum ambient temperature is 80°C.

$$P_{pack} = \frac{T_{J(MAX)} - T_{A(MAX)}}{R_{\theta JA}} = \frac{125 - 80}{62.5} = 0.72 \text{ W} \quad \text{(eq. 50)}$$

The primary peak current and the primary inductance have been calculated in (42) and (43). We can deduce the primary rms current value:

$$\begin{split} I_{pri,rms} &= \ I_{L,pk} \ \sqrt{\frac{1}{3} \left( \frac{I_{L,pk} \ L_p \ F_{sw,min}}{V_{in,min} \sqrt{2} - V_{ripple}} \right)} = \\ &= 0.62 \ \sqrt{\frac{1}{3} \left( \frac{0.59 \times 1900 \mu \times 50 k}{82 \sqrt{2} - 30} \right)} = 0.268 \ A \end{split}$$

We deduce the  $R_{DSon}$  value at  $T_J = 125$ °C:

$$R_{DSon(125^{\circ}C)} = \frac{P_{pack}}{I_{pri,rms}^{2}} = \frac{0.72}{0.268^{2}} = 10\Omega \quad (eq. 52)$$

The MOSFET manufacturers generally specify the  $R_{DSon}$  at 25°C.

The  $R_{DSon}$  value at 25°C is roughly half the value at  $T_J=125$ °C, so we will choose a MOSFET with a  $R_{DSon(25$ °C)}  $\leq$  5  $\Omega$ .

#### **Selecting the Output Diode**

In order to select the output diode, it is important to consider also the losses caused by the secondary rms current which interact with the diode dynamic resistance  $r_d$ :

$$P_{diode} = V_f I_{out} + r_d I_{sec,rms}^2$$

(eq. 53)

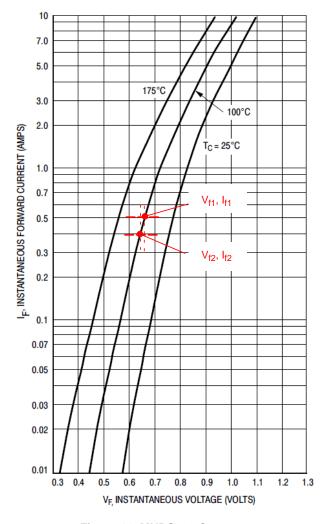

The diode dynamic resistance can be extracted from the I-V curves drawn in the datasheet of the diode or measured.

Figure 14. MURS220 Curves

Look at the forward voltage drop at  $I_{f1} = I_{out}$ , then choose an operating point slightly below the previous one and note  $V_{f2}$ ,  $I_{f2}$ . From these values, you can calculate the dynamic resistance:

$$r_{d} = \frac{V_{f1} - V_{f2}}{I_{f1} - I_{f2}}$$

(eq. 54)

We choose a MURS220 diode in SMB package. We extract its dynamic resistance from the curves in Figure 14:  $r_d = 167 \ m\Omega$ .

The rms value of the current circulating in the secondary side of the transformer is:

$$\begin{split} I_{\text{sec,rms}} &= \frac{I_{\text{L,pk}}}{N_{\text{sp}}} \sqrt{\frac{1}{3} \left( 1 - \frac{I_{\text{L,pk}} \, L_{\text{p}} \, F_{\text{sw,min}}}{V_{\text{in,min}} \sqrt{2} - V_{\text{ripple}}} \right)} = \\ &= \frac{0.59}{0.167} \sqrt{\frac{1}{3} \left( 1 - \frac{0.59 \times 1900 \mu \times 50 k}{82 \sqrt{2} - 30} \right)} = 1.25 \, \text{A} \end{split}$$

The forward voltage drop of the MURS220 diode at  $I_{out} = 0.5$  A and  $T_J = 100^{\circ}$ C is 0.65 V (Figure 14). We can deduce the power dissipated by the diode:

$$P_{diode} = V_f I_{out} + r_d I_{sec,rms}^2 =$$

(eq. 56)

=  $0.65 \times 0.5 + 0.167 \times 1.25^2 = 0.59 W$

When selecting the output diode, the power supply designer must ensure that the diode package is able to dissipate the calculated power:  $P_{\text{pack}} > P_{\text{diode}}$ .

Considering a thermal resistance  $R_{\theta JA} = 100^{\circ}\text{C/W}$  for the SMB package and a maximum junction temperature of 150°C for the diode, we calculate the power dissipation of the package using (eq. 47):

$$P_{pack} = \frac{T_{J(MAX)} - T_{A(MAX)}}{R_{\theta JA}} = \frac{150 - 80}{100} = 0.7 \text{ W} \quad (eq. 57)$$

Since the worst case power losses in the output diode is 0.59 W and the package can dissipate 0.7 W at an ambient temperature of 80°C, we can consider our design safe.

#### Conclusion

This application note provides the key equations and design criteria to dimension a primary-side constant current flyback converter operated by the NCL30080/81/82/83. The design method is illustrated by an implementation of a 12 W, wide mains LED driver. Table 4 summarizes the equations useful to select the components around the NCL3008X controllers. For detailed information on the performance of the 10 W LED driver designed in this document, you can refer to AND9132/D [2].

**Table 4. GENERAL EQUATIONS SUMMARY**

| ZCD Pin         | ZCD Pin Resistor                                         | $R_{ZCD} \ge \max\left(\frac{V_{aux(high)}}{5m}, \frac{V_{aux(low)}}{2m}\right)$                                               |

|-----------------|----------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------|

| SD Pin          | NTC B <sub>x</sub> Coefficient and Resistance<br>at 25°C | $B_{x} = \frac{T_{OTP}T_{TFstart}}{T_{OTP} - T_{TFstart}} \ln\left(\frac{11.76k}{5.88k}\right)$                                |

|                 |                                                          | $R_{25} = \frac{11.76k}{e^{B_X \left(\frac{1}{T_{TFstart}} \frac{1}{25 + 273}\right)}}$                                        |

|                 | SD Pin Capacitor                                         | $C_{SD} \leq 4.7 \text{ nF}$                                                                                                   |

| CS Pin          | LFF Resistor                                             | $R_{LFF} = \left(1 + \frac{R_{BOU}}{R_{BOL}}\right) \frac{t_{prop}R_{sense}}{L_p 17\mu}$                                       |

|                 | CS Pin Capacitor                                         | 10 – 100 pF                                                                                                                    |

| VIN Pin         | Lower Resistor                                           | 10 – 100 kΩ                                                                                                                    |

|                 | Upper Resistor                                           | $R_{BOU} = R_{BOL} \left( \frac{V_{in(start)} \sqrt{2}}{V_{BO(on)}} - 1 \right)$                                               |

| DIM Pin         | Output Current Variation with DIM<br>Pin Voltage         | $I_{out}(\%) = \frac{100}{175} V_{DIM} - 0.4$                                                                                  |

| Startup Network | V <sub>CC</sub> Capacitor                                | $C_{\text{Vcc}} \ge \frac{(I_{\text{CC2}} + Q_g F_{\text{sw}})t_{\text{reg}}}{V_{\text{CC(on),min}} - V_{\text{CC(off),max}}}$ |

|                 | Startup Resistor                                         | $R_{\text{startup}} = \frac{V_{\text{in,min}} \sqrt{2}}{I_{\text{Cvcc}} + 14\mu}$                                              |

|                 |                                                          | (Bulk connection)                                                                                                              |

|                 |                                                          | $R_{startup}/\pi$ (Half-wave connection)                                                                                       |

|                 | Startup Current                                          | $I_{start} \ge 60 \mu\text{A}!$                                                                                                |

Table 4. GENERAL EQUATIONS SUMMARY (continued)

| Sense Resistor     | Set the Output Current Value   | $R_{\text{sense}} = \frac{0.25}{2N_{\text{sp}} I_{\text{out}}}$                                                                                                                                          |

|--------------------|--------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Transformer Design | Turn-ratio                     | $N_{sp} < \frac{\frac{V_{out,max} + V_f}{0.5} - (V_{out,max} + V_f)}{V_{in,min}\sqrt{2}}$                                                                                                                |

|                    | Maximum Primary Peak Current   | $I_{L,pk} = 2 \frac{P_{out,max}}{\eta} \left( \frac{1}{V_{in,min} \sqrt{2} - V_{ripple}} + \frac{N_{sp}}{V_{out(OVP)} + V_f} \right) +$                                                                  |

|                    |                                | $+ \pi \sqrt{\frac{2P_{out,max}C_{lump}F_{sw,min}}{\eta}}$                                                                                                                                               |

|                    | Primary Inductance             | $L_{p} = \frac{2P_{out,max}}{I_{L,pk}^{2} F_{sw,min} \eta}$                                                                                                                                              |

| MOSFET Selection   | Breakdown Voltage              | $B_{Vdss} \ge \frac{V_{ds,max}}{(1 - 0.15)}$                                                                                                                                                             |

|                    |                                | $V_{ds,max} = V_{in,max}\sqrt{2} + \frac{(V_{out(OVP)} + V_f)}{N_{sp}}k_c + V_{os}$                                                                                                                      |

|                    | $R_{DS(on)}$ at $T_J = 125$ °C | $R_{DSon(125^{\circ}C)} = \frac{P_{pack}}{I_{pri,rms}}$                                                                                                                                                  |

|                    |                                | $I_{pri,rms} = I_{L,pk} \sqrt{\frac{1}{3} \left( \frac{I_{L,pk} L_p F_{sw,min}}{V_{in,min} \sqrt{2} - V_{ripple}} \right)}$                                                                              |

|                    |                                | $P_{pack} = \frac{125 - T_{A(MAX)}}{R_{\thetaJA}}$                                                                                                                                                       |

| Output Diode       | Diode Losses                   | $P_{diode} = V_f I_{out} + r_d I_{sec,rms}^2$                                                                                                                                                            |

|                    |                                | $I_{\text{sec,rms}} = \frac{I_{\text{L,pk}}}{N_{\text{sp}}} \sqrt{\frac{1}{3} \left(1 - \frac{I_{\text{L,pk}}  L_{\text{p}}  F_{\text{sw,min}}}{V_{\text{in,min}} \sqrt{2} - V_{\text{ripple}}}\right)}$ |

#### **REFERENCES**

- [1] Christophe Basso, "Switch-mode Power Supplies", McGraw-Hill, 2008.

- [2] Stephanie Cannenterre, "Performance of a 10 W LED driver controlled by the NCL30080-81-82-83", AND9132/D

ON Semiconductor and the are registered trademarks of Semiconductor Components Industries, LLC (SCILLC) or its subsidiaries in the United States and/or other countries. SCILLC owns the rights to a number of patents, trademarks, copyrights, trade secrets, and other intellectual property. A listing of SCILLC's product/patent coverage may be accessed at www.onsemi.com/site/pdf/Patent-Marking.pdf. SCILLC reserves the right to make changes without further notice to any products herein. SCILLC makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does SCILLC assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. "Typical" parameters which may be provided in SCILLC data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. SCILLC does not convey any license under its patent rights nor the rights of others. SCILLC products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the SCILLC product could create a situation where personal injury or death may occur. Should Buyer purchase or use SCILLC products for any such unintended or unauthorized application, Buyer shall indemnify and hold SCILLC and its officers, employees, subsidiaries, affliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that SCILLC was negligent regarding t

#### **PUBLICATION ORDERING INFORMATION**

#### LITERATURE FULFILLMENT:

Literature Distribution Center for ON Semiconductor P.O. Box 5163, Denver, Colorado 80217 USA Phone: 303–675–2175 or 800–344–3860 Toll Free USA/Canada Fax: 303–675–2176 or 800–344–3867 Toll Free USA/Canada Email: orderlit@onsemi.com

N. American Technical Support: 800–282–9855 Toll Free USA/Canada Europe, Middle East and Africa Technical Support:

Europe, Middle East and Africa Technical Support: Phone: 421 33 790 2910 Japan Customer Focus Center Phone: 81–3–5817–1050 ON Semiconductor Website: www.onsemi.com

Order Literature: http://www.onsemi.com/orderlit

For additional information, please contact your local Sales Representative