|                                                              |                                    |        |             |                   |       |                                              |                  |                         |                       |      |        | I                        | REVIS                             | SIONS                     |                                                 |                                               |                                               |                                |                                |             |        |   |

|--------------------------------------------------------------|------------------------------------|--------|-------------|-------------------|-------|----------------------------------------------|------------------|-------------------------|-----------------------|------|--------|--------------------------|-----------------------------------|---------------------------|-------------------------------------------------|-----------------------------------------------|-----------------------------------------------|--------------------------------|--------------------------------|-------------|--------|---|

|                                                              |                                    |        |             |                   | LT    | R                                            |                  |                         |                       | DESC | RIPTIC | ON                       |                                   |                           |                                                 | D                                             | ATE                                           |                                | ļ                              | PPR         | OVED   | ) |

|                                                              |                                    |        |             |                   |       |                                              |                  |                         |                       |      |        |                          |                                   |                           |                                                 |                                               |                                               |                                |                                |             |        |   |

|                                                              |                                    |        |             |                   |       |                                              |                  |                         |                       |      |        |                          |                                   |                           |                                                 |                                               |                                               |                                |                                |             |        |   |

|                                                              |                                    |        |             |                   |       |                                              |                  |                         |                       |      |        |                          |                                   |                           |                                                 |                                               |                                               |                                |                                |             |        |   |

|                                                              |                                    |        |             |                   |       |                                              |                  |                         |                       |      |        |                          |                                   |                           |                                                 |                                               |                                               |                                |                                |             |        |   |

|                                                              |                                    |        |             |                   |       |                                              |                  |                         |                       |      |        |                          |                                   |                           |                                                 |                                               |                                               |                                |                                |             |        |   |

|                                                              |                                    |        |             |                   |       |                                              |                  |                         |                       |      |        |                          |                                   |                           |                                                 |                                               |                                               |                                |                                |             |        |   |

|                                                              |                                    |        |             |                   |       |                                              |                  |                         |                       |      |        |                          |                                   |                           |                                                 |                                               |                                               |                                |                                |             |        |   |

|                                                              |                                    |        |             |                   |       |                                              |                  |                         |                       |      |        |                          |                                   |                           |                                                 |                                               |                                               |                                |                                |             |        |   |

|                                                              |                                    |        |             |                   |       |                                              |                  |                         |                       |      |        |                          |                                   |                           |                                                 |                                               |                                               |                                |                                |             |        |   |

|                                                              |                                    |        |             |                   |       |                                              |                  |                         |                       |      |        |                          |                                   |                           |                                                 |                                               |                                               |                                |                                |             |        |   |

|                                                              |                                    |        |             |                   |       |                                              |                  |                         |                       |      |        |                          |                                   |                           |                                                 |                                               |                                               |                                |                                |             |        |   |

|                                                              |                                    |        |             |                   |       |                                              |                  |                         |                       |      |        |                          |                                   |                           |                                                 |                                               |                                               |                                |                                |             |        |   |

|                                                              |                                    |        |             |                   |       |                                              |                  |                         |                       |      |        |                          |                                   |                           |                                                 |                                               |                                               |                                |                                |             |        |   |

|                                                              |                                    |        |             |                   |       |                                              |                  |                         |                       |      |        |                          |                                   |                           |                                                 |                                               |                                               |                                |                                |             |        |   |

|                                                              |                                    |        |             |                   |       |                                              |                  |                         |                       |      |        |                          |                                   |                           |                                                 |                                               |                                               |                                |                                |             |        |   |

|                                                              |                                    |        |             |                   |       |                                              |                  |                         |                       |      |        |                          |                                   |                           |                                                 |                                               |                                               |                                |                                |             |        |   |

|                                                              |                                    |        |             |                   |       |                                              |                  |                         |                       |      |        |                          |                                   |                           |                                                 |                                               |                                               |                                |                                |             |        |   |

|                                                              |                                    |        |             |                   |       |                                              |                  |                         |                       |      |        |                          |                                   |                           |                                                 |                                               |                                               |                                |                                |             |        |   |

| Prepared                                                     | l in acc                           | cordan | ce with     | ASM               | E Y14 | 1.24                                         |                  |                         |                       |      |        |                          |                                   |                           |                                                 |                                               |                                               | Ve                             | ndor it                        | em dr       | rawing | I |

| Prepared                                                     | l in acc                           | cordan | ice with    | ASMI              | E Y14 | 4.24                                         |                  |                         |                       |      |        |                          |                                   |                           |                                                 |                                               |                                               | Ve                             | ndor it                        | em dr       | rawing | I |

| Prepared                                                     | l in acc                           | cordan | ce with     | ASM               | E Y14 | 4.24                                         |                  |                         |                       |      |        |                          |                                   |                           |                                                 |                                               |                                               | Ve                             | ndor it                        | em dr       | rawing | 1 |

|                                                              | in acc                             | cordan | ce with     | ASME              | E Y14 | 4.24                                         |                  |                         |                       |      |        |                          |                                   |                           |                                                 |                                               |                                               | Ve                             | ndor it                        | em dr       | rawing |   |

| REV                                                          |                                    | cordan | ce with     | ASM               | E Y14 | 4.24                                         |                  |                         |                       |      |        |                          |                                   |                           |                                                 |                                               |                                               | Ve                             | ndor it                        | em dr       | rawing |   |

| REV<br>PAGE                                                  |                                    | cordan | ce with     | ASME              | E Y14 | 4.24                                         |                  |                         |                       |      |        |                          |                                   |                           |                                                 |                                               |                                               | Ve                             | ndor it                        | em dr       | rawing |   |

| REV<br>PAGE<br>REV<br>PAGE<br>REV STA                        |                                    | cordan | ce with     | ASM               | E Y14 | 4.24                                         |                  |                         |                       |      |        |                          |                                   |                           |                                                 |                                               |                                               | Ve                             | ndor it                        | em dr       | rawing |   |

| REV<br>PAGE<br>REV<br>PAGE                                   |                                    | cordan |             |                   | E Y14 | 1.24                                         | 2                | 3                       | 4                     | 5    | 6      | 7                        | 8                                 | 9                         | 10                                              | 11                                            | 12                                            | Ve                             | ndor it                        | em dr       | rawing |   |

| REV<br>PAGE<br>REV<br>PAGE<br>REV STA                        |                                    | cordan | REV         |                   |       | 1<br>20 BY                                   |                  |                         |                       | 5    | 6      | 7                        | 8                                 |                           | DLA                                             | LAND                                          |                                               | 13<br>MARI                     | 14<br><b>TIME</b>              |             | rawing |   |

| REV<br>PAGE<br>REV<br>PAGE<br>REV STA<br>OF PAGE             |                                    | cordan | REV         |                   |       | 1<br>20 BY                                   |                  | 3<br>Nguye              |                       | 5    | 6      | 7                        | 8                                 | с                         | DLA<br>OLUN                                     | LAND<br>IBUS,                                 |                                               | 13<br>MARI<br>0 432            | 14<br><b>TIME</b><br>18-399    | 0           | rawing |   |

| REV<br>PAGE<br>REV<br>PAGE<br>REV STA<br>OF PAGE<br>PMIC N/A | ATUS<br>ES<br>A                    | drawin | REV         |                   | PARE  | 1<br>20 BY                                   | 'hu H.           | Nguye                   | en                    | 5    | 6      | 7                        |                                   | с                         | DLA<br>OLUN                                     | LAND<br>IBUS,                                 | AND                                           | 13<br>MARI<br>0 432            | 14<br><b>TIME</b><br>18-399    | 0           | rawing |   |

| REV<br>PAGE<br>REV<br>PAGE<br>REV STA<br>OF PAGE<br>PMIC N/A | ATUS<br>ES<br>A<br>date of<br>Y MM | drawi  | REV<br>PAGE | E<br>PREP<br>CHEC | PARE  | 1<br>20 BY<br>P                              | 'hu H.<br>'hu H. |                         | en                    | 5    | 6      | TITI                     | LE                                | C<br>http<br>CIRCL        | DLA<br>OLUN<br>://ww                            | LAND<br>IBUS,<br>w.land                       | AND<br>OHIC<br>dandn                          | 13<br>MARI<br>9 432<br>haritin | 14<br>TIME<br>18-399<br>ne.dla | 90<br>.mil/ |        |   |

| REV<br>PAGE<br>REV<br>PAGE<br>REV STA<br>OF PAGE<br>PMIC N/A | ATUS<br>ES<br>A                    | drawi  | REV<br>PAGE | E<br>PREP<br>CHEC | PARE  | 1<br>D BY<br>P<br>D BY                       | 'hu H.<br>'hu H. | Nguye                   | en                    | 5    | 6      | TITI<br>MIC<br>CH/       | L <b>E</b><br>ROC                 | C<br><u>http</u><br>CIRCL | DLA<br>OLUN<br>://www                           | LAND<br>IBUS,<br>w.land                       | AND<br>OHIC                                   | 13<br>MARI<br>9 432<br>haritin | 14<br>TIME<br>18-399<br>ne.dla | 90<br>.mil/ |        |   |

| REV<br>PAGE<br>REV<br>PAGE<br>REV STA<br>OF PAGE<br>PMIC N/A | ATUS<br>ES<br>A<br>date of<br>Y MM | drawi  | REV<br>PAGE |                   | PARE  | 1<br>20 BY<br>P<br>20 BY<br>P<br>20 BY<br>Th | hu H.            | Nguye<br>Nguye<br>M. He | en<br>en<br>ess       | 5    | 6      | TITI<br>MIC<br>CH/<br>MO | L <b>E</b><br>ROC<br>ANNE<br>NOLI | C<br><u>http</u><br>CIRCL | DLA<br>OLUN<br>://www                           | LAND<br>IBUS,<br>w.land                       | AND<br>OHIC                                   | 13<br>MARI<br>9 432<br>haritin | 14<br>TIME<br>18-399<br>ne.dla | 90<br>.mil/ |        |   |

| REV<br>PAGE<br>REV<br>PAGE<br>REV STA<br>OF PAGE<br>PMIC N/A | ATUS<br>ES<br>A<br>date of<br>Y MM | drawi  | REV<br>PAGE |                   | PARE  | 1<br>20 BY<br>P<br>20 BY<br>P<br>20 BY<br>Th | hu H.            | Nguye<br>Nguye<br>M. He | en<br>en<br>ess<br>O. | 5    | 6      | TITI<br>MIC<br>CH/<br>MO | L <b>E</b><br>ROC                 | C<br><u>http</u><br>CIRCL | DLA<br>OLUM<br>://ww<br>JIT,<br>6-BIT,<br>5-BIT | LAND<br>IBUS,<br>w.land<br>LINE<br>1MS<br>CON | AND<br>, OHIC<br><u>dandn</u><br>AR,<br>SPS F | 13<br>MARI<br>0 432<br>Daritin | 14<br>TIME<br>18-399<br>ne.dla | 90<br>.mil/ |        |   |

| REV<br>PAGE<br>REV<br>PAGE<br>REV STA<br>OF PAGE<br>PMIC N/A | ATUS<br>ES<br>A<br>date of<br>Y MM | drawi  | REV<br>PAGE |                   | PARE  | 1<br>20 BY<br>P<br>20 BY<br>P<br>20 BY<br>Th | hu H.            | Nguye<br>Nguye<br>M. He | en<br>en<br>ess       | 5    | 6      | TITI<br>MIC<br>CH/<br>MO | L <b>E</b><br>ROC<br>ANNE<br>NOLI | C<br><u>http</u><br>CIRCL | DLA<br>OLUM<br>://ww<br>JIT,<br>6-BIT,<br>5-BIT | LAND<br>IBUS,<br>w.land<br>LINE<br>1MS<br>CON | AND<br>OHIC                                   | 13<br>MARI<br>0 432<br>Daritin | 14<br>TIME<br>18-399<br>ne.dla | 90<br>.mil/ |        |   |

## 1. SCOPE

1.1 <u>Scope</u>. This drawing documents the general requirements of a high performance low cost, 4-channel, 16-bit 1 MSPS PulSAR ADC microcircuit, with an operating temperature range of -55°C to +125°C.

1.2 <u>Vendor Item Drawing Administrative Control Number</u>. The manufacturer's PIN is the item of identification. The vendor item drawing establishes an administrative control number for identifying the item on the engineering documentation:

| V62/14620<br>Drawing<br>number | - <u>01</u><br>Device type<br>(See 1.2.1) | Case outline<br>(See 1.2.2) | Lead finish<br>(See 1.2.3)            |

|--------------------------------|-------------------------------------------|-----------------------------|---------------------------------------|

| 1.2.1 Device type(s).          |                                           |                             |                                       |

| Device type                    | Generic                                   | <u>Ci</u>                   | rcuit function                        |

| 01                             | AD7655-EP                                 | Low cost                    | , 4-channel, 16-bit 1 MSPS PulSAR ADC |

1.2.2 <u>Case outline(s)</u>. The case outlines are as specified herein.

| Outline letter | Number of pins | JEDEC PUB 95        | Package style                           |

|----------------|----------------|---------------------|-----------------------------------------|

| Х              | 48             | JEDEC MO-220-VKKD-2 | Lead Frame Chip Scale Package(LFCSP_VQ) |

1.2.3 Lead finishes. The lead finishes are as specified below or other lead finishes as provided by the device manufacturer:

| Finish designator          | Material                                                                                     |

|----------------------------|----------------------------------------------------------------------------------------------|

| A<br>B<br>C<br>D<br>E<br>Z | Hot solder dip<br>Tin-lead plate<br>Gold plate<br>Palladium<br>Gold flash palladium<br>Other |

|                            |                                                                                              |

| DLA LAND AND MARITIME | SIZE | CODE IDENT NO. | DWG NO. <b>V62/14620</b> |

|-----------------------|------|----------------|--------------------------|

| COLUMBUS, OHIO        | A    | 16236          |                          |

|                       |      | REV            | PAGE 2                   |

#### 1.3 Absolute maximum ratings. 1/

| Analog input:<br>INAx, INBx, REFx, INxN, REFGND | AVDD + 0.3 V to AGND – 0.3 V |

|-------------------------------------------------|------------------------------|

| Ground voltage differences:<br>AGND, DGND, OGND | ±0.3 V                       |

| Supply voltages:                                |                              |

| AVDD, DVDD, OVDD                                | -0.3 V to +7 V               |

| AVDD to DVDD, AVDD to OVDD                      | . ±7 V                       |

| DVDD to OVDD                                    | -0.3 V to +7 V               |

| Digital inputs                                  | -0.3 V to DVDD + 0.3 V       |

| Internal power dissipation                      |                              |

| Junction temperature                            | 150°C                        |

| Storage temperature range                       | -65°C to 150°C               |

| Lead temperature range (Soldering 10 sec)       |                              |

#### 2. APPLICABLE DOCUMENTS

JEDEC – SOLID STATE TECHNOLOGY ASSOCIATION (JEDEC)

JEP95 – Registered and Standard Outlines for Semiconductor Devices

(Copies of these documents are available online at http://www.jedec.org or from JEDEC – Solid State Technology Association, 3103 North 10th Street, Suite 240–S, Arlington, VA 22201-2107).

#### 3. REQUIREMENTS

3.1 <u>Marking</u>. Parts shall be permanently and legibly marked with the manufacturer's part number as shown in 6.3 herein and as follows:

- A. Manufacturer's name, CAGE code, or logo

- B. Pin 1 identifier

- C. ESDS identification (optional)

3.2 <u>Unit container</u>. The unit container shall be marked with the manufacturer's part number and with items A and C (if applicable) above.

3.3 <u>Electrical characteristics</u>. The maximum and recommended operating conditions and electrical performance characteristics are as specified in 1.3, 1.4, and table I herein.

3.4 <u>Design, construction, and physical dimension</u>. The design, construction, and physical dimensions are as specified herein.

<sup>&</sup>lt;u>2</u>/ Specification is for device in free air: case outline X,  $\theta_{JA} = 26^{\circ}$ C/W.

| DLA LAND AND MARITIME | SIZE | CODE IDENT NO. | DWG NO.          |

|-----------------------|------|----------------|------------------|

| COLUMBUS, OHIO        | A    | <b>16236</b>   | <b>V62/14620</b> |

|                       |      | REV            | PAGE 3           |

<sup>&</sup>lt;u>1</u>/ Stresses beyond those listed under "absolute maximum ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated under "recommended operating conditions" is not implied. Exposure to absolute maximum rated conditions for extended periods may affect device reliability.

# 3.5 Diagrams.

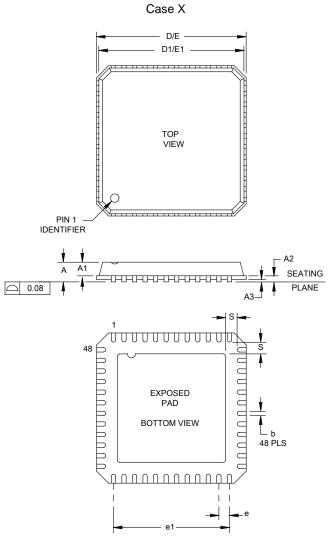

- 3.5.1 <u>Case outline</u>. The case outline shall be as shown in 1.2.2 and figure 1.

- 3.5.2 <u>Terminal connections</u>. The terminal connections shall be as shown in figure 2.

- 3.5.3 <u>Terminal function description</u>. The terminal function description shall be as shown in figure 3.

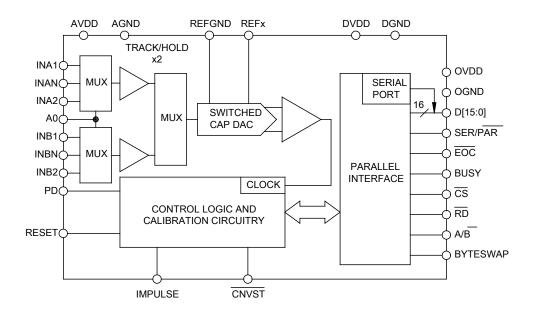

- 3.5.4 <u>Functional block diagram</u>. The functional block diagram shall be as shown in figure 4.

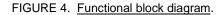

- 3.5.5 <u>Load circuit for digital interface timing</u>. The load circuit for digital interface timing shall be as shown in figure 5.

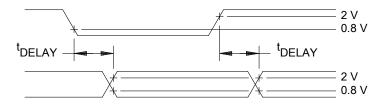

- 3.5.6 <u>Voltage reference levels for timings</u>. The voltage reference levels for timings shall be as shown in figure 6.

| DLA LAND AND MARITIME | SIZE | CODE IDENT NO. | DWG NO. <b>V62/14620</b> |

|-----------------------|------|----------------|--------------------------|

| COLUMBUS, OHIO        | A    | <b>16236</b>   |                          |

|                       |      | REV            | PAGE 4                   |

| Test                                | Test conditions                         |      | Limits |                    |                |  |

|-------------------------------------|-----------------------------------------|------|--------|--------------------|----------------|--|

|                                     | <u>2</u> /                              | Min  | Тур    | Max                |                |  |

| RESOLUTION                          |                                         | 16   |        |                    | Bits           |  |

| ANALOG INPUT                        |                                         |      | •      | •                  | •              |  |

| Voltage Range                       | $V_{INx} - V_{INxN}$                    | 0    |        | 2 V <sub>REF</sub> | V              |  |

| Common-Mode Input Voltage           | V <sub>INxN</sub>                       | -0.1 |        | +0.5               | V              |  |

| Analog Input CMRR                   | f <sub>IN</sub> = 100 kHz               |      | 55     |                    | dB             |  |

| Input Current                       | 1 MSPS throughput                       |      | 45     |                    | μA             |  |

| Input Impedance                     |                                         |      |        |                    |                |  |

| THROUGHPUT SPEED                    |                                         |      |        |                    |                |  |

| Complete Cycle (2 Channels)         | Normal mode                             |      |        | 2                  | μs             |  |

| Throughput Rate                     | Normal mode                             | 0    |        | 1                  | MSPS           |  |

| Complete Cycle (2 Channels)         | Impulse mode                            |      |        | 2.25               | μs             |  |

| Throughput Rate                     | Impulse mode                            | 0    |        | 888                | kSPS           |  |

| DC ACCURACY                         |                                         |      |        |                    |                |  |

| Integral Linearity Error <u>3</u> / |                                         | -6   |        | +6                 | LSB <u>4</u> / |  |

| No Missing Codes                    |                                         | 15   |        |                    | Bits           |  |

| Transition Noise                    |                                         |      | 0.8    |                    | LSB            |  |

| Full-Scale Error                    | T <sub>MIN</sub> to T <sub>MAX</sub>    |      | ±0.25  | ±0.5               | % of FSF       |  |

| Full-Scale Error Drift              |                                         |      | ±2     |                    | ppm/°C         |  |

| Unipolar Zero Error                 | T <sub>MIN</sub> to T <sub>MAX</sub>    |      |        | ±0.25              | % of FSF       |  |

| Unipolar Zero Error Drift           |                                         |      | ±0.8   |                    | ppm/°C         |  |

| Power Supply Sensitivity            | $AVDD = 5 V \pm 5\%$                    |      | ±0.8   |                    | LSB            |  |

| AC ACCURACY                         |                                         |      |        |                    |                |  |

| Signal-to-Noise                     | f <sub>IN</sub> = 100 kHz               |      | 86     |                    | dB <u>5</u> /  |  |

| Spurious-Free Dynamic Range         | f <sub>IN</sub> = 100 kHz               |      | 98     |                    | dB             |  |

| Total Harmonic Distortion           | f <sub>IN</sub> = 100 kHz               |      | -96    |                    | dB             |  |

| Signal-to-Noise and Distortion      | f <sub>IN</sub> = 100 kHz               |      | 86     |                    | dB             |  |

|                                     | f <sub>IN</sub> = 100 kHz, −60 dB input |      | 30     |                    | dB             |  |

| Channel-to-Channel Isolation        | f <sub>IN</sub> = 100 kHz               |      | -92    |                    | dB             |  |

| -3 dB Input Bandwidth               |                                         |      | 10     |                    | MHz            |  |

| SAMPLING DYNAMICS                   |                                         |      |        |                    |                |  |

| Aperture Delay                      |                                         |      | 2      |                    | ns             |  |

| Aperture Delay Matching             |                                         |      | 30     |                    | ps             |  |

| Aperture Jitter                     |                                         |      | 5      |                    | ps rms         |  |

| Transient Response                  | Full-scale step                         |      |        | 250                | ns             |  |

| REFERENCE                           |                                         |      |        | -                  |                |  |

| External Reference Voltage Range    |                                         | 2.3  | 2.5    | AVDD/2             | V              |  |

| External Reference Current Drain    | 1 MSPS throughput                       |      | 180    |                    | μA             |  |

## TABLE I. <u>Electrical performance characteristics</u>. <u>1</u>/

See footnote at end of table.

| DLA LAND AND MARITIME | SIZE | CODE IDENT NO. | DWG NO.   |

|-----------------------|------|----------------|-----------|

| COLUMBUS, OHIO        | A    | <b>16236</b>   | V62/14620 |

|                       |      | REV            | PAGE 5    |

| Test                                 | Symbol         | Test conditions                      |            | Limits |                 | Unit |

|--------------------------------------|----------------|--------------------------------------|------------|--------|-----------------|------|

|                                      |                | <u>2</u> /                           | Min        | Тур    | Max             |      |

| DIGITAL INPUTS                       |                |                                      |            |        |                 |      |

| Logic Levels                         |                |                                      |            |        |                 |      |

| V <sub>IL</sub>                      |                |                                      | -0.3       |        | +0.8            | V    |

| V <sub>IH</sub>                      |                |                                      | +2.0       |        | DVDD + 0.3      | V    |

| l <sub>IL</sub>                      |                |                                      | -1         |        | +1              | μΑ   |

| I <sub>IH</sub>                      |                |                                      | -1         |        | +1              | μA   |

| DIGITAL OUTPUTS                      |                |                                      |            |        | 1               |      |

| Data Format <u>6</u> /               |                |                                      |            |        |                 |      |

| Pipeline Delay <u>7</u> /            |                |                                      |            |        |                 |      |

| V <sub>OL</sub>                      |                | $I_{SINK} = 1.6 \text{ mA}$          |            |        | 0.4             | V    |

| V <sub>OH</sub>                      |                | I <sub>SOURCE</sub> = −500 μA        | OVDD – 0.2 |        |                 | V    |

| POWER SUPPLIES                       |                |                                      |            |        |                 |      |

| Specified performance                |                | 1                                    | 1          |        | 1               |      |

| AVDD                                 |                |                                      | 4.75       | 5      | 5.25            | V    |

| DVDD                                 |                |                                      | 4.75       | 5      | 5.25            | V    |

| OVDD                                 |                |                                      | 2.7        |        | 5.25 <u>8</u> / | V    |

| Operating current <u>9</u> /         |                |                                      |            |        |                 |      |

| AVDD                                 |                | 1 MSPS throughput                    |            | 15.5   |                 | mA   |

| DVDD                                 |                |                                      |            | 8.5    |                 | mA   |

| OVDD                                 |                |                                      |            | 100    |                 | μA   |

|                                      |                | 1 MSPS throughput <u>9</u> /         |            | 120    | 135             | mW   |

| Power Dissipation                    |                | 20 kSPS throughput 10/               |            | 2.6    |                 | mW   |

|                                      |                | 888 kSPS throughput 10/              |            | 114    | 125             | mW   |

| TEMPERATURE RANGE <u>11</u> /        |                |                                      |            |        |                 |      |

| Specified Performance                |                | T <sub>MIN</sub> to T <sub>MAX</sub> | -55        |        | +125            | °C   |

|                                      | TI             | MING SPECIFICATIONS                  |            |        |                 |      |

| CONVERSION AND RESET                 |                |                                      |            |        |                 |      |

| Convert Pulse Width                  | t <sub>1</sub> |                                      | 5          |        |                 | ns   |

| Time Between Conversions             | t <sub>2</sub> |                                      | 2/2.25     |        |                 | μs   |

| (Normal Mode/Impulse Mode)           |                |                                      |            |        |                 |      |

| CNVST Low to BUSY High Delay         | t <sub>3</sub> |                                      |            |        | 32              | ns   |

| BUSY High All Modes Except in Master | t <sub>4</sub> |                                      |            |        | 1.75/2          | μs   |

| Serial Read After Convert Mode       |                |                                      |            |        |                 |      |

| (Normal Mode/Impulse Mode)           |                |                                      |            |        |                 |      |

| Aperture Delay                       | t <sub>5</sub> |                                      |            | 2      |                 | ns   |

| End of Conversions to BUSY Low Delay | t <sub>6</sub> |                                      | 10         |        |                 | ns   |

# TABLE I. <u>Electrical performance characteristics</u> - Continued. <u>1</u>/

See footnote at end of table.

| DLA LAND AND MARITIME | SIZE | CODE IDENT NO. | DWG NO.   |

|-----------------------|------|----------------|-----------|

| COLUMBUS, OHIO        | A    | <b>16236</b>   | V62/14620 |

|                       |      | REV            | PAGE 6    |

| TABLE I. | Electrical performance characteristics - Continued. | <u>1</u> / |

|----------|-----------------------------------------------------|------------|

|----------|-----------------------------------------------------|------------|

| Test                                                            | Symbol          | Test conditions |     | Limits  |        | Unit |

|-----------------------------------------------------------------|-----------------|-----------------|-----|---------|--------|------|

|                                                                 | <u>2</u> /      |                 | Min | Тур     | Max    |      |

| TII                                                             | MING SPEC       | IFICATIONS      |     |         |        |      |

| CONVERSION AND RESET – Continued.                               |                 |                 |     |         |        |      |

| Conversion Time                                                 | t7              |                 |     |         | 1.75/2 | μs   |

| (Normal Mode/Impulse Mode)                                      |                 |                 |     | _       |        |      |

| Acquisition Time                                                | t <sub>8</sub>  |                 | 250 |         |        | ns   |

| RESET Pulse Width                                               | t <sub>9</sub>  |                 | 10  |         |        | ns   |

| CNVST Low to EOC high delay                                     | t <sub>10</sub> |                 |     |         | 30     | ns   |

| EOC high for channel A conversion                               | t <sub>11</sub> |                 |     |         | 1/1.25 | μs   |

| (Normal Mode/Impulse Mode)                                      |                 |                 |     |         |        |      |

| EOC low after Channel A Conversion                              | t <sub>12</sub> |                 | 45  |         |        | ns   |

| EOC high for channel A conversion                               | t <sub>13</sub> |                 |     |         | 0.75   | μs   |

| Channel Selection Setup Time                                    | t <sub>14</sub> |                 | 250 |         |        | ns   |

| Channel Selection Hold Time                                     | t <sub>15</sub> |                 |     |         | 30     | ns   |

| PARALLEL INTERFACE MODES                                        |                 |                 |     |         |        |      |

| CNVST Low to DATA Valid Delay                                   | t <sub>16</sub> |                 |     |         | 1.75/2 | μs   |

| DATA Valid to BUSY Low Delay                                    | t <sub>17</sub> |                 | 14  |         |        | ns   |

| Bus Access Request to DATA Valid                                | t <sub>18</sub> |                 |     |         | 40     | ns   |

| Bus Relinquish Time                                             | t <sub>19</sub> |                 | 5   |         | 15     | ns   |

| $A/\overline{B}$ Low to Data Valid Delay                        | t <sub>20</sub> |                 |     |         | 40     | ns   |

| MASTER SERIAL INTERFACE MODES                                   |                 |                 |     |         |        |      |

| CS Low to SYNC Valid Delay                                      | t <sub>21</sub> |                 |     |         | 10     | ns   |

| CS Low to Internal SCLK Valid Delay 12/                         | t <sub>22</sub> |                 |     |         | 10     | ns   |

| CS Low to SDOUT Delay                                           | t <sub>23</sub> |                 |     |         | 10     | ns   |

| CNVST Low to SYNC Delay, Read During Convert                    | t <sub>24</sub> |                 |     | 250/500 |        | ns   |

| (Normal Mode/Impulse Mode)                                      |                 |                 |     |         |        |      |

| SYNC Asserted to SCLK First Edge Delay                          | t <sub>25</sub> |                 | 3   |         |        | ns   |

| Internal SCK Period 13/                                         | t <sub>26</sub> |                 | 23  |         | 40     | ns   |

| Internal SCLK High <u>13</u> /                                  | t <sub>27</sub> |                 | 12  |         |        | ns   |

| Internal SCLK Low <u>13</u> /                                   | t <sub>28</sub> |                 | 7   |         |        | ns   |

| SDOUT Valid Setup Time <u>13</u> /                              | t <sub>29</sub> |                 | 4   |         |        | ns   |

| SDOUT Valid Hold Time <u>13</u> /                               | t <sub>30</sub> |                 | 2   |         |        | ns   |

| SCLK Last Edge to SYNC Delay <u>13</u> /                        | t <sub>31</sub> |                 | 1   |         |        | ns   |

| CS High to SYNC High-Z                                          | t <sub>32</sub> |                 |     |         | 10     | ns   |

| CS High to Internal SCLK High-Z                                 | t <sub>33</sub> |                 |     |         | 10     | ns   |

| CS High to SDOUT High-Z                                         | t <sub>34</sub> |                 |     |         | 10     | ns   |

| BUSY High in Master Serial Read after Convert $\underline{13}/$ | t <sub>35</sub> |                 |     | 14/     | -      | ns   |

| CNVST Low to SYNC Asserted Delay                                | t <sub>36</sub> |                 |     | 0.75/1  |        | μs   |

| (Normal Mode/Impulse Mode)                                      | -00             |                 |     |         |        |      |

| SYNC Deasserted to BUSY Low Delay                               | t <sub>37</sub> |                 |     | 25      |        | ns   |

See footnote at end of table.

| DLA LAND AND MARITIME | SIZE | CODE IDENT NO. | DWG NO. <b>V62/14620</b> |

|-----------------------|------|----------------|--------------------------|

| COLUMBUS, OHIO        | A    | 16236          |                          |

|                       |      | REV            | PAGE 7                   |

## TABLE I. Electrical performance characteristics - Continued. 1/

| Test                                                                                                                                                                                                                                                                                                                                                                                                                 | Symbol                                                                                | Test conditions                                                                                                 | Limits                                                     |                                              |                                      | Unit          |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------|------------------------------------------------------------|----------------------------------------------|--------------------------------------|---------------|

|                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                       | <u>2</u> /                                                                                                      | Min                                                        | Тур                                          | Max                                  |               |

| TIM                                                                                                                                                                                                                                                                                                                                                                                                                  | ING SPECIFICAT                                                                        | IONS – Continued.                                                                                               | <u>.</u>                                                   |                                              |                                      |               |

| SLAVE SERIAL INTERFACE MODES                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                       |                                                                                                                 |                                                            |                                              |                                      | _             |

| External SCLK Setup Time                                                                                                                                                                                                                                                                                                                                                                                             | t <sub>38</sub>                                                                       |                                                                                                                 | 5                                                          |                                              |                                      | ns            |

| External SCLK Active Edge to SDOUT Delay                                                                                                                                                                                                                                                                                                                                                                             | t <sub>39</sub>                                                                       |                                                                                                                 | 3                                                          |                                              | 18                                   | ns            |

| SDIN Setup Time                                                                                                                                                                                                                                                                                                                                                                                                      | t <sub>40</sub>                                                                       |                                                                                                                 | 5                                                          |                                              |                                      | ns            |

| SDIN Hold Time                                                                                                                                                                                                                                                                                                                                                                                                       | t <sub>41</sub>                                                                       |                                                                                                                 | 5                                                          |                                              |                                      | ns            |

| External SCLK Period                                                                                                                                                                                                                                                                                                                                                                                                 | t <sub>42</sub>                                                                       |                                                                                                                 | 25                                                         |                                              |                                      | ns            |

| External SCLK High                                                                                                                                                                                                                                                                                                                                                                                                   | t <sub>43</sub>                                                                       |                                                                                                                 | 10                                                         |                                              |                                      | ns            |

| External SCLK Low                                                                                                                                                                                                                                                                                                                                                                                                    | t44                                                                                   |                                                                                                                 | 10                                                         |                                              |                                      | ns            |

| <ul> <li>/ Testing and other quality control techniques are specified temperature range. Product may not r necessarily be tested. In the absence of specific design.</li> <li>/ AVDD = DVDD = 5 V, OVDD = 2.7 V to 5.25 V;</li> <li>/ Linearity is tested using endpoints, not best fit.</li> <li>/ LSB means least significant bit. With the 0 V to All specifications in dB are referred to as full-sca</li> </ul> | necessarily be test<br>c parametric testin<br>VREF = 2.5 V; all<br>5 V input range, 1 | ed across the full temper<br>g, product performance<br>specifications $T_{MIN}$ to $T_{I}$<br>LSB is 76.294 µV. | erature range<br>is assured b<br><sub>MAX</sub> , unless o | e and all par<br>by character<br>therwise no | rameters ma<br>rization and<br>oted. | ay not<br>/or |

| specified.                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                       |                                                                                                                 |                                                            |                                              |                                      |               |

| <ul> <li>Parallel or serial 16 bit.</li> <li>Conversion results are available immediately aff</li> <li>The maximum should be the minimum of 5.25 V</li> <li>In normal mode: tested in parallel reading mode</li> </ul>                                                                                                                                                                                               | ter completed con                                                                     | version                                                                                                         |                                                            |                                              |                                      |               |

| The maximum should be the minimum of 5.25 V                                                                                                                                                                                                                                                                                                                                                                          |                                                                                       |                                                                                                                 |                                                            |                                              |                                      |               |

| In normal mode: tested in parallel reading mode                                                                                                                                                                                                                                                                                                                                                                      |                                                                                       |                                                                                                                 |                                                            |                                              |                                      |               |

In normal mode; tested in parallel reading mode

In impulse mode; tested in parallel reading mode.

Consult sales for extended temperature range.

<u>9</u>/ <u>10</u>/ <u>11</u>/ <u>12</u>/ In serial interface modes, the SYNC, SCLK, and SDOUT timings are defined with a maximum load CL of 10 pF; otherwise CL is 60 pF maximum.

<u>13</u>/ In serial master read during convert mode. See <u>14</u>/ for serial master read after convert mode.

14/ Serial Clock Timings in Master Read After Convert.

| DIVSCLK[1]                            | Symbol          | 0    | 0    | 1    | 1     | Units |

|---------------------------------------|-----------------|------|------|------|-------|-------|

| DIVSCLK[0]                            |                 | 0    | 1    | 0    | 1     |       |

| SYNC to SCLK First Edge Delay Minimum | t <sub>25</sub> | 3    | 17   | 17   | 17    | ns    |

| Internal SCLK Period Minimum          | t <sub>26</sub> | 25   | 50   | 100  | 200   | ns    |

| Internal SCLK Period Typical          | t <sub>26</sub> | 40   | 70   | 140  | 280   | ns    |

| Internal SCLK High Minimum            | t <sub>27</sub> | 12   | 22   | 50   | 100   | ns    |

| Internal SCLK Low Minimum             | t <sub>28</sub> | 7    | 21   | 49   | 99    | ns    |

| SDOUT Valid Setup Time Minimum        | t <sub>29</sub> | 4    | 18   | 18   | 18    | ns    |

| SDOUT Valid Hold Time Minimum         | t <sub>30</sub> | 2    | 4    | 30   | 80    | ns    |

| SCLK Last Edge to SYNC Delay Minimum  | t <sub>31</sub> | 1    | 3    | 30   | 80    | ns    |

| Busy High Width Maximum (Normal)      | t <sub>35</sub> | 3.25 | 4.25 | 6.25 | 10.75 | μs    |

| Busy High Width Maximum (Impulse)     | t <sub>35</sub> | 3.5  | 4.5  | 6.5  | 11    | μs    |

| DLA LAND AND MARITIME | SIZE | CODE IDENT NO. | DWG NO. <b>V62/14620</b> |  |

|-----------------------|------|----------------|--------------------------|--|

| COLUMBUS, OHIO        | A    | <b>16236</b>   |                          |  |

|                       |      | REV            | PAGE 8                   |  |

| Dimensions |             |      |        |          |        |  |  |

|------------|-------------|------|--------|----------|--------|--|--|

| Symbol     | Millimeters |      | Symbol | Millim   | neters |  |  |

|            | Min         | Max  |        | Min      | Max    |  |  |

| А          | 0.80        | 1.00 | D/E    | 7.00     | BSC    |  |  |

| A1         |             | 0.80 | D1/E1  | 6.75     | BSC    |  |  |

| A2         | 0.20        | REF  | е      | 0.50 BSC |        |  |  |

| A3         |             | 0.05 | e1     | 5.50     | REF    |  |  |

| b          | 0.18        | 0.30 | S      | 0.25     |        |  |  |

## NOTES:

- 1. All linear dimensions are in millimeters.

- 2. Falls within JEDEC MO-15-AB3.

FIGURE 1. Case outline.

| DLA LAND AND MARITIME | SIZE | CODE IDENT NO. | DWG NO.   |

|-----------------------|------|----------------|-----------|

| COLUMBUS, OHIO        | A    | 16236          | V62/14620 |

|                       |      | REV            | PAGE 9    |

|                    | Case outline X     |                    |                    |                    |                    |                    |                    |  |

|--------------------|--------------------|--------------------|--------------------|--------------------|--------------------|--------------------|--------------------|--|

| Terminal<br>number | Terminal<br>symbol | Terminal<br>number | Terminal<br>symbol | Terminal<br>number | Terminal<br>symbol | Terminal<br>number | Terminal<br>symbol |  |

| 1                  | AGND               | 13                 | D4/EXT/INT         | 25                 | D12                | 37                 | REF                |  |

| 2                  | AVDD               | 14                 | D5/INVSYNC         | 26                 | D13                | 38                 | REFGND             |  |

| 3                  | A0                 | 15                 | D6/INVSCLK         | 27                 | D14                | 39                 | INB1               |  |

| 4                  | BYTESWAP           | 16                 | D7/RDC/SDIN        | 28                 | D15                | 40                 | INBN               |  |

| 5                  | $A/\overline{B}$   | 17                 | OGND               | 29                 | BUSY               | 41                 | INB2               |  |

| 6                  | DGND               | 18                 | OVDD               | 30                 | EOC                | 42                 | REFB               |  |

| 7                  | IMPULSE            | 19                 | DVDD               | 31                 | RD                 | 43                 | REFAA              |  |

| 8                  | SER/PAR            | 20                 | DGND               | 32                 | $\overline{CS}$    | 44                 | INA2               |  |

| 9                  | D0                 | 21                 | D8/SDOUT           | 33                 | RESET              | 45                 | INAN               |  |

| 10                 | D1                 | 22                 | D9/SCLK            | 34                 | PD                 | 46                 | INA1               |  |

| 11                 | D2/DIVSCLK[0]      | 23                 | D10/SYNC           | 35                 | CNVST              | 47                 | AGND               |  |

| 12                 | D3/DIVSCLK[1]      | 24                 | D11/RDERROR        | 36                 | DVDD               | 48                 | AGND               |  |

| FIGURE 2. | Terminal | connections. |

|-----------|----------|--------------|

|-----------|----------|--------------|

| Pin No.   | Mnemonic                  | Type <u>1</u> / | Description                                                                                                                                                                                                                                                                                                                                                                                   |

|-----------|---------------------------|-----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1, 47, 48 | AGND                      | Р               | Analog Power Ground Pin.                                                                                                                                                                                                                                                                                                                                                                      |

| 2         | AVDD                      | Р               | Input Analog Power Pin. Nominally 5 V.                                                                                                                                                                                                                                                                                                                                                        |

| 3         | A0                        | DI              | Multiplexer Select. When LOW, the analog inputs INA1 and INB1 are sampled simultaneously, then converted. When HIGH, the analog inputs INA2 and INB2 are sampled simultaneously, then converted.                                                                                                                                                                                              |

| 4         | BYTESWAP                  | DI              | Parallel Mode Selection (8 Bit, 16 Bit). When LOW, the LSB is output on D[7:0] and the MSB is output on D[15:8]. When HIGH, the LSB is output on D[15:8] and the MSB is output on D[7:0].                                                                                                                                                                                                     |

| 5         | A/B                       | DI              | Data Channel Selection. In parallel mode, when LOW, the data from Channel B is read. When HIGH, the data from Channel A is read. In serial mode, when HIGH, Channel A is output first followed by Channel B. When LOW, Channel B is output first followed by Channel A.                                                                                                                       |

| 6, 20     | DGND                      | Р               | Digital Power Ground                                                                                                                                                                                                                                                                                                                                                                          |

| 7         | IMPULSE                   | DI              | Mode Selection. When HIGH, this input selects a reduced power mode. In this mode, the power dissipation is approximately proportional to the sampling rate.                                                                                                                                                                                                                                   |

| 8         | SER/PAR                   | DI              | Serial/Parallel Selection Input. When LOW, the parallel port is selected; when HIGH, the serial interface mode is selected and some bits of the DATA bus are used as a serial port.                                                                                                                                                                                                           |

| 9, 10     | D[0:1]                    | DO              | Bit 0 and Bit 1 of the Parallel Port Data Output Bus. When SER/PAR is HIGH, these outputs are in high impedance.                                                                                                                                                                                                                                                                              |

| 11, 12    | D[2:3] or<br>DIVSCLK[0:1] | DI/O            | When SER/PAR is LOW, these outputs are used as Bit 2 and Bit 3 of the Parallel Port Data Output Bus. When SER/PAR is HIGH, EXT/INT is LOW, and RDC/SDIN is LOW, which is the serial master read after convert mode. These inputs, part of the serial port, are used to slow down the internal serial clock that clocks the data output. In the other serial modes, these inputs are not used. |

FIGURE 3. Terminal function description.

| DLA LAND AND MARITIME | SIZE | CODE IDENT NO. | DWG NO. <b>V62/14620</b> |  |

|-----------------------|------|----------------|--------------------------|--|

| COLUMBUS, OHIO        | A    | <b>16236</b>   |                          |  |

|                       |      | REV            | PAGE 10                  |  |

| Pin No. | Mnemonic           | Type <u>1</u> / | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|---------|--------------------|-----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 13      | D[4]               | DI/O            | When SER/PAR is LOW, this output is used as Bit 4 of the Parallel Port Data Output Bus.                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|         | or EXT/INT         |                 | When SER/PAR is HIGH, this input, part of the serial port, is used as a digital select input for choosing the internal or an external data clock called, respectively, master and slave mode. With EXT/INT tied LOW, the internal clock is selected on SCLK output. With EXT/INT set to a logic HIGH, output data is synchronized to an external clock signal connected to the SCLK input.                                                                                                                                                              |

| 14      | D[5]               | DI/O            | When SER/PAR is LOW, this output is used as Bit 5 of the Parallel Port Data Output Bus.                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|         | or INVSYNC         |                 | When SER/PAR is HIGH, this input, part of the serial port, is used to select the active state of the SYNC signal in Master modes. When LOW, SYNC is active HIGH. When HIGH, SYNC is active LOW                                                                                                                                                                                                                                                                                                                                                          |

| 15      | D[6]<br>or INVSCLK | DI/O            | When SER/PAR is LOW, this output is used as Bit 6 of the parallel port data output bus.<br>When SER/PAR is HIGH, this input, part of the serial port, is used to invert the SCLK signal. It is active in both master and slave modes                                                                                                                                                                                                                                                                                                                    |

| 16      | D[7]               | DI/O            | When SER/PAR is LOW, this output is used as Bit 7 of the Parallel Port Data Output Bus.                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|         | or RDC/SDIN        |                 | When SER/PAR is HIGH, this input, part of the serial port, is used as either an external data input or a read mode selection input, depending on the state of EXT/INT.                                                                                                                                                                                                                                                                                                                                                                                  |

|         |                    |                 | When EXT/INT is HIGH, RDC/SDIN can be used as a data input to daisy-chain the conversion results from two or more ADCs onto a single SDOUT line. The digital data level on SDIN is output on SDOUT with a delay of 32 SCLK periods after the initiation of the read sequence. When EXT/INT is LOW, RDC/SDIN is used to select the read mode. When RDC/SDIN is HIGH, the previous data is output on SDOUT during conversion. When RDC/SDIN is LOW, the data can be output on SDOUT only when the conversion is complete.                                 |