|                                                              |               |        |         |       |       |       |       |       |     |      |                                   |                  | REVIS | SIONS | ,      |            |            |       |         |        |       |    |

|--------------------------------------------------------------|---------------|--------|---------|-------|-------|-------|-------|-------|-----|------|-----------------------------------|------------------|-------|-------|--------|------------|------------|-------|---------|--------|-------|----|

|                                                              |               |        |         |       | L     | ΓR    |       |       |     | DESC | RIPTI                             | ON               |       |       |        | D          | ATE        |       | ļ       | APPRO  | OVED  |    |

|                                                              |               |        |         |       |       |       |       |       |     |      |                                   |                  |       |       |        |            |            |       |         |        |       |    |

|                                                              |               |        |         |       |       |       |       |       |     |      |                                   |                  |       |       |        |            |            |       |         |        |       |    |

|                                                              |               |        |         |       |       |       |       |       |     |      |                                   |                  |       |       |        |            |            |       |         |        |       |    |

|                                                              |               |        |         |       |       |       |       |       |     |      |                                   |                  |       |       |        |            |            |       |         |        |       |    |

|                                                              |               |        |         |       |       |       |       |       |     |      |                                   |                  |       |       |        |            |            |       |         |        |       |    |

|                                                              |               |        |         |       |       |       |       |       |     |      |                                   |                  |       |       |        |            |            |       |         |        |       |    |

|                                                              |               |        |         |       |       |       |       |       |     |      |                                   |                  |       |       |        |            |            |       |         |        |       |    |

|                                                              |               |        |         |       |       |       |       |       |     |      |                                   |                  |       |       |        |            |            |       |         |        |       |    |

|                                                              |               |        |         |       |       |       |       |       |     |      |                                   |                  |       |       |        |            |            |       |         |        |       |    |

|                                                              |               |        |         |       |       |       |       |       |     |      |                                   |                  |       |       |        |            |            |       |         |        |       |    |

|                                                              |               |        |         |       |       |       |       |       |     |      |                                   |                  |       |       |        |            |            |       |         |        |       |    |

|                                                              |               |        |         |       |       |       |       |       |     |      |                                   |                  |       |       |        |            |            |       |         |        |       |    |

|                                                              |               |        |         |       |       |       |       |       |     |      |                                   |                  |       |       |        |            |            |       |         |        |       |    |

|                                                              |               |        |         |       |       |       |       |       |     |      |                                   |                  |       |       |        |            |            |       |         |        |       |    |

|                                                              |               |        |         |       |       |       |       |       |     |      |                                   |                  |       |       |        |            |            |       |         |        |       |    |

|                                                              |               |        |         |       |       |       |       |       |     |      |                                   |                  |       |       |        |            |            |       |         |        |       |    |

|                                                              |               |        |         |       |       |       |       |       |     |      |                                   |                  |       |       |        |            |            |       |         |        |       |    |

|                                                              |               |        |         |       |       |       |       |       |     |      |                                   |                  |       |       |        |            |            |       |         |        |       |    |

|                                                              |               |        |         |       |       |       |       |       |     |      |                                   |                  |       |       |        |            |            |       |         |        |       |    |

|                                                              |               |        |         |       |       |       |       |       |     |      |                                   |                  |       |       |        |            |            |       |         |        |       |    |

|                                                              |               |        |         |       |       |       |       |       |     |      |                                   |                  |       |       |        |            |            |       |         |        |       |    |

| Prepared                                                     | in ac         | cordar | nce wit | h ASN | ИЕ Y1 | 4.24  |       |       |     |      |                                   |                  |       |       |        |            |            | Ve    | ndor it | em dra | awing |    |

| REV                                                          |               |        |         |       |       |       |       |       |     |      |                                   |                  |       |       |        |            |            |       |         |        |       |    |

| PAGE                                                         |               |        |         |       |       |       |       |       |     |      |                                   |                  |       |       |        |            |            |       |         |        |       |    |

| REV                                                          |               |        |         |       |       |       |       |       |     |      |                                   |                  |       |       |        |            |            |       |         |        |       |    |

| PAGE                                                         | 18            | 19     | 20      | 21    | 22    | 23    | 24    |       |     |      |                                   |                  |       |       |        |            |            |       |         |        |       |    |

| REV STA                                                      | TUS           |        | REV     | ,     |       |       |       |       |     |      |                                   |                  |       |       |        |            |            |       |         |        |       |    |

| OF PAGE                                                      |               |        | PAG     | βE    |       | 1     | 2     | 3     | 4   | 5    | 6                                 | 7                | 8     | 9     | 10     | 11         | 12         | 13    | 14      | 15     | 16    | 17 |

| PMIC N/A                                                     | 4             |        |         |       |       | D BY  |       |       | 1   |      |                                   |                  |       | D     | LA L   | AND        | AND        | MAI   | RITIN   | 1E     | I     |    |

|                                                              |               |        |         | RIC   | CK OF | FICE  | 3     |       |     |      |                                   |                  |       |       |        |            |            | O 43  |         |        |       |    |

|                                                              |               |        |         |       |       |       |       |       |     |      |                                   | http://www.landa |       |       | landr  | nariti     | ime.c      | dla.m | il/     |        |       |    |

| Original date of drawing YY-MM-DD CHECKED BY RAJESH PITHADIA |               |        |         |       |       |       | TIT   | LE    |     |      |                                   |                  |       |       |        |            |            |       |         |        |       |    |

|                                                              | vv.<br> 3-10- |        |         |       |       | ED BY |       |       |     |      |                                   | MIC              | ROC   | IRC   | JIT, I | INE        | AR, 1      | .2 Gł | Hz, C   | LOC    | K     |    |

| •                                                            | 10-10-        | 20     |         |       |       |       | SAFFL | E     |     |      | FANOUT BUFFER, MONOLITHIC SILICON |                  |       |       |        |            |            |       |         |        |       |    |

|                                                              |               |        |         | SI    | ZE    | COL   | E IDE | NT. N | 0.  |      |                                   | DW               | G NO. |       |        |            |            |       |         |        |       |    |

|                                                              |               |        |         | /     | 4     |       |       | 162   | 236 |      |                                   |                  |       |       | \      | <b>/62</b> | <u>/13</u> | 62    | 6       |        |       |    |

|                                                              |               |        |         | REV   | ,     |       |       |       |     |      |                                   | DAC              | E 1   | 05    | 24     |            |            |       |         |        |       |    |

|                                                              |               |        |         | KEV   | 1     |       |       |       |     |      |                                   | PAC              | )C    | OF    | 24     |            |            |       |         |        |       |    |

AMSC N/A 5962-V076-13

### 1. SCOPE

- 1.1 <u>Scope</u>. This drawing documents the general requirements of a high performance 1.2 GHz clock fanout buffer microcircuit, with an operating temperature range of -55°C to +105°C.

- 1.2 <u>Vendor Item Drawing Administrative Control Number</u>. The manufacturer's PIN is the item of identification. The vendor item drawing establishes an administrative control number for identifying the item on the engineering documentation:

V62/13626

01

X

E

Drawing number

Device type (See 1.2.1)

Case outline (See 1.2.2)

Lead finish (See 1.2.3)

1.2.1 Device type(s).

Device type Generic Circuit function

O1 AD9508-EP 1.2 GHz clock fanout buffer

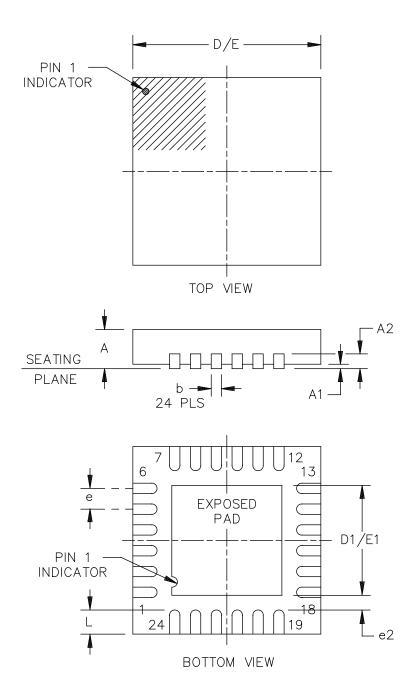

1.2.2 <u>Case outline(s)</u>. The case outline(s) are as specified herein.

Outline letter

Number of pins

JEDEC PUB 95

Package style

X

24

MO-220-WGGD

Quad lead frame chip scale package

1.2.3 Lead finishes. The lead finishes are as specified below or other lead finishes as provided by the device manufacturer:

Finish designator

A Hot solder dip

B Tin-lead plate

C Gold plate

D Palladium

E Gold flash palladium

Z Other

| DLA LAND AND MARITIME | SIZE     | CODE IDENT NO. | DWG NO.          |

|-----------------------|----------|----------------|------------------|

| COLUMBUS, OHIO        | <b>A</b> | <b>16236</b>   | <b>V62/13626</b> |

|                       |          | REV            | PAGE 2           |

## 1.3 Absolute maximum ratings. 1/

| Supply voltage (V <sub>DD</sub> )             | 3.6 V                             |

|-----------------------------------------------|-----------------------------------|

| Maximum digital input voltage                 | -0.5 V to V <sub>DD</sub> + 0.5 V |

| CLK to CLK                                    | -0.5 V to V <sub>DD</sub> + 0.5 V |

| Maximum digital output voltage                | -0.5 V to V <sub>DD</sub> + 0.5 V |

| Storage temperature range (T <sub>STG</sub> ) | -65°C to +150°C                   |

| Lead temperature (soldering, 10 seconds)      | +300°C                            |

| Junction temperature range (T <sub>J</sub> )  | +150°C                            |

| Recommended operating conditions. 2/          |                                   |

| Supply voltage (Vnn)                          | 2.5 V                             |

# 1.4

| Supply voltage (V <sub>DD</sub> )             | 2.5 V           |

|-----------------------------------------------|-----------------|

| Operating temperature range (T <sub>A</sub> ) | -55°C to +105°C |

#### 1.5 Thermal characteristics.

| Thermal characteristic 3/                                                                           | Symbol                   | Limit <u>4</u> / | Unit |

|-----------------------------------------------------------------------------------------------------|--------------------------|------------------|------|

| Thermal resistance, junction-to-ambient per JEDEC JESD51-2 (still air)                              | θЈА                      | 43.5             | °C/W |

| Thermal resistance, junction-to-ambient , 1.0 m/second airflow per JEDEC JESD51-6 (moving air)      | $_{\sf AML}_{\sf 	heta}$ | 40               | °C/W |

| Thermal resistance, junction-to-ambient,<br>2.5 m/second airflow per JEDEC JESD51-6<br>(moving air) | θJMA                     | 38.5             | °C/W |

| Thermal resistance, junction-to-board per JEDEC JESD51-8 (still air)                                | θЈВ                      | 16.2             | °C/W |

| Junction to case thermal resistance (die-to-heat sink) per MIL-STD-883, method 1012                 | θЈС                      | 7.1              | °C/W |

| Characterization parameter, junction-to-top of package per JEDEC JESD51-2 (still air)               | ΨJT                      | 0.33             | °C/W |

Results are from simulations. The printed circuit board (PCB) is a JEDEC multilayer type. Thermal performance for actual applications requires careful inspection of the conditions in the application to determine whether they are similar to those assumed in these calculations.

| DLA LAND AND MARITIME | SIZE | CODE IDENT NO. | DWG NO.          |

|-----------------------|------|----------------|------------------|

| COLUMBUS, OHIO        | A    | <b>16236</b>   | <b>V62/13626</b> |

|                       |      | REV            | PAGE 3           |

Stresses beyond those listed under "absolute maximum rating" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated under "recommended operating conditions" is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

Use of this product beyond the manufacturers design rules or stated parameters is done at the user's risk. The manufacturer and/or distributor maintain no responsibility or liability for product used beyond the stated limits.

The exposed pad on the bottom of the package must be soldered to ground (VSS) to achieve the specified thermal performance.

## 2. APPLICABLE DOCUMENTS

JEDEC Solid State Technology Association

EIA/JESD 51-2a - Integrated Circuits Thermal Test Method Environment Conditions – Natural Convection (Still Air)

EIA/JEDEC 51-6 - Integrated Circuit Thermal Test Method Environmental Conditions – Forced Convection (Moving Air)

EIA/JESD 51-8 - Integrated Circuits Thermal Test Method Environment Conditions – Junction-to-Board

JEDEC PUB 95 - Registered and Standard Outlines for Semiconductor Devices

(Applications for copies should be addressed to the Electronic Industries Alliance, 2500 Wilson Boulevard, Arlington, VA 22201-3834 or online at http://www.jedec.org)

#### DEPARTMENT OF DEFENSE STANDARDS

MIL-STD-883 - Test Method Standard Microcircuits.

(Copies of these documents are available online at <a href="http://quicksearch.dla.mil">http://quicksearch.dla.mil</a> or from the Standardization Document Order Desk, 700 Robbins Avenue, Building 4D, Philadelphia, PA 19111-5094.)

### 3. REQUIREMENTS

- 3.1 <u>Marking</u>. Parts shall be permanently and legibly marked with the manufacturer's part number as shown in 6.3 herein and as follows:

- A. Manufacturer's name, CAGE code, or logo

- B. Pin 1 identifier

- C. ESDS identification (optional)

- 3.2 <u>Unit container</u>. The unit container shall be marked with the manufacturer's part number and with items A and C (if applicable) above.

- 3.3 <u>Electrical characteristics</u>. The maximum and recommended operating conditions and electrical performance characteristics are as specified in 1.3, 1.4, and table I herein.

- 3.4 <u>Design, construction, and physical dimension</u>. The design, construction, and physical dimensions are as specified herein.

- 3.5 Diagrams.

- 3.5.1 <u>Case outline</u>. The case outline shall be as shown in 1.2.2 and figure 1.

- 3.5.2 <u>Terminal connections</u>. The terminal connections shall be as shown in figure 2.

| DLA LAND AND MARITIME | SIZE | CODE IDENT NO. | DWG NO.          |

|-----------------------|------|----------------|------------------|

| COLUMBUS, OHIO        | A    | <b>16236</b>   | <b>V62/13626</b> |

|                       |      | REV            | PAGE 4           |

TABLE I. Electrical performance characteristics. 1/

| Test                                                         | Symbol      | Conditions 2/                                                                                          | Temperature,<br>T <sub>A</sub> | Device<br>type | Lir                                     | nits   | Unit |  |

|--------------------------------------------------------------|-------------|--------------------------------------------------------------------------------------------------------|--------------------------------|----------------|-----------------------------------------|--------|------|--|

|                                                              |             |                                                                                                        |                                |                | Min                                     | Max    |      |  |

| Power supply current and                                     | d temperatu | re conditions.                                                                                         |                                |                |                                         |        |      |  |

| Supply voltage                                               | VS          |                                                                                                        | -55°C to +105°C                | 01             | 2.375                                   | 2.625  | V    |  |

|                                                              |             |                                                                                                        | +25°C                          |                | 2.5 t                                   | ypical |      |  |

| Current consumption.                                         | •           |                                                                                                        |                                | 1              |                                         |        | 1    |  |

| Low voltage differential                                     |             | Input clock at 1200 MHz, differential                                                                  | -55°C to +105°C                | 01             |                                         | 148    | mA   |  |

| signaling (LVDS) configuration                               |             | mode; all LVDS output drivers at 1200 MHz                                                              | +25°C                          |                | 132 t                                   | ypical |      |  |

|                                                              |             | Input clock at 800 MHz, differential                                                                   | -55°C to +105°C                |                |                                         | 108    |      |  |

|                                                              |             | mode; all LVDS output drivers at 200 MHz                                                               | +25°C                          |                | 2.375 2.625 2.5 typical 148 132 typical |        |      |  |

| High speed transceiver                                       |             | Input clock at 1200 MHz, differential                                                                  | -55°C to +105°C                | 01             |                                         | 175    | mA   |  |

| logic (HSTL)<br>configuration                                |             | mode; all HSTL output drivers at 1200 MHz                                                              | +25°C                          |                |                                         |        |      |  |

|                                                              |             | Input clock at 491.52 MHz,                                                                             | -55°C to +105°C                |                |                                         | 136    |      |  |

|                                                              |             | differential mode; all HSTL output<br>drivers at 491.52 MHz                                            | +25°C                          |                | 121 t                                   | ypical |      |  |

|                                                              |             | Input clock at 122.88 MHz,                                                                             | -55°C to +105°C                |                |                                         | 96     |      |  |

|                                                              |             | differential mode; all HSTL output drivers at 122.88 MHz                                               | +25°C                          |                | 86 ty                                   | /pical |      |  |

| Complementary metal oxide semiconductor (CMOS) configuration |             | Input clock at 1200 MHz, differential mode; all CMOS output drivers at 200 MHz, C <sub>L</sub> = 10 pF | -55°C to +105°C                | 01             |                                         | 159    | mA   |  |

|                                                              |             |                                                                                                        | +25°C                          |                | 142 t                                   | ypical |      |  |

|                                                              |             | Input clock at 800 MHz, differential                                                                   | -55°C to +105°C                |                |                                         | 132    |      |  |

|                                                              |             | mode; all CMOS output drivers at 200 MHz, C <sub>L</sub> = 10 pF                                       | +25°C                          |                | 118 t                                   | ypical |      |  |

|                                                              |             | Input clock at 100 MHz, differential                                                                   | -55°C to +105°C                |                |                                         | 85     |      |  |

|                                                              |             | mode; all CMOS output drivers at 100 MHz, C <sub>L</sub> = 10 pF                                       | +25°C                          | 1              | 76 ty                                   | /pical |      |  |

| Full power down                                              |             |                                                                                                        | -55°C to +105°C                | 01             |                                         | 8      | mA   |  |

|                                                              |             |                                                                                                        | +25°C                          | 1              | 4.6 t                                   | ypical | 1    |  |

| DLA LAND AND MARITIME | SIZE | CODE IDENT NO. | DWG NO.          |

|-----------------------|------|----------------|------------------|

| COLUMBUS, OHIO        | A    | <b>16236</b>   | <b>V62/13626</b> |

|                       |      | REV            | PAGE 5           |

TABLE I. <u>Electrical performance characteristics</u> – Continued. <u>1</u>/

| Test                               | Symbol          | Conditions 2/                                                                                                                     | Temperature,<br>T <sub>A</sub> | Device<br>type | Lin    | nits    | Unit             |

|------------------------------------|-----------------|-----------------------------------------------------------------------------------------------------------------------------------|--------------------------------|----------------|--------|---------|------------------|

|                                    |                 |                                                                                                                                   |                                |                | Min    | Max     |                  |

| Power supply current and           | d temperatu     | ure conditions - continued.                                                                                                       |                                |                |        |         |                  |

| Temperature.                       |                 |                                                                                                                                   |                                |                |        |         |                  |

| Ambient temperature range          | T <sub>A</sub>  |                                                                                                                                   |                                | 01             | -55    | +105    | °C               |

|                                    |                 |                                                                                                                                   |                                |                | +25 t  | ypical  |                  |

| Junction temperature               | TJ              | Junction temperature above 115°C can degrade performance, but no damage should occur unless the absolute temperature is exceeded. |                                | 01             |        | 135     | °C               |

| Clock input and output de          | c specificati   | ons.                                                                                                                              |                                |                |        |         |                  |

| Clocks inputs (Differentia         | al mode).       |                                                                                                                                   |                                |                |        |         |                  |

| Input frequency                    | f <sub>IN</sub> | Differential input                                                                                                                | -55°C to +105°C                | 01             | 0      | 1200    | MHz              |

| Input sensitivity                  |                 | As measured with a differential probe; jitter performance improves with higher slew rates (greater voltage swing)                 | -55°C to +105°C                | 01             | 360    | 2200    | mV <sub>PP</sub> |

| Input common mode voltage          | VICM            | Input pins are internally self biased, which enables ac coupling                                                                  | -55°C to +105°C                | 01             | 0.95   | 1.15    | V                |

| voltage                            |                 | which chables ac coupling                                                                                                         | +25°C                          |                | 1.05 1 | typical |                  |

| Input voltage offset               | V <sub>IO</sub> |                                                                                                                                   | +25°C                          | 01             | 30 ty  | /pical  | mV               |

| DC coupled input common mode range | VCMR            | Allowable common mode voltage range when dc coupled                                                                               | -55°C to +105°C                | 01             | 0.58   | 1.67    | V                |

| Pulse width low                    | tpWL            |                                                                                                                                   | -55°C to +105°C                | 01             | 417    |         | ps               |

| Pulse width high                   | tpWH            |                                                                                                                                   | -55°C to +105°C                | 01             | 417    |         | ps               |

| Input resistance (differential)    | R <sub>IN</sub> |                                                                                                                                   | -55°C to +105°C                | 01             | 5.0    | 9       | kΩ               |

| (umerential)                       |                 |                                                                                                                                   | +25°C                          | 1              | 7 ty   | pical   | =                |

| Input capacitance                  | C <sub>IN</sub> |                                                                                                                                   | +25°C                          | 01             | 2 ty   | pical   | pF               |

| Input bias current (each pin)      | I <sub>IB</sub> | Full input swing                                                                                                                  | -55°C to +105°C                | 01             | 100    | 400     | μА               |

| DLA LAND AND MARITIME | SIZE | CODE IDENT NO. | DWG NO.          |

|-----------------------|------|----------------|------------------|

| COLUMBUS, OHIO        | A    | <b>16236</b>   | <b>V62/13626</b> |

|                       |      | REV            | PAGE 6           |

TABLE I. Electrical performance characteristics – Continued.  $\underline{1}/$

| Test                              | Symbol                             | Conditions 2/                                                                                                                        | Temperature,    | Device<br>type |                          |         | Unit |

|-----------------------------------|------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------|-----------------|----------------|--------------------------|---------|------|

|                                   |                                    |                                                                                                                                      |                 |                | Min                      | Max     |      |

| Clock input and output            | dc specificati                     | ons – continued.                                                                                                                     |                 |                |                          |         |      |

| CMOS clock mode sing              | gle ended.                         |                                                                                                                                      |                 |                |                          |         |      |

| Input frequency                   | f <sub>IN</sub>                    |                                                                                                                                      | -55°C to +105°C | 01             |                          | 250     | MHz  |

| Input voltage high                | VIH                                |                                                                                                                                      | -55°C to +105°C | 01             | V <sub>DD</sub><br>- 0.4 |         | V    |

| Input voltage low                 | VIL                                |                                                                                                                                      | -55°C to +105°C | 01             |                          | 0.4     | V    |

| Input current high                | linh                               |                                                                                                                                      | +25°C           | 01             | 1 ty                     | pical   | μА   |

| Input current low                 | I <sub>INL</sub>                   |                                                                                                                                      | +25°C           | 01             | -142                     | typical | μА   |

| Input capacitance                 | C <sub>IN</sub>                    |                                                                                                                                      | +25°C           | 01             | 2 ty                     | pical   | pF   |

| LVDS clock inputs. Ter            | rmination = 1                      | $00 \Omega$ differential (OUTx, $\overline{\text{OUTx}}$ ).                                                                          |                 | •              | 1                        |         |      |

| Output frequency                  | four                               |                                                                                                                                      | -55°C to +105°C | 01             |                          | 1200    | MHz  |

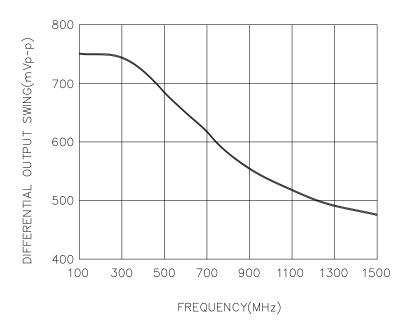

| Differential output voltage       | V <sub>OD</sub>                    | V <sub>OH</sub> – V <sub>OL</sub> measurement across a differential pair at the default                                              | -55°C to +105°C | 01             | 247                      | 454     | mV   |

|                                   |                                    | amplitude settling with output driver not toggling; see figure 3 for variation over frequency.                                       | +25°C           |                | 375 t                    | ypical  |      |

| Delta differential output voltage | ΔV <sub>OD</sub>                   | Absolute value of the difference between V <sub>OD</sub> when the normal output is high versus when the complementary output is high | -55°C to +105°C | 01             |                          | 50      | mV   |

| Offset voltage                    | Vos                                | (V <sub>OH</sub> + V <sub>OL</sub> ) / 2 across a                                                                                    | -55°C to +105°C | 01             | 1.125                    | 1.375   | V    |

|                                   |                                    | differential pair                                                                                                                    | +25°C           |                | 1.18                     | typical |      |

| Delta offset voltage              | ΔVOS                               | Absolute value of the difference between VOS when the normal output is high versus when the complementary output is high.            | -55°C to +105°C | 01             |                          | 50      | mV   |

| Short circuit current             | I <sub>S</sub> A, I <sub>S</sub> B | Each pin (output shorted to GND)                                                                                                     | -55°C to +105°C | 01             |                          | 24      | mA   |

|                                   |                                    |                                                                                                                                      | +25°C           | 1              | 13.6                     | typical |      |

| LVDS duty cycle                   |                                    | Up to 750 MHz input                                                                                                                  | -55°C to +105°C | 01             | 45                       | 55      | %    |

|                                   |                                    | 750 MHz to 1200 MHz input                                                                                                            |                 |                | 39                       | 61      |      |

| DLA LAND AND MARITIME | SIZE | CODE IDENT NO. | DWG NO.          |

|-----------------------|------|----------------|------------------|

| COLUMBUS, OHIO        | A    | <b>16236</b>   | <b>V62/13626</b> |

|                       |      | REV            | PAGE 7           |

TABLE I. <u>Electrical performance characteristics</u> – Continued. <u>1</u>/

| Test                        | Symbol          | Symbol Conditions $\underline{2}/$ Temperature, $T_A$                 |                                               | Device<br>type | Lir   | nits   | Unit |  |

|-----------------------------|-----------------|-----------------------------------------------------------------------|-----------------------------------------------|----------------|-------|--------|------|--|

|                             |                 |                                                                       |                                               |                | Min   | Max    |      |  |

| Clock input and output d    | lc specificati  | ons – continued.                                                      |                                               |                |       |        |      |  |

| HSTL clock inputs. Terr     | mination = 1    | 00 $\Omega$ differential; default amplitude setti                     | ng.                                           |                |       |        |      |  |

| Output frequency            | fout            |                                                                       | -55°C to +105°C                               | 01             |       | 1200   | MHz  |  |

| Differential output voltage | Vo              | VOH - VOL with output driver static                                   | L with output driver static -55°C to +105°C 0 | 01             | 859   | 978    | mV   |  |

|                             |                 |                                                                       | +25°C                                         |                | 925 t | ypical |      |  |

| Common mode output voltage  | Vocm            | (V <sub>OH</sub> + V <sub>OL</sub> )/2 with output driver             | -55°C to +105°C                               | 01             | 905   | 971    | mV   |  |

| vollage                     |                 | static                                                                | +25°C                                         |                | 940 t |        | -    |  |

| HSTL duty cycle             |                 | Up to 750 MHz input                                                   | -55°C to +105°C                               | 01             | 45    | 55     | %    |  |

|                             |                 | 750 MHz to 1200 MHz input                                             |                                               |                | 40    | 60     |      |  |

| CMOS clock outputs. S       | ingle ended;    | termination = open; OUTx and $\overline{\text{OUTx}}$                 | in phase.                                     |                |       |        |      |  |

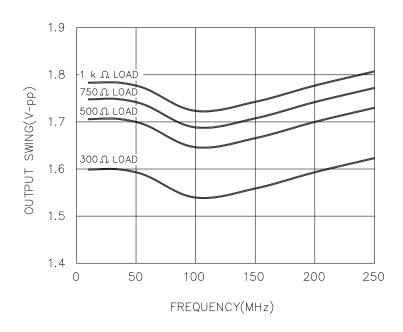

| Output frequency            | fout            | 10 pF load per output; see figure 4 for output swing versus frequency | -55°C to +105°C                               | 01             |       | 250    | MHz  |  |

| Output voltage              | Voн             | 1 mA load                                                             | -55°C to +105°C                               | 01             | 1.7   |        | V    |  |

|                             | V <sub>OL</sub> |                                                                       |                                               |                |       | 0.1    |      |  |

|                             | V <sub>OH</sub> | 10 mA load                                                            |                                               |                |       | 1.2    |      |  |

| V <sub>OI</sub>             | V <sub>OL</sub> |                                                                       |                                               |                |       | 0.6    |      |  |

|                             | Voh             | 10 mA load (2 x CMOS mode)                                            |                                               |                | 1.45  |        |      |  |

|                             | V <sub>OL</sub> |                                                                       |                                               |                |       | 0.35   |      |  |

| CMOS duty cycle             |                 | Up to 250 MHz                                                         | -55°C to +105°C                               | 01             | 45    | 55     | %    |  |

| DLA LAND AND MARITIME | SIZE | CODE IDENT NO. | DWG NO.          |

|-----------------------|------|----------------|------------------|

| COLUMBUS, OHIO        | A    | <b>16236</b>   | <b>V62/13626</b> |

|                       |      | REV            | PAGE 8           |

TABLE I. <u>Electrical performance characteristics</u> – Continued. <u>1</u>/

| Test                                                                     | Symbol                          | Conditions 2/                                                                                                            | Temperature,<br>T <sub>A</sub> | Device<br>type | Lin          | nits   | Unit  |  |

|--------------------------------------------------------------------------|---------------------------------|--------------------------------------------------------------------------------------------------------------------------|--------------------------------|----------------|--------------|--------|-------|--|

|                                                                          |                                 |                                                                                                                          |                                |                |              | Min    | Max   |  |

| Output driver timing char                                                | acteristics.                    |                                                                                                                          |                                |                |              |        |       |  |

| LVDS outputs. Terminat                                                   | $ion = 100 \Omega$              | differential, 1 X LVDS.                                                                                                  |                                |                |              |        |       |  |

| Output rise/fall time                                                    | t <sub>R</sub> , t <sub>F</sub> | 20% x 80% measured differentially                                                                                        | -55°C to +105°C                | 01             |              | 192    | ps    |  |

|                                                                          |                                 |                                                                                                                          | +25°C                          |                | 152 t        | ypical |       |  |

| Propagation delay, clock to LVDS output                                  | t <sub>PD</sub>                 |                                                                                                                          | -55°C to +105°C                | 01             | 1.52         | 2.49   | ns    |  |

| Clock to EVD3 output                                                     |                                 |                                                                                                                          | +25°C                          |                | 2.01 t       | ypical |       |  |

| Propagation delay,<br>clock to LVDS output<br>temperature<br>coefficient | t <sub>PD</sub>                 |                                                                                                                          | +25°C                          | 01             | 2.8 typical  |        | ps/°C |  |

| Output skew, all LVDS o                                                  | utputs. 3/                      |                                                                                                                          |                                | •              |              |        | •     |  |

| On the same part                                                         |                                 |                                                                                                                          | -55°C to +105°C                | 01             |              | 48     | ps    |  |

| Across multiple parts                                                    |                                 | Assumes same temperature and supply; takes into account worst case propagation delay due to worst case process variation | -55°C to +105°C                | 01             |              | 781    | ps    |  |

| HSTL outputs. Terminat                                                   | ion = 100 Ω                     | differential, 1 X HSTL.                                                                                                  |                                | •              |              | •      | •     |  |

| Output rise/fall time                                                    | t <sub>R</sub> , t <sub>F</sub> | 20% x 80% measured differentially                                                                                        | -55°C to +105°C                | 01             |              | 154    | ps    |  |

|                                                                          |                                 |                                                                                                                          | +25°C                          |                | 118 t        | ypical |       |  |

| Propagation delay,<br>clock to HSTL output                               | t <sub>PD</sub>                 |                                                                                                                          | -55°C to +105°C                | 01             | 1.55         | 2.56   | ns    |  |

| Clock to H312 output                                                     |                                 |                                                                                                                          | +25°C                          |                | 2.05 typical |        |       |  |

| Propagation delay,<br>clock to HSTL output<br>temperature<br>coefficient | t <sub>PD</sub>                 |                                                                                                                          | +25°C                          | 01             | 2.9 typical  |        | ps/°C |  |

| Output skew, all HSTL of                                                 | utputs. <u>3</u> /              |                                                                                                                          |                                |                |              |        |       |  |

| On the same part                                                         |                                 |                                                                                                                          | -55°C to +105°C                | 01             |              | 59     | ps    |  |

| Across multiple parts                                                    |                                 | Assumes same temperature and supply; takes into account worst case propagation delay due to worst case process variation | -55°C to +105°C                | 01             |              | 825    | ps    |  |

| DLA LAND AND MARITIME | SIZE | CODE IDENT NO. | DWG NO.          |

|-----------------------|------|----------------|------------------|

| COLUMBUS, OHIO        | A    | <b>16236</b>   | <b>V62/13626</b> |

|                       |      | REV            | PAGE 9           |

TABLE I. <u>Electrical performance characteristics</u> – Continued. <u>1</u>/

| Test                                                                     | Symbol                          | conditions <u>2</u> /                                                                                                    | Temperature,    | Device<br>type | Lin         | nits    | Unit  |

|--------------------------------------------------------------------------|---------------------------------|--------------------------------------------------------------------------------------------------------------------------|-----------------|----------------|-------------|---------|-------|

|                                                                          |                                 |                                                                                                                          |                 |                | Min         | Max     |       |

| Output driver timing char                                                | acteristics -                   | continued.                                                                                                               |                 |                |             |         |       |

| CMOS outputs.                                                            |                                 |                                                                                                                          |                 |                |             |         |       |

| Output rise/fall time $t_R$ , $t_F$                                      | t <sub>R</sub> , t <sub>F</sub> | t <sub>F</sub> 20% x 80%, C <sub>L</sub> = 10 pF                                                                         | -55°C to +105°C | 01             |             | 1.47    | ps    |

|                                                                          |                                 |                                                                                                                          | +25°C           |                | 1.181       | typical |       |

| Propagation delay,<br>clock to CMOS output                               | t <sub>PD</sub>                 | 10 pF load                                                                                                               | -55°C to +105°C | 01             | 1.98        | 3.14    | ns    |

| Clock to CIMOS output                                                    |                                 |                                                                                                                          | +25°C           |                | 2.56        | ypical  |       |

| Propagation delay,<br>clock to CMOS output<br>temperature<br>coefficient | tPD                             |                                                                                                                          | +25°C           | 01             | 3.3 typical |         | ps/°C |

| Output skew, all CMOS of                                                 | outputs. 3/                     |                                                                                                                          |                 |                |             |         |       |

| On the same part                                                         |                                 |                                                                                                                          | -55°C to +105°C | 01             |             | 112     | ps    |

| Across multiple parts                                                    |                                 | Assumes same temperature and supply; takes into account worst case propagation delay due to worst case process variation | -55°C to +105°C | 01             |             | 965     | ps    |

| Output logic skew. 3/ C                                                  | MOS load =                      | = 10 pF and LVDS load = 100 $\Omega$ .                                                                                   |                 | •              |             | •       | •     |

| LVDS outputs and                                                         |                                 | Outputs on the same device;                                                                                              | -55°C to +105°C | 01             |             | 119     | ps    |

| HSTL outputs                                                             |                                 | assumes worst case output combination                                                                                    | +25°C           |                | 77 ty       | /pical  |       |

| LVDS outputs and                                                         |                                 | Outputs on the same device;                                                                                              | -55°C to +105°C | 01             |             | 708     | ps    |

| CMOS outputs                                                             |                                 | assumes worst case output combination                                                                                    | +25°C           |                | 497 t       | ypical  |       |

| HSTL outputs and                                                         |                                 | Outputs on the same device;                                                                                              | -55°C to +105°C | 01             |             | 628     | ps    |

| CMOS outputs assumes worst case output combination                       |                                 | +25°C                                                                                                                    |                 | 424 typical    |             | 1       |       |

| DLA LAND AND MARITIME | SIZE | CODE IDENT NO. | DWG NO.          |

|-----------------------|------|----------------|------------------|

| COLUMBUS, OHIO        | A    | <b>16236</b>   | <b>V62/13626</b> |

|                       |      | REV            | PAGE 10          |

TABLE I. Electrical performance characteristics – Continued.  $\underline{1}/$

| Test                      | Symbol                                 | Conditions 2/                           | Temperature,    | Device<br>type | Lin                      | nits   | Unit  |       |       |       |       |       |       |       |    |       |       |    |

|---------------------------|----------------------------------------|-----------------------------------------|-----------------|----------------|--------------------------|--------|-------|-------|-------|-------|-------|-------|-------|-------|----|-------|-------|----|

|                           |                                        |                                         | ^               |                | Min                      | Max    |       |       |       |       |       |       |       |       |    |       |       |    |

| Logic inputs.             |                                        |                                         | ·               |                |                          |        |       |       |       |       |       |       |       |       |    |       |       |    |

| Logic inputs. (RESE1      | T, SYNC, IN_                           | _SEL).                                  |                 |                |                          |        |       |       |       |       |       |       |       |       |    |       |       |    |

| Input high voltage        | VIH                                    | 2.5 V supply voltage operation          | -55°C to +105°C | 01             | 1.7                      |        | V     |       |       |       |       |       |       |       |    |       |       |    |

| Input low voltage         | VIL                                    | 2.5 V supply voltage operation          | -55°C to +105°C | 01             |                          | 0.7    | V     |       |       |       |       |       |       |       |    |       |       |    |

| Input current             | I <sub>INH</sub> ,<br>I <sub>INL</sub> |                                         | -55°C to +105°C | 01             | -300                     | 100    | μА    |       |       |       |       |       |       |       |    |       |       |    |

| Input capacitance         | C <sub>IN</sub>                        |                                         | +25°C           | 01             | 2 ty                     | pical  | pF    |       |       |       |       |       |       |       |    |       |       |    |

| Serial port specification | n. Serial perip                        | pheral interface (SPI) mode.            | 1               |                |                          |        |       |       |       |       |       |       |       |       |    |       |       |    |

| Chip select (CS).         | S has an inter                         | nal 35 k $\Omega$ pull up resistor.     |                 |                |                          |        |       |       |       |       |       |       |       |       |    |       |       |    |

| Input voltage             | V <sub>IN</sub>                        | Logic 1                                 | -55°C to +105°C | 01             | V <sub>DD</sub><br>- 0.4 |        | ٧     |       |       |       |       |       |       |       |    |       |       |    |

|                           |                                        | Logic 0                                 |                 |                |                          | 0.4    | 1     |       |       |       |       |       |       |       |    |       |       |    |

| Input current             | I <sub>IN</sub>                        | Logic 1                                 | +25°C           | 01             | -4 ty                    | pical  | μА    |       |       |       |       |       |       |       |    |       |       |    |

|                           |                                        | Logic 0                                 |                 |                | -85 typical              |        |       |       |       |       |       |       |       |       |    |       |       |    |

| Input capacitance         | C <sub>IN</sub>                        |                                         | +25°C           | 01             | 2 ty                     | pical  | pF    |       |       |       |       |       |       |       |    |       |       |    |

| Serial clock (SCLK).      | SCLK has an i                          | nternal 35 k $\Omega$ pull up resistor. | 1               | l .            |                          |        |       |       |       |       |       |       |       |       |    |       |       |    |

| Input voltage             | VIN                                    | Logic 1                                 | -55°C to +105°C | 01             | V <sub>DD</sub><br>- 0.4 |        | V     |       |       |       |       |       |       |       |    |       |       |    |

|                           |                                        | Logic 0                                 |                 |                |                          | 0.4    | 1     |       |       |       |       |       |       |       |    |       |       |    |

| Input current             | I <sub>IN</sub>                        | Logic 1                                 | +25°C           | +25°C          | +25°C                    | +25°C  | +25°C | +25°C | +25°C | +25°C | +25°C | +25°C | +25°C | +25°C | 01 | 70 ty | pical | μА |

|                           |                                        | Logic 0                                 |                 |                | 13 ty                    | /pical | 1     |       |       |       |       |       |       |       |    |       |       |    |

| Input capacitance         | C <sub>IN</sub>                        |                                         | +25°C           | 01             | 2 ty                     | pical  | pF    |       |       |       |       |       |       |       |    |       |       |    |

| DLA LAND AND MARITIME | SIZE | CODE IDENT NO. | DWG NO.          |

|-----------------------|------|----------------|------------------|

| COLUMBUS, OHIO        | A    | <b>16236</b>   | <b>V62/13626</b> |

|                       |      | REV            | PAGE 11          |

TABLE I.  $\underline{\text{Electrical performance characteristics}}$  – Continued.  $\underline{1}/$

| Test                        | Symbol             | Conditions 2/              | Temperature,    | Device<br>type | Lin                      | nits  | Unit |

|-----------------------------|--------------------|----------------------------|-----------------|----------------|--------------------------|-------|------|

|                             |                    |                            | , ,             |                | Min                      | Max   |      |

| Serial port specification - | - continued        | . SPI mode.                |                 |                |                          |       |      |

| Serial data input and out   | put (SDIO)         | (input).                   |                 |                |                          |       |      |

| Input voltage               | V <sub>IN</sub>    | Logic 1                    | -55°C to +105°C | 01             | V <sub>DD</sub><br>- 0.4 |       | V    |

|                             |                    | Logic 0                    |                 |                |                          | 0.4   |      |

| Input current               | I <sub>IN</sub>    | Logic 1                    | +25°C           | 01             | -1 ty                    | pical | μА   |

|                             |                    | Logic 0                    |                 |                | -1 ty                    | pical | 1    |

| Input capacitance           | C <sub>IN</sub>    |                            | +25°C           | 01             | 2 ty                     | pical | pF   |

| Serial data input and out   | put (SDIO)         | output.                    |                 | l              | l                        |       |      |

| Output voltage              | Vout               | Logic 1, 1 mA load current | -55°C to +105°C | 01             | V <sub>DD</sub><br>- 0.4 |       | V    |

|                             |                    | Logic 0, 1 ma load current |                 |                |                          | 0.4   |      |

| Serial data output (SDO)    | output.            |                            | ·               |                |                          |       |      |

| Output voltage              | Vout               | Logic 1, 1 mA load current | -55°C to +105°C | 01             | V <sub>DD</sub><br>- 0.4 |       | V    |

|                             |                    | Logic 0, 1 mA load current |                 |                |                          | 0.4   | 1    |

| Timing.                     |                    |                            |                 |                |                          |       |      |

| SCLK clock rate             | 1/t <sub>CLK</sub> |                            | -55°C to +105°C | 01             |                          | 30    | MHz  |

| SCLK pulse width high       | tHIGH              |                            | -55°C to +105°C | 01             | 4.6                      |       | ns   |

| SCLK pulse width low        | t <sub>LOW</sub>   |                            | -55°C to +105°C | 01             | 3.5                      |       | ns   |

| SDIO to SCLK setup          | t <sub>DS</sub>    |                            | -55°C to +105°C | 01             | 2.9                      |       | ns   |

| SCLK to SDIO hold           | tDH                |                            | -55°C to +105°C | 01             | 0                        |       | ns   |

| SCLK to valid SDIO and SDO  | t <sub>DV</sub>    |                            | -55°C to +105°C | 01             |                          | 15    | ns   |

| CS to SCLK setup            | tS                 |                            | -55°C to +105°C | 01             | 3.4                      |       | ns   |

| CS to SCLK hold             | t <sub>C</sub>     |                            | -55°C to +105°C | 01             | 0                        |       | ns   |

| CS minimum pulse width high |                    |                            | -55°C to +105°C | 01             | 3.4                      |       | ns   |

| DLA LAND AND MARITIME | SIZE | CODE IDENT NO. | DWG NO.          |

|-----------------------|------|----------------|------------------|

| COLUMBUS, OHIO        | A    | <b>16236</b>   | <b>V62/13626</b> |

|                       |      | REV            | PAGE 12          |

TABLE I.  $\underline{\text{Electrical performance characteristics}}$  – Continued.  $\underline{1}/$

| Test                                             | Symbol              | Conditions 2/                                         | Temperature,         | Device<br>type | Lir                      | nits | Unit |

|--------------------------------------------------|---------------------|-------------------------------------------------------|----------------------|----------------|--------------------------|------|------|

|                                                  |                     |                                                       | ^                    |                | Min                      | Max  |      |

| Serial port specifications                       | . Inter-integ       | grated circuit (I <sup>2</sup> C) mode.               |                      |                |                          |      |      |

| Serial data (SDA), serial                        | clock (SCL)         | inputs. SDA and SCL have internal 80                  | kΩ pull up resistors |                |                          |      |      |

| Input voltage                                    | VIN                 | Logic 1                                               | -55°C to +105°C      | 01             | V <sub>DD</sub><br>- 0.4 |      | V    |

|                                                  |                     | Logic 0                                               |                      |                |                          | 0.4  |      |

| Input current                                    | I <sub>IN</sub>     | V <sub>IN</sub> = 10% to 90%                          | -55°C to +105°C      | 01             | -40                      | 0    | μА   |

| Hysteresis of schmitt trigger inputs             |                     |                                                       | -55°C to +105°C      | 01             | 150                      |      | mV   |

| SDA output.                                      |                     |                                                       |                      | •              |                          | •    | •    |

| Output logic 0 voltage                           |                     | I <sub>O</sub> = 3 mA                                 | -55°C to +105°C      | 01             |                          | 0.4  | V    |

| Output fall time from VIH(MIN) to VIL(MAX)       |                     | $10 \text{ pF} \leq C_b \leq 400 \text{ pF}$          | -55°C to +105°C      | 01             |                          | 250  | ns   |

| Timing.                                          |                     |                                                       |                      | l              |                          | l    |      |

| SCL clock rate                                   |                     |                                                       | -55°C to +105°C      | 01             |                          | 400  | kHz  |

| Bus free time between a stop and start condition | tBUF                |                                                       | -55°C to +105°C      | 01             | 1.3                      |      | μs   |

| Repeated start condition setup time              | tsu;sta             |                                                       | -55°C to +105°C      | 01             |                          | 0.6  | μS   |

| Repeated start condition hold time               | t <sub>HD;STA</sub> | After this period, the first clock pulse is generated | -55°C to +105°C      | 01             | 0.6                      |      | μS   |

| Stop condition setup time                        | tsu;sto             |                                                       | -55°C to +105°C      | 01             | 0.6                      |      | μS   |

| Low period of SCL clock                          | t <sub>LOW</sub>    |                                                       | -55°C to +105°C      | 01             | 1.3                      |      | μS   |

| High period of SCL clock                         | tHIGH               |                                                       | -55°C to +105°C      | 01             | 0.6                      |      | μS   |

| Data setup time                                  | t <sub>SU;DAT</sub> |                                                       | -55°C to +105°C      | 01             | 100                      |      | ns   |

| Data hold time                                   | t <sub>HD;DAT</sub> |                                                       | -55°C to +105°C      | 01             | 0                        | 0.9  | μS   |

| DLA LAND AND MARITIME | SIZE | CODE IDENT NO. | DWG NO.          |

|-----------------------|------|----------------|------------------|

| COLUMBUS, OHIO        | A    | <b>16236</b>   | <b>V62/13626</b> |

|                       |      | REV            | PAGE 13          |

TABLE I. Electrical performance characteristics – Continued.  $\underline{1}/$

| Test                     | Symbol        | Conditions 2/                | Temperature,<br>T <sub>A</sub>           | Device<br>type | Limits      |        | Unit   |

|--------------------------|---------------|------------------------------|------------------------------------------|----------------|-------------|--------|--------|

|                          |               |                              |                                          |                | Min         | Max    |        |

| External resistor values | for pin strap | ping mode.                   |                                          |                |             |        |        |

| External resistors. Usin | g 10% tolera  | ance resistor.               |                                          |                |             |        |        |

| Voltage level 0          |               | Pull down to ground          | Pull down to ground +25°C 01 820 typical |                | ypical      | Ω      |        |

| Voltage level 1          |               | Pull down to ground          | +25°C                                    | 01             | 1.8 ty      | /pical | kΩ     |

| Voltage level 2          |               | Pull down to ground          | +25°C                                    | 01             | 3.9 ty      | /pical | kΩ     |

| Voltage level 3          |               | Pull down to ground          | +25°C                                    | 01             | 8.2 ty      | /pical | kΩ     |

| Voltage level 4          |               | Pull up to V <sub>DD</sub>   | +25°C                                    | 01             | 820 t       | ypical | Ω      |

| Voltage level 5          |               | Pull up to V <sub>DD</sub>   | +25°C                                    | 01             | 1.8 typical |        | kΩ     |

| Voltage level 6          |               | Pull up to V <sub>DD</sub>   | +25°C                                    | 01             | 3.9 typical |        | kΩ     |

| Voltage level 7          |               | Pull up to V <sub>DD</sub>   | +25°C                                    | 01             | 8.2 typical |        | kΩ     |

| Clock output additive ph | nase noise.   |                              |                                          |                |             |        |        |