|     | REVISIONS   |      |          |  |  |  |  |  |  |  |

|-----|-------------|------|----------|--|--|--|--|--|--|--|

| LTR | DESCRIPTION | DATE | APPROVED |  |  |  |  |  |  |  |

|     |             |      |          |  |  |  |  |  |  |  |

| Prepared                               | in acc                       | ordan | ce wit | h ASN             | ЛЕ Y1                                                                        | 4.24          |      |    |   |   |   |                                                                                     |            |       |       |      |             | Ve | ndor it | em dra  | awing |    |

|----------------------------------------|------------------------------|-------|--------|-------------------|------------------------------------------------------------------------------|---------------|------|----|---|---|---|-------------------------------------------------------------------------------------|------------|-------|-------|------|-------------|----|---------|---------|-------|----|

| REV                                    |                              |       |        |                   |                                                                              |               |      |    |   |   |   |                                                                                     |            |       |       |      |             |    |         |         |       |    |

| PAGE                                   |                              |       |        |                   |                                                                              |               |      |    |   |   |   |                                                                                     |            |       |       |      |             |    |         |         |       |    |

| REV                                    |                              |       |        |                   |                                                                              |               |      |    |   |   |   |                                                                                     |            |       |       |      |             |    |         |         |       |    |

| PAGE                                   | 18                           | 19    | 20     | 21                | 22                                                                           | 23            | 24   | 25 |   |   |   |                                                                                     |            |       |       |      |             |    |         |         |       |    |

| REV STA                                | TUS                          |       | REV    | ,                 |                                                                              |               |      |    |   |   |   |                                                                                     |            |       |       |      |             |    |         |         |       |    |

| OF PAGE                                | S                            |       | PAG    | E                 |                                                                              | 1             | 2    | 3  | 4 | 5 | 6 | 7                                                                                   | 8          | 9     | 10    | 11   | 12          | 13 | 14      | 15      | 16    | 17 |

| PMIC N/A                               | <b>\</b>                     |       |        |                   |                                                                              | ED BY<br>FICE |      |    |   |   |   | DLA LAND AND MARITIME COLUMBUS, OHIO 43218-3990 http://www.landandmaritime.dla.mil/ |            |       |       |      |             |    |         |         |       |    |

| Original d                             | ate of<br>′-MM-l             |       | ng     |                   | CKEI<br>JESH                                                                 | D BY<br>PITH  | ADIA |    |   |   |   | TIT                                                                                 |            | יחסוי | IIT I | INIE | <b>ND</b> ( |    | ) CU    | \ NINIE | =1    |    |

| 15-10-01 APPROVED BY CHARLES F. SAFFLE |                              |       |        |                   | - MICROCIRCUIT, LINEAR, QUAD CHANNEL<br>DIGITAL ISOLATOR, MONOLITHIC SILICON |               |      |    |   |   |   |                                                                                     |            |       |       |      |             |    |         |         |       |    |

|                                        | SIZE CODE IDENT. NO. A 16236 |       |        | DWG NO. V62/14630 |                                                                              |               |      |    |   |   |   |                                                                                     |            |       |       |      |             |    |         |         |       |    |

|                                        |                              |       |        | REV               | ′                                                                            | •             |      |    |   |   |   | PAG                                                                                 | <b>E</b> 1 | OF    | 25    |      |             |    |         |         |       |    |

AMSC N/A 5962-V102-15

## 1. SCOPE

- 1.1 <u>Scope</u>. This drawing documents the general requirements of a high performance quad channel, digital isolator microcircuit, with an operating temperature range of -55°C to +125°C.

- 1.2 <u>Vendor Item Drawing Administrative Control Number</u>. The manufacturer's PIN is the item of identification. The vendor item drawing establishes an administrative control number for identifying the item on the engineering documentation:

| V62/14630 | - | <u>01</u><br> | X<br>T       | Ę           |

|-----------|---|---------------|--------------|-------------|

| Drawing   |   | Device type   | Case outline | Lead finish |

| number    |   | (See 1.2.1)   | (See 1.2.2)  | (See 1.2.3) |

1.2.1 Device type(s).

Device typeGenericCircuit function01ADUM3401Quad channel, digital isolator

1.2.2 <u>Case outline(s)</u>. The case outline(s) are as specified herein.

| Outline letter | Number of pins | JEDEC PUB 95 | Package style               |

|----------------|----------------|--------------|-----------------------------|

| X              | 16             | MS-013-AA    | Small outline surface mount |

1.2.3 <u>Lead finishes</u>. The lead finishes are as specified below or other lead finishes as provided by the device manufacturer:

| Finish designator | <u>Material</u>      |

|-------------------|----------------------|

| Α                 | Hot solder dip       |

| В                 | Tin-lead plate       |

| С                 | Gold plate           |

| D                 | Palladium            |

| Е                 | Gold flash palladium |

| Z                 | Other                |

| DLA LAND AND MARITIME | SIZE | CODE IDENT NO. | DWG NO.          |

|-----------------------|------|----------------|------------------|

| COLUMBUS, OHIO        | A    | <b>16236</b>   | <b>V62/14630</b> |

|                       |      | REV            | PAGE 2           |

## 1.3 Absolute maximum ratings. 1/

|     | Supply voltages (V <sub>DD1</sub> , V <sub>DD2</sub> )          |                                                         |

|-----|-----------------------------------------------------------------|---------------------------------------------------------|

|     | Input voltages (VIA, VIB, VIC, VID, VE1, VE2)                   | 0.5 V to V <sub>DDI</sub> + 0.5 V <u>2</u> / <u>3</u> / |

|     | Output voltage (VOA, VOB, VOC, VOD)                             | 0.5 V to V <sub>DDO</sub> + 0.5 V <u>2</u> / <u>3</u> / |

|     | Average output current per pin: 4/                              |                                                         |

|     | Side 1 (I <sub>O1</sub> )                                       | 18 mA to +18 mA                                         |

|     | Side 2 (I <sub>O2</sub> )                                       | 22 mA to +22 mA                                         |

|     | Common mode transients (CM <sub>H</sub> , CM <sub>L</sub> )     |                                                         |

|     | Storage temperature range (T <sub>STG</sub> )                   | 65°C to +150°C                                          |

|     |                                                                 |                                                         |

| 1 1 | Pacammandad aparating conditions 6/                             |                                                         |

| 1.4 | Recommended operating conditions. 6/                            |                                                         |

|     | Supply voltages (V <sub>DD1</sub> , V <sub>DD2</sub> )          | . 3.135 V to 5.5 V 2/                                   |

|     | Input signal rise and fall times                                |                                                         |

|     | Operating temperature range (T <sub>A</sub> )                   |                                                         |

|     |                                                                 |                                                         |

| 1 5 | Daglegge characteristics                                        |                                                         |

| 1.5 | Package characteristics.                                        |                                                         |

|     | Resistance (input to output) (R <sub>IO</sub> )                 | . 10 <sup>12</sup> Ω typical <u>7</u> /                 |

|     | Capacitance (input to output) (C <sub>IO</sub> ) with f = 1 MHz |                                                         |

|     | Input capacitance (C <sub>I</sub> )                             | . 4.0 pF typical 8/                                     |

|     | Integrated circuit junction to case thermal resistance:         |                                                         |

|     | Thermocouple located at center of package underside.            |                                                         |

|     | Side 1 (θ <sub>JCI</sub> )                                      | . 33°C/W typical                                        |

|     | Side 2 (θ <sub>JCO</sub> )                                      | . 28°C/W typical                                        |

|     |                                                                 |                                                         |

<sup>8/</sup> Input capacitance is from any input data pin to ground.

| DLA LAND AND MARITIME | SIZE | CODE IDENT NO. | DWG NO.          |

|-----------------------|------|----------------|------------------|

| COLUMBUS, OHIO        | A    | <b>16236</b>   | <b>V62/14630</b> |

|                       |      | REV            | PAGE 3           |

Stresses beyond those listed under "absolute maximum rating" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated under "recommended operating conditions" is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

<sup>2/</sup> All voltages are relative to their respective ground.

<sup>3/</sup> V<sub>DDI</sub> and V<sub>DDO</sub> refer to the supply voltages on the input and output sides of a given channel, respectively.

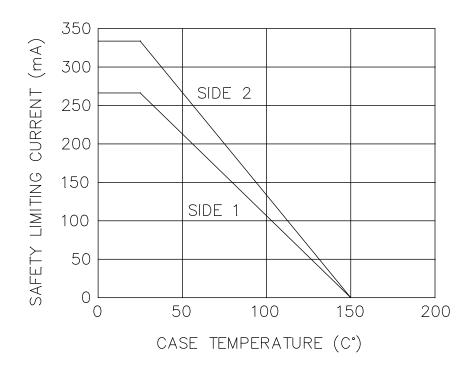

<sup>4/</sup> See figure 5 for maximum rated current values for various temperatures.

<sup>5/</sup> Refers to common mode transients across the insulation barrier. Common mode transients exceeding the absolute maximum ratings can cause latch up or permanent damage.

<sup>6/</sup> Use of this product beyond the manufacturers design rules or stated parameters is done at the user's risk. The manufacturer and/or distributor maintain no responsibility or liability for product used beyond the stated limits.

<sup>7/</sup> Device considered a 2 terminal device; V<sub>DD1</sub> pin to GND1 pin are shorted together, and GND2 pin to V<sub>DD2</sub> pin are shorted together.

#### 2. APPLICABLE DOCUMENTS

JEDEC Solid State Technology Association

JEDEC PUB 95 - Registered and Standard Outlines for Semiconductor Devices

(Copies of these documents are available online at http://www.jedec.org or from JEDEC – Solid State Technology Association, 3103 North 10th Street, Suite 240–S, Arlington, VA 22201-2107).

#### 3. REQUIREMENTS

- 3.1 <u>Marking</u>. Parts shall be permanently and legibly marked with the manufacturer's part number as shown in 6.3 herein and as follows:

- A. Manufacturer's name, CAGE code, or logo

- B. Pin 1 identifier

- C. ESDS identification (optional)

- 3.2 <u>Unit container</u>. The unit container shall be marked with the manufacturer's part number and with items A and C (if applicable) above.

- 3.3 <u>Electrical characteristics</u>. The maximum and recommended operating conditions and electrical performance characteristics are as specified in 1.3, 1.4, and table I herein.

- 3.4 Design, construction, and physical dimension. The design, construction, and physical dimensions are as specified herein.

- 3.5 Diagrams.

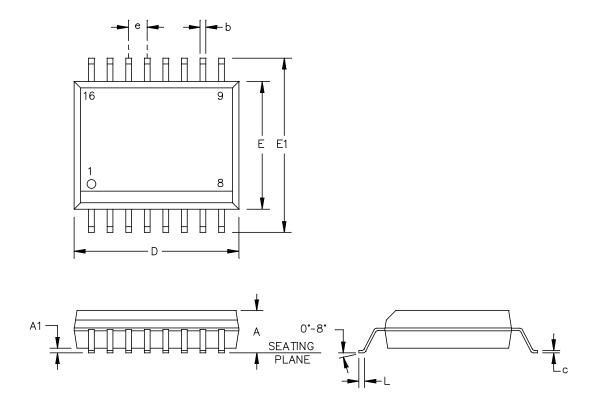

- 3.5.1 <u>Case outline</u>. The case outline shall be as shown in 1.2.2 and figure 1.

- 3.5.2 <u>Terminal connections</u>. The terminal connections shall be as shown in figure 2.

- 3.5.3 Truth table. The truth table shall be as shown in figure 3.

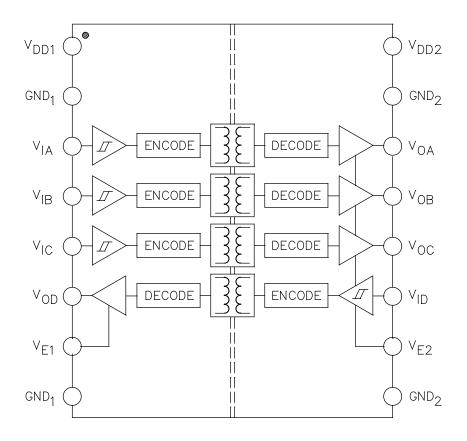

- 3.5.4 Logic diagram. The logic diagram shall be as shown in figure 4.

- 3.5.5 Thermal derating curve. The thermal derating curve shall be as shown in figure 5.

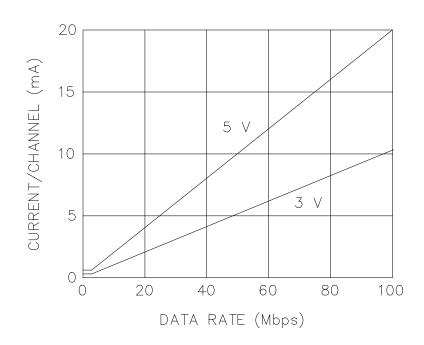

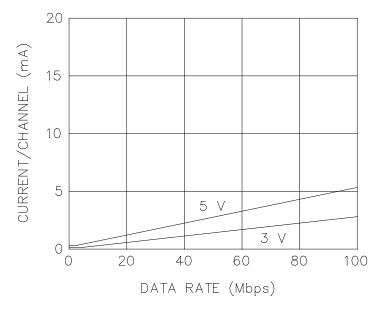

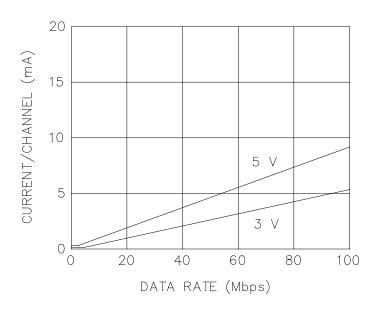

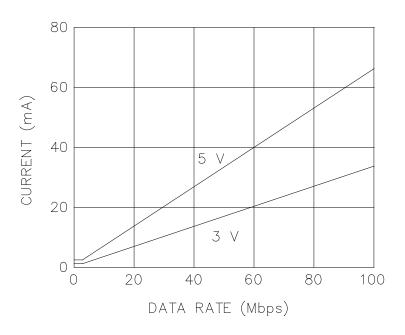

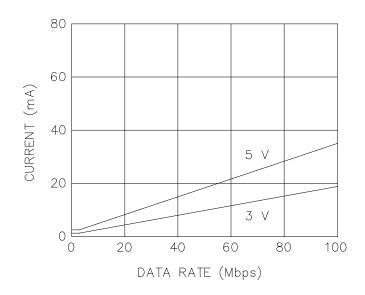

- 3.5.6 Data rate graphs. The data rate graphs shall be as shown in figures 6 through 10.

| DLA LAND AND MARITIME | SIZE | CODE IDENT NO. | DWG NO.          |

|-----------------------|------|----------------|------------------|

| COLUMBUS, OHIO        | A    | <b>16236</b>   | <b>V62/14630</b> |

|                       |      | REV            | PAGE 4           |

TABLE I. Electrical performance characteristics. 1/

| Test                               | Symbol                            | Conditions                             | Temperature,    | Device<br>type | Lin         | nits          | Unit |  |

|------------------------------------|-----------------------------------|----------------------------------------|-----------------|----------------|-------------|---------------|------|--|

|                                    |                                   | 5 V operation 2/                       | I A             | ,,             | Min         | Max           |      |  |

| DC specifications                  |                                   |                                        |                 |                |             | •             | •    |  |

| Input supply current IDDI (Q)      |                                   |                                        | -55°C to +125°C | 01             |             | 0.83          | mA   |  |

| per channel,<br>quiescent          |                                   |                                        | +25°C           |                | 0.57 1      | ypical        |      |  |

| Output supply current per channel, | I <sub>DDO</sub> (Q)              |                                        | -55°C to +125°C | 01             |             | 0.35          | mA   |  |

| quiescent                          |                                   |                                        | +25°C           |                | 0.29 1      | ypical        |      |  |

| Total supply current               | <u>3</u> /                        | DC to 2 Mbps                           |                 |                |             |               |      |  |

| V <sub>DD1</sub> supply current    | I <sub>DD1(Q)</sub>               | DC to 1 MHz logical signal frequency   | -55°C to +125°C | 01             |             | 3.2           | mA   |  |

|                                    |                                   | почистоу                               | +25°C           |                | 2.5 typical |               | ]    |  |

| V <sub>DD2</sub> supply current    | I <sub>DD2(Q)</sub>               | DC to 1 MHz logical signal frequency   | -55°C to +125°C | 01             |             | 2.4           | mA   |  |

|                                    |                                   | nequency                               | +25°C           |                | 1.6 typical |               | ]    |  |

| Total supply current               | <u>3</u> /                        | 10 Mbps                                |                 |                |             |               | •    |  |

| V <sub>DD1</sub> supply current    | I <sub>DD1(10)</sub>              | 5 MHz logical signal frequency         | -55°C to +125°C | 01             |             | 10.6          | mA   |  |

|                                    |                                   |                                        | +25°C           |                | 7.4 ty      | 7.4 typical   |      |  |

| V <sub>DD2</sub> supply current    | I <sub>DD2(10)</sub>              | 5 MHz logical signal frequency         | -55°C to +125°C | 01             |             | 6.5           | mA   |  |

|                                    |                                   |                                        | +25°C           |                | 4.4 typical |               | 1    |  |

| DC specifications                  |                                   |                                        | •               |                |             |               |      |  |

| Input leakage per channel          | Iį                                | $0 \text{ V} \leq V_{IX} \leq V_{DDX}$ | -55°C to +125°C | 01             | -10         | +10           | μА   |  |

| channel                            |                                   |                                        | +25°C           |                | +0.01       | +0.01 typical |      |  |

| V <sub>EX</sub> input pull up      | I <sub>PU</sub>                   | V <sub>E</sub> X = 0 V                 | -55°C to +125°C | 01             | -10         |               | μА   |  |

| current                            |                                   |                                        | +25°C           |                | -3 ty       | pical         |      |  |

| Tristate leakage current           | loz                               |                                        | -55°C to +125°C | 01             | -10         | +10           | μА   |  |

| per channel                        |                                   |                                        | +25°C           |                | +0.01       | typical       |      |  |

| Logic high input threshold         | VIH, VEH                          |                                        | -55°C to +125°C | 01             | 2.0         |               | V    |  |

| Logic low input threshold          | V <sub>IL</sub> , V <sub>EL</sub> |                                        | -55°C to +125°C | 01             |             | 0.8           | ٧    |  |

| DLA LAND AND MARITIME | SIZE | CODE IDENT NO. | DWG NO.          |

|-----------------------|------|----------------|------------------|

| COLUMBUS, OHIO        | A    | <b>16236</b>   | <b>V62/14630</b> |

|                       |      | REV            | PAGE 5           |

TABLE I. Electrical performance characteristics – Continued.  $\underline{1}/$

| Test                                                            | Symbol                                 | Conditions                                                                     | Temperature,<br>T <sub>A</sub> | Device<br>type | Lin         | nits                         | Unit  |

|-----------------------------------------------------------------|----------------------------------------|--------------------------------------------------------------------------------|--------------------------------|----------------|-------------|------------------------------|-------|

|                                                                 |                                        | 5 V operation 2/                                                               | i A                            |                | Min         | Max                          |       |

| DC specifications – conti                                       | nued.                                  |                                                                                |                                | •              |             | •                            | •     |

| Logic high output voltages                                      | V <sub>OAH</sub> ,<br>V <sub>OBH</sub> | $I_{OX} = -20 \mu A, V_{IX} = V_{IXH} \qquad \underline{4}/\underline{5}/$     | -55°C to +125°C                | 01             | -           | or V <sub>DD2</sub> )<br>0.1 | V     |

|                                                                 |                                        |                                                                                | +25°C                          |                | 5.0 ty      | /pical                       |       |

|                                                                 | V <sub>OCH</sub> ,                     | $I_{OX} = -4 \text{ mA}, V_{IX} = V_{IXH} \qquad \underline{4}/\underline{5}/$ | -55°C to +125°C                |                |             | or V <sub>DD2</sub> )<br>0.4 |       |

|                                                                 |                                        |                                                                                | +25°C                          |                | 4.8 t       | /pical                       |       |

| Logic low output<br>voltage                                     | V <sub>OAL</sub> ,                     | $I_{OX} = 20 \mu A, V_{IX} = V_{IXL} \qquad \underline{4}/\underline{6}/$      | -55°C to +125°C                | 01             |             | 0.1                          | V     |

|                                                                 | V <sub>OBL</sub>                       |                                                                                | +25°C                          | ı              | 0.0 ty      | /pical                       |       |

|                                                                 | V <sub>OCL</sub> ,                     | $I_{OX} = 400 \mu A, V_{IX} = V_{IXL}  \underline{4}/\underline{6}/$           | -55°C to +125°C                |                |             | 0.1                          |       |

|                                                                 | V <sub>ODL</sub>                       |                                                                                | +25°C                          |                | 0.04 1      | ypical                       |       |

|                                                                 |                                        | $I_{OX} = 4 \text{ mA}, V_{IX} = V_{IXL} \qquad \underline{4}/\underline{6}/$  | -55°C to +125°C                |                |             | 0.4                          |       |

|                                                                 |                                        |                                                                                | +25°C                          |                | 0.2 typical |                              |       |

| Switching specifications.                                       | •                                      |                                                                                |                                | •              |             |                              | •     |

| Minimum pulse width                                             | PW                                     | C <sub>L</sub> = 15 pF, CMOS signal levels                                     | -55°C to +125°C                | 01             |             | 100                          | ns    |

| Maximum data rate                                               |                                        | C <sub>L</sub> = 15 pF, CMOS signal levels                                     | -55°C to +125°C                | 01             | 10          |                              | Mbps  |

| Propagation delay                                               | t <sub>PHL</sub> ,                     | C <sub>L</sub> = 15 pF, CMOS signal levels                                     | -55°C to +125°C                | 01             | 20          | 50                           | ns    |

|                                                                 | tPLH                                   |                                                                                | +25°C                          |                | 32 typical  |                              |       |

| Pulse width distortion<br> tplh - tphl                          | PWD                                    | C <sub>L</sub> = 15 pF, CMOS signal levels                                     | -55°C to +125°C                | 01             |             | 3                            | ns    |

| Pulse width distortion   tplh - tphl  change versus temperature |                                        | C <sub>L</sub> = 15 pF, CMOS signal levels                                     | +25°C                          | 01             | 5 ty        | pical                        | ps/°C |

| Propagation delay skew                                          | tpsk                                   | C <sub>L</sub> = 15 pF, CMOS signal levels                                     | -55°C to +125°C                | 01             |             | 15                           | ns    |

| DLA LAND AND MARITIME | SIZE | CODE IDENT NO. | DWG NO.          |

|-----------------------|------|----------------|------------------|

| COLUMBUS, OHIO        | A    | <b>16236</b>   | <b>V62/14630</b> |

|                       |      | REV            | PAGE 6           |

TABLE I. <u>Electrical performance characteristics</u> – Continued. <u>1</u>/

| Test                                                       | Symbol                          | Conditions                                       | Temperature,    | Device<br>type | Lir   | mits    | Unit        |  |

|------------------------------------------------------------|---------------------------------|--------------------------------------------------|-----------------|----------------|-------|---------|-------------|--|

|                                                            |                                 | 5 V operation <u>2</u> /                         | 1A              |                | 1,700 | Min     | Max         |  |

| Switching specifications -                                 | - continued                     |                                                  |                 |                |       | 1       | •           |  |

| Channel to channel matching, codirectional channels        | tpskcd                          | C <sub>L</sub> = 15 pF, CMOS signal levels       | -55°C to +125°C | 01             |       | 3       | ns          |  |

| Channel to channel matching, opposing directional channels | †PSKOD                          | C <sub>L</sub> = 15 pF, CMOS signal levels       | -55°C to +125°C | 01             |       | 6       | ns          |  |

| Output propagation delay, disable                          | t <sub>PHZ</sub> ,              | C <sub>L</sub> = 15 pF, CMOS signal levels       | -55°C to +125°C | 01             |       | 8       | ns          |  |

| (high/low to high impedance)                               | t <sub>PLZ</sub>                |                                                  | +25°C           |                | 6 ty  | pical   |             |  |

| Output propagation delay, enable                           | tpzH,                           | C <sub>L</sub> = 15 pF, CMOS signal levels       | -55°C to +125°C | 01             |       | 8       | ns          |  |

| (high impedance to high/low)                               | tpzL                            |                                                  | +25°C           |                | 6 ty  | pical   |             |  |

| Output rise/fall time (10% to 90%)                         | t <sub>R</sub> / t <sub>F</sub> | C <sub>L</sub> = 15 pF, CMOS signal levels       | +25°C           | 01             | 2.5 t | ypical  | ns          |  |

| Common mode <u>7/</u> transient immunity                   | CM <sub>H</sub>                 | $V_{IX} = V_{DD1}/V_{DD2}, V_{CM} = 1000 V,$     | -55°C to +125°C | 01             | 25    |         | kV/μs       |  |

| logic high output                                          |                                 | transient magnitude = 800 V                      | +25°C           |                | 35 t  | ypical  |             |  |

| Common mode <u>7</u> /<br>transient immunity               | CML                             | V <sub>IX</sub> = 0 V, V <sub>CM</sub> = 1000 V, | -55°C to +125°C | 01             | 25    |         | kV/μs       |  |

| logic low output                                           |                                 | transient magnitude = 800 V                      | +25°C           |                | 35 t  | ypical  |             |  |

| Refresh rate                                               | fr                              |                                                  | +25°C           | 01             | 1.2 t | ypical  | Mbps        |  |

| Dynamic supply current per channel, input                  | I <sub>DDI(D)</sub>             | 8/                                               | +25°C           | 01             | 0.20  | typical | mA/<br>Mbps |  |

| Dynamic supply current per channel, output                 | I <sub>DDO(D)</sub>             | <u>8</u> /                                       | +25°C           | 01             | 0.05  | typical | mA/<br>Mbps |  |

| DLA LAND AND MARITIME | SIZE | CODE IDENT NO. | DWG NO.          |

|-----------------------|------|----------------|------------------|

| COLUMBUS, OHIO        | A    | <b>16236</b>   | <b>V62/14630</b> |

|                       |      | REV            | PAGE 7           |

TABLE I. <u>Electrical performance characteristics</u> – Continued.  $\underline{1}/$

| Test                                             | Symbol                            | Conditions                             | Temperature,    | Device<br>type | Lir           | mits    | Unit |     |  |

|--------------------------------------------------|-----------------------------------|----------------------------------------|-----------------|----------------|---------------|---------|------|-----|--|

|                                                  |                                   | 3.3 V operation 9/                     |                 |                |               |         | Min  | Max |  |

| DC specifications                                |                                   | •                                      |                 |                |               | 1       | •    |     |  |

| Input supply current                             | I <sub>DDI</sub> (Q)              |                                        | -55°C to +125°C | 01             |               | 0.49    | mA   |     |  |

| per channel,<br>quiescent                        |                                   |                                        | +25°C           |                | 0.31          | typical |      |     |  |

| Output supply current per channel,               | I <sub>DDO</sub> (Q)              |                                        | -55°C to +125°C | 01             |               | 0.27    | mA   |     |  |

| quiescent                                        |                                   |                                        | +25°C           |                | 0.19          | typical |      |     |  |

| Total supply current                             | <u>3</u> /                        | DC to 2 Mbps                           |                 |                |               |         | _    |     |  |

| V <sub>DD1</sub> supply current                  | I <sub>DD1(Q)</sub>               | DC to 1 MHz logical signal frequency   | -55°C to +125°C | 01             |               | 1.9     | mA   |     |  |

|                                                  |                                   | nequency                               | +25°C           |                | 1.4 t         | ypical  |      |     |  |

| V <sub>DD2</sub> supply current I <sub>DD2</sub> | I <sub>DD2(Q)</sub>               | DC to 1 MHz logical signal             | -55°C to +125°C | 01             |               | 1.5     | mA   |     |  |

|                                                  |                                   | frequency                              | +25°C           | -              | 0.9 typical   |         |      |     |  |

| Total supply current                             | <u>3</u> /                        | 10 Mbps                                |                 |                |               |         |      |     |  |

| V <sub>DD1</sub> supply current                  | I <sub>DD1(10)</sub>              | 5 MHz logical signal frequency         | -55°C to +125°C | 01             |               | 5.6     | mA   |     |  |

|                                                  |                                   |                                        | +25°C           | -              | 4.1 t         | ypical  |      |     |  |

| V <sub>DD2</sub> supply current                  | I <sub>DD2(10)</sub>              | 5 MHz logical signal frequency         | -55°C to +125°C | 01             |               | 3.3     | mA   |     |  |

|                                                  |                                   |                                        | +25°C           | -              | 2.5 typical   |         |      |     |  |

| DC specifications                                |                                   | •                                      |                 |                |               |         | •    |     |  |

| Input leakage per channel                        | l <sub>l</sub>                    | $0 \text{ V} \leq V_{IX} \leq V_{DDX}$ | -55°C to +125°C | 01             | -10           | +10     | μА   |     |  |

| channei                                          |                                   |                                        | +25°C           |                | +0.01 typical |         |      |     |  |

| V <sub>EX</sub> input pull up                    | I <sub>PU</sub>                   | V <sub>E</sub> X = 0 V                 | -55°C to +125°C | 01             | -10           |         | μА   |     |  |

| current                                          |                                   |                                        | +25°C           | -              | -3 typical    |         |      |     |  |

| Tristate leakage current                         | loz                               |                                        | -55°C to +125°C | 01             | -10           | +10     | μА   |     |  |

| per channel                                      |                                   |                                        | +25°C           |                | +0.01         | typical |      |     |  |

| Logic high input threshold                       | V <sub>IH</sub> , V <sub>EH</sub> |                                        | -55°C to +125°C | 01             | 1.6           |         | V    |     |  |

| Logic low input threshold                        | V <sub>IL</sub> , V <sub>EL</sub> |                                        | -55°C to +125°C | 01             |               | 0.4     | V    |     |  |

| DLA LAND AND MARITIME | SIZE | CODE IDENT NO. | DWG NO.          |

|-----------------------|------|----------------|------------------|

| COLUMBUS, OHIO        | A    | <b>16236</b>   | <b>V62/14630</b> |

|                       |      | REV            | PAGE 8           |

TABLE I.  $\underline{\text{Electrical performance characteristics}}$  – Continued.  $\underline{1}/$

| Test Syn                                                        | Symbol                                 | Conditions                                                                     | Temperature,<br>T <sub>A</sub> | Device<br>type | Lir                                              | nits                         | Unit  |

|-----------------------------------------------------------------|----------------------------------------|--------------------------------------------------------------------------------|--------------------------------|----------------|--------------------------------------------------|------------------------------|-------|

|                                                                 |                                        | 3.3 V operation <u>9</u> /                                                     | - 7                            |                | Min                                              | Max                          |       |

| DC specifications – cont                                        | inued.                                 |                                                                                |                                |                |                                                  |                              |       |

| Voltages                                                        | V <sub>OAH</sub> ,<br>V <sub>OBH</sub> | $I_{OX} = -20 \mu A, V_{IX} = V_{IXH} \frac{4}{5}$                             | -55°C to +125°C                | 01             | (V <sub>DD1</sub> or V <sub>DD2</sub> )<br>- 0.1 |                              | V     |

|                                                                 |                                        |                                                                                | +25°C                          |                | 3.3                                              | typical                      |       |

|                                                                 | V <sub>OCH</sub> ,                     | $I_{OX} = -4 \text{ mA}, V_{IX} = V_{IXH} \qquad \underline{4}/\underline{5}/$ | -55°C to +125°C                |                | -                                                | or V <sub>DD2</sub> )<br>0.4 |       |

|                                                                 |                                        |                                                                                | +25°C                          |                | 2.8 t                                            | ypical                       |       |

| VOBL VOCL                                                       | V <sub>OAL</sub> ,                     | $I_{OX} = 20 \mu A, V_{IX} = V_{IXL} $ 4/ 6/                                   | -55°C to +125°C                | 01             |                                                  | 0.1                          | V     |

|                                                                 | V <sub>OBL</sub>                       |                                                                                | +25°C                          |                | 0.0 typical                                      |                              | 1     |

|                                                                 | V <sub>OCL</sub> ,                     | $I_{OX} = 400 \mu A, V_{IX} = V_{IXL}  \underline{4}/\underline{6}/$           | -55°C to +125°C                |                |                                                  | 0.1                          |       |

|                                                                 | V <sub>ODL</sub>                       |                                                                                | +25°C                          |                | 0.04                                             | typical                      |       |

|                                                                 |                                        | $I_{OX} = 4 \text{ mA}, V_{IX} = V_{IXL} \qquad \underline{4}/\underline{6}/$  | -55°C to +125°C                |                |                                                  | 0.4                          |       |

|                                                                 |                                        |                                                                                | +25°C                          |                | 0.2 t                                            | ypical                       |       |

| Switching specifications                                        |                                        |                                                                                |                                |                |                                                  |                              |       |

| Minimum pulse width                                             | PW                                     | C <sub>L</sub> = 15 pF, CMOS signal levels                                     | -55°C to +125°C                | 01             |                                                  | 100                          | ns    |

| Maximum data rate                                               |                                        | C <sub>L</sub> = 15 pF, CMOS signal levels                                     | -55°C to +125°C                | 01             | 10                                               |                              | Mbps  |

| Propagation delay                                               | t <sub>PHL</sub> ,                     | C <sub>L</sub> = 15 pF, CMOS signal levels                                     | -55°C to +125°C                | 01             | 20                                               | 50                           | ns    |

|                                                                 | tpLH                                   |                                                                                | +25°C                          |                | 38 typical                                       |                              |       |

| Pulse width distortion<br> tplh - tphl                          | PWD                                    | C <sub>L</sub> = 15 pF, CMOS signal levels                                     | -55°C to +125°C                | 01             |                                                  | 3                            | ns    |

| Pulse width distortion   tplh - tphl  change versus temperature |                                        | C <sub>L</sub> = 15 pF, CMOS signal levels                                     | +25°C                          | 01             | 5 typical                                        |                              | ps/°C |

| Propagation delay skew                                          | t <sub>PSK</sub>                       | C <sub>L</sub> = 15 pF, CMOS signal levels                                     | -55°C to +125°C                | 01             |                                                  | 22                           | ns    |

| DLA LAND AND MARITIME<br>COLUMBUS, OHIO | SIZE CODE IDENT NO.  A 16236 |     | DWG NO.<br><b>V62/14630</b> |

|-----------------------------------------|------------------------------|-----|-----------------------------|

|                                         |                              | REV | PAGE 9                      |

TABLE I. <u>Electrical performance characteristics</u> – Continued. <u>1</u>/

| Test                                                       | Test Symbol Conditions Temperat |                                                  | Temperature,    | Device<br>type | Lir       | nits    | Unit        |

|------------------------------------------------------------|---------------------------------|--------------------------------------------------|-----------------|----------------|-----------|---------|-------------|

|                                                            |                                 | 3.3 V operation <u>9</u> /                       |                 |                | Min       | Max     |             |

| Switching specifications -                                 | - continued                     |                                                  |                 |                |           |         |             |

| Channel to channel matching, codirectional channels        | tpskcd                          | C <sub>L</sub> = 15 pF, CMOS signal levels       | -55°C to +125°C | 01             |           | 3       | ns          |

| Channel to channel matching, opposing directional channels | tpskod                          | C <sub>L</sub> = 15 pF, CMOS signal levels       | -55°C to +125°C | 01             |           | 6       | ns          |

| Output propagation delay, disable                          | t <sub>PHZ</sub> ,              | C <sub>L</sub> = 15 pF, CMOS signal levels       | -55°C to +125°C | 01             |           | 8       | ns          |

| (high/low to high impedance)                               | tPLZ                            |                                                  | +25°C           |                | 6 ty      | pical   |             |

| Output propagation delay, enable                           | tpzH,                           | C <sub>L</sub> = 15 pF, CMOS signal levels       | -55°C to +125°C | 01             |           | 8       | ns          |

| (high impedance to high/low)                               | tpzL                            |                                                  | +25°C           |                | 6 typical |         |             |

| Output rise/fall time (10% to 90%)                         | t <sub>R</sub> / t <sub>F</sub> | C <sub>L</sub> = 15 pF, CMOS signal levels       | +25°C           | 01             | 3 ty      | pical   | ns          |

| Common mode 7/ transient immunity                          | CM <sub>H</sub>                 | $V_{IX} = V_{DD1}/V_{DD2}, V_{CM} = 1000 V,$     | -55°C to +125°C | 01             | 25        |         | kV/μs       |

| logic high output                                          |                                 | transient magnitude = 800 V                      | +25°C           |                | 35 ty     | /pical  |             |

| Common mode <u>7/</u> transient immunity                   | CML                             | V <sub>IX</sub> = 0 V, V <sub>CM</sub> = 1000 V, | -55°C to +125°C | 01             | 25        |         | kV/μs       |

| logic low output                                           |                                 | transient magnitude = 800 V                      | +25°C           |                | 35 ty     | /pical  |             |

| Refresh rate                                               | fr                              |                                                  | +25°C           | 01             | 1.1 t     | ypical  | Mbps        |

| Dynamic supply current per channel, input                  | I <sub>DDI(D)</sub>             | 8/                                               | +25°C           | 01             | 0.10      | typical | mA/<br>Mbps |

| Dynamic supply current per channel, output                 | I <sub>DDO(D)</sub>             | 8/                                               | +25°C           | 01             | 0.03      | typical | mA/<br>Mbps |

| DLA LAND AND MARITIME | SIZE | CODE IDENT NO. | DWG NO.          |

|-----------------------|------|----------------|------------------|

| COLUMBUS, OHIO        | A    | <b>16236</b>   | <b>V62/14630</b> |

|                       |      | REV            | PAGE 10          |

TABLE I. Electrical performance characteristics – Continued.  $\underline{1}/$

| Test                               | Symbol               | Conditions                                                          | Temperature,                    | Device<br>type | Lir          | nits    | Unit   |  |

|------------------------------------|----------------------|---------------------------------------------------------------------|---------------------------------|----------------|--------------|---------|--------|--|

|                                    |                      | 5 V / 3.3 V or<br>3.3 V / 5 V operation <u>10</u> /                 |                                 | Min            | Max          |         |        |  |

| DC specifications                  |                      |                                                                     |                                 |                |              |         |        |  |

| Input supply current               | I <sub>DDI (Q)</sub> | 5 V / 3.3 V operation                                               | -55°C to +125°C                 | 01             |              | 0.83    | mA     |  |

| per channel,<br>quiescent          |                      | +25°C                                                               | +25°C                           |                | 0.57         | typical |        |  |

|                                    |                      | 3.3 V / 5 V operation                                               | -55°C to +125°C                 |                |              | 0.49    |        |  |

|                                    |                      |                                                                     | +25°C                           |                | 0.31         | typical |        |  |

| Output supply current per channel, | I <sub>DDO (Q)</sub> | 5 V / 3.3 V operation                                               | -55°C to +125°C                 | 01             |              | 0.27    | mA     |  |

| quiescent                          |                      |                                                                     | +25°C                           | -              | 0.29 typical |         |        |  |

|                                    |                      | 3.3 V / 5 V operation                                               | -55°C to +125°C                 |                |              | 0.35    | 1      |  |

|                                    |                      |                                                                     | +25°C                           |                | 0.19         | typical |        |  |

| Total supply current               | <u>3</u> /           | DC to 2 Mbps                                                        | •                               |                |              |         |        |  |

| V <sub>DD1</sub> supply current    | I <sub>DD1(Q)</sub>  | IDD1(Q) DC to 1 MHz logical signal frequency, 5 V / 3.3 V operation | -55°C to +125°C                 | 01             |              | 3.2     | mA     |  |

|                                    |                      | DC to 1 MHz logical signal                                          | noquency, o v / o.o v operation | +25°C          |              | 2.5 t   | ypical |  |

|                                    |                      |                                                                     | -55°C to +125°C                 |                |              | 1.9     |        |  |

|                                    |                      | frequency, 3.3 V / 5 V operation                                    | +25°C                           |                | 1.4 t        | ypical  |        |  |

| V <sub>DD2</sub> supply current    | I <sub>DD2(Q)</sub>  | DC to 1 MHz logical signal frequency, 5 V / 3.3 V operation         | -55°C to +125°C                 | 01             |              | 1.5     | mA     |  |

|                                    |                      | rrequericy, 5 v / 5.5 v operation                                   | +25°C                           |                | 0.9 t        | ypical  |        |  |

|                                    |                      | DC to 1 MHz logical signal                                          | -55°C to +125°C                 |                |              | 2.4     | 1      |  |

|                                    |                      | frequency, 3.3 V / 5 V operation                                    | +25°C                           |                | 1.6 t        | ypical  |        |  |

| Total supply current               | <u>3</u> /           | 10 Mbps                                                             |                                 |                |              |         |        |  |

| V <sub>DD1</sub> supply current    | I <sub>DD1(10)</sub> | 5 MHz logical signal frequency,<br>5 V / 3.3 V operation            | -55°C to +125°C                 | 01             |              | 10.6    | mA     |  |

|                                    |                      | 5 17 0.0 1 operation                                                | +25°C                           |                | 7.4 t        | ypical  |        |  |

|                                    |                      | 5 MHz logical signal frequency,                                     | -55°C to +125°C                 |                |              | 5.6     | ]      |  |

|                                    |                      | 3.3 V / 5 V operation                                               | +25°C                           |                | 4.1 t        | ypical  |        |  |

| DLA LAND AND MARITIME | SIZE | CODE IDENT NO. | DWG NO.          |

|-----------------------|------|----------------|------------------|

| COLUMBUS, OHIO        | A    | <b>16236</b>   | <b>V62/14630</b> |

|                       |      | REV            | PAGE 11          |

TABLE I. <u>Electrical performance characteristics</u> – Continued. <u>1</u>/

| Test                                 | Symbol                                 | Conditions                                                                 | Temperature,    | Device<br>type | Lir                                              | nits                             | Unit |

|--------------------------------------|----------------------------------------|----------------------------------------------------------------------------|-----------------|----------------|--------------------------------------------------|----------------------------------|------|

|                                      |                                        | 5 V / 3.3 V or<br>3.3 V / 5 V operation <u>10</u> /                        | TA              |                | Min                                              | Max                              |      |

| DC specifications – conti            | nued.                                  |                                                                            |                 |                |                                                  |                                  |      |

| Total supply current                 | <u>3</u> /                             | 10 Mbps                                                                    |                 |                |                                                  |                                  |      |

| V <sub>DD2</sub> supply current      | I <sub>DD2(10)</sub>                   | 5 MHz logical signal frequency,<br>5 V / 3.3 V operation                   | -55°C to +125°C | 01             |                                                  | 3.3                              | mA   |

|                                      |                                        | '                                                                          | +25°C           |                | 2.5 t                                            | ypical                           |      |

|                                      |                                        | 5 MHz logical signal frequency,<br>3.3 V / 5 V operation                   | -55°C to +125°C |                |                                                  | 6.5                              |      |

|                                      |                                        | 3.3 V / 5 V operation                                                      | +25°C           |                | 4.4 t                                            | ypical                           |      |

| Input leakage per channel            | lı                                     | $0 \text{ V} \leq V_{IX} \leq V_{DDX}$                                     | -55°C to +125°C | 01             | -10                                              | +10                              | μА   |

|                                      |                                        |                                                                            | +25°C           |                | +0.01 typical                                    |                                  |      |

| V <sub>EX</sub> input pull up        | I <sub>PU</sub>                        | V <sub>E</sub> X = 0 V                                                     | -55°C to +125°C | 01             | -10                                              |                                  | μА   |

| current                              |                                        |                                                                            | +25°C           | -              | -3 typical                                       |                                  |      |

| Tristate leakage current per channel | loz                                    |                                                                            | -55°C to +125°C | 01             | -10                                              | +10                              | μА   |

| per chamici                          |                                        |                                                                            | +25°C           |                | +0.01                                            | typical                          |      |

| Logic high input threshold           | V <sub>IH</sub> ,                      | 5 V / 3.3 V operation                                                      | -55°C to +125°C | 01             | 2.0                                              |                                  | V    |

| tilleshold                           | VEH                                    | 3.3 V / 5 V operation                                                      |                 |                | 1.6                                              |                                  |      |

| Logic low input                      | V <sub>IL</sub> , V <sub>EL</sub>      | 5 V / 3.3 V operation                                                      | -55°C to +125°C | 01             |                                                  | 0.8                              | V    |

| threshold                            |                                        | 3.3 V / 5 V operation                                                      |                 |                |                                                  | 0.4                              |      |

| Logic high output voltages           | V <sub>OAH</sub> ,<br>V <sub>OBH</sub> | $I_{OX} = -20 \mu A, V_{IX} = V_{IXH} \qquad \underline{4}/\underline{5}/$ | -55°C to +125°C | 01             | (V <sub>DD1</sub> or V <sub>DD2</sub> )<br>- 0.1 |                                  | V    |

|                                      |                                        |                                                                            | +25°C           |                |                                                  | or V <sub>DD2</sub> )<br>ical    |      |

|                                      | V <sub>OCH</sub> ,<br>V <sub>ODH</sub> | $I_{OX} = -4 \text{ mA}, V_{IX} = V_{IXH} \qquad 4/5/$                     | -55°C to +125°C |                |                                                  | or V <sub>DD2</sub> )<br>0.4     |      |

|                                      |                                        |                                                                            | +25°C           |                |                                                  | or V <sub>DD2</sub> )<br>typical |      |

| DLA LAND AND MARITIME | SIZE | CODE IDENT NO. | DWG NO.          |

|-----------------------|------|----------------|------------------|

| COLUMBUS, OHIO        | A    | <b>16236</b>   | <b>V62/14630</b> |

|                       |      | REV            | PAGE 12          |

TABLE I.  $\underline{\text{Electrical performance characteristics}}$  – Continued.  $\underline{1}/$

| Test                                                            | Symbol             | Conditions                                                                    | Temperature,<br>T <sub>A</sub> | Device<br>type | e Limits     |        | Unit  |

|-----------------------------------------------------------------|--------------------|-------------------------------------------------------------------------------|--------------------------------|----------------|--------------|--------|-------|

|                                                                 |                    | 5 V / 3.3 V or<br>3.3 V / 5 V operation <u>10</u> /                           | 'A                             |                | Min          | Max    |       |

| DC specifications – contin                                      | nued.              |                                                                               |                                |                |              |        |       |

| voltage                                                         | V <sub>OAL</sub> , | $I_{OX} = 20 \mu A$ , $V_{IX} = V_{IXL} \qquad \underline{4}/\underline{6}/$  | -55°C to +125°C                | 01             |              | 0.1    | V     |

| · onago                                                         | VOBL               | +25°                                                                          |                                |                | 0.0 t        | ypical |       |

| V <sub>OCL</sub> ,<br>V <sub>ODL</sub>                          |                    | $I_{OX} = 400 \mu A, V_{IX} = V_{IXL} $ 4/6/                                  | -55°C to +125°C                |                |              | 0.1    |       |

|                                                                 | VODL               |                                                                               | +25°C                          |                | 0.04 typical |        |       |

|                                                                 |                    | $I_{OX} = 4 \text{ mA}, V_{IX} = V_{IXL} \qquad \underline{4}/\underline{6}/$ | -55°C to +125°C                |                |              | 0.4    |       |

|                                                                 |                    | +25°C                                                                         |                                | 0.2 typical    |              |        |       |

| Switching specifications                                        |                    |                                                                               | •                              |                |              |        |       |

| Minimum pulse width                                             | PW                 | C <sub>L</sub> = 15 pF, CMOS signal levels                                    | -55°C to +125°C                | 01             |              | 100    | ns    |

| Maximum data rate                                               |                    | C <sub>L</sub> = 15 pF, CMOS signal levels                                    | -55°C to +125°C                | 01             | 10           |        | Mbps  |

| Propagation delay                                               | t <sub>PHL</sub> , | C <sub>L</sub> = 15 pF, CMOS signal levels                                    | s -55°C to +125°C 01 15        |                | 15           | 50     | ns    |

|                                                                 | tPLH               |                                                                               | +25°C                          |                | 35 ty        | /pical |       |

| Pulse width distortion  tplh - tphl                             | PWD                | C <sub>L</sub> = 15 pF, CMOS signal levels                                    | -55°C to +125°C                | 01             |              | 3      | ns    |

| Pulse width distortion   tplh - tphl  change versus temperature |                    | C <sub>L</sub> = 15 pF, CMOS signal levels                                    | +25°C                          | 01             | 5 ty         | pical  | ps/°C |

| Propagation delay skew                                          | tPSK               | C <sub>L</sub> = 15 pF, CMOS signal levels                                    | -55°C to +125°C                | 01             |              | 22     | ns    |

| DLA LAND AND MARITIME | SIZE | CODE IDENT NO. | DWG NO.          |

|-----------------------|------|----------------|------------------|

| COLUMBUS, OHIO        | A    | <b>16236</b>   | <b>V62/14630</b> |

|                       |      | REV            | PAGE 13          |

TABLE I.  $\underline{\text{Electrical performance characteristics}}$  – Continued.  $\underline{1}/$

| Test                                                       | Symbol                          | Conditions                                                                      | Temperature,    | Device<br>type | Lir         | nits   | Unit         |           |    |

|------------------------------------------------------------|---------------------------------|---------------------------------------------------------------------------------|-----------------|----------------|-------------|--------|--------------|-----------|----|

|                                                            |                                 | 5 V / 3.3 V or<br>3.3 V / 5 V operation <u>10</u> /                             | I A             | ,,             | Min         | Max    |              |           |    |

| Switching specifications -                                 | - continued                     |                                                                                 |                 |                |             |        |              |           |    |

| Channel to channel matching, codirectional channels        | tpskcd                          | C <sub>L</sub> = 15 pF, CMOS signal levels                                      | -55°C to +125°C | 01             |             | 3      | ns           |           |    |

| Channel to channel matching, opposing directional channels | <sup>†</sup> PSKOD              | C <sub>L</sub> = 15 pF, CMOS signal levels                                      | -55°C to +125°C | 01             |             | 6      | ns           |           |    |

| Output propagation delay, disable                          | t <sub>PHZ</sub> ,              | C <sub>L</sub> = 15 pF, CMOS signal levels                                      | -55°C to +125°C | 01             |             | 8      | ns           |           |    |

| (high/low to high impedance)                               | tPLZ                            |                                                                                 | +25°C           |                | 6 typical   |        |              |           |    |

| Output propagation delay, enable                           | tpzH,                           | C <sub>L</sub> = 15 pF, CMOS signal levels                                      | -55°C to +125°C | 01             |             | 8      | ns           |           |    |

| (high impedance to high/low)                               | tpzL                            |                                                                                 | +25°C           |                | 6 typical   |        |              |           |    |

| Output rise/fall time (10% to 90%)                         | t <sub>R</sub> / t <sub>F</sub> | C <sub>L</sub> = 15 pF, CMOS signal levels,<br>5 V / 3.3 V operation            | +25°C           | 01             | 3 typical   |        | 01 3 typical | 3 typical | ns |

|                                                            |                                 | C <sub>L</sub> = 15 pF, CMOS signal levels,<br>3.3 V / 5 V operation            |                 | 2.5 typic      |             | ypical |              |           |    |

| Common mode <u>7/</u> transient immunity                   | CM <sub>H</sub>                 | $V_{IX} = V_{DD1}/V_{DD2}, V_{CM} = 1000 V,$                                    | -55°C to +125°C | 01             | 25          |        | kV/μs        |           |    |

| logic high output                                          |                                 | transient magnitude = 800 V                                                     | +25°C           |                | 35 typical  |        |              |           |    |

| Common mode 7/<br>transient immunity                       | CML                             | V <sub>IX</sub> = 0 V, V <sub>CM</sub> = 1000 V,<br>transient magnitude = 800 V | -55°C to +125°C | 01             | 25          |        | kV/μs        |           |    |

| logic low output                                           |                                 | transient magnitude = 000 V                                                     | +25°C           |                | 35 typical  |        |              |           |    |

| Refresh rate                                               | fr                              | 5 V / 3.3 V operation                                                           | +25°C           | 01             | 1.2 t       | ypical | Mbps         |           |    |

|                                                            |                                 | 3.3 V / 5 V operation                                                           | ]               |                | 1.1 typical |        | 1            |           |    |

| DLA LAND AND MARITIME | SIZE | CODE IDENT NO. | DWG NO.          |

|-----------------------|------|----------------|------------------|

| COLUMBUS, OHIO        | A    | <b>16236</b>   | <b>V62/14630</b> |

|                       |      | REV            | PAGE 14          |

TABLE I. Electrical performance characteristics - Continued. 1/

| Test                                       | Symbol              | Conditions                                          | T <sub>Δ</sub> type |    | Temperature, Device Limits |        | nits        | Unit |

|--------------------------------------------|---------------------|-----------------------------------------------------|---------------------|----|----------------------------|--------|-------------|------|

|                                            |                     | 5 V / 3.3 V or<br>3.3 V / 5 V operation <u>10</u> / | . 7                 |    | Min                        | Max    |             |      |

| Dynamic supply current per channel, input  | I <sub>DDI(D)</sub> | 5 V / 3.3 V operation <u>8</u> /                    | +25°C               | 01 | 0.20 t                     | ypical | mA/<br>Mbps |      |

| per charmer, input                         |                     | 3.3 V / 5 V operation <u>8</u> /                    |                     |    | 0.10 t                     | ypical | Wibps       |      |

| Dynamic supply current per channel, output | I <sub>DDO(D)</sub> | 5 V / 3.3 V operation <u>8</u> /                    | +25°C               | 01 | 0.03 t                     | ypical | mA/<br>Mbps |      |

| por orialinos, output                      |                     | 3.3 V / 5 V operation <u>8</u> /                    |                     |    | 0.05 t                     | ypical | шоро        |      |

- 1/ Testing and other quality control techniques are used to the extent deemed necessary to assure product performance over the specified temperature range. Product may not necessarily be tested across the full temperature range and all parameters may not necessarily be tested. In the absence of specific parametric testing, product performance is assured by characterization and/or design.

- 2/ All voltages are relative to their respective ground. 4.5 V ≤ V<sub>DD1</sub> ≤ 5.5 V and 4.5 V ≤ V<sub>DD2</sub> ≤ 5.5 V. Unless otherwise specified, all minimum / maximum specifications apply over the entire recommended operation range. All typical specifications are at T<sub>A</sub> = 25°C, V<sub>DD1</sub> = V<sub>DD2</sub> = 5 V.

- The supply current values for all four channels are combined when running at identical data rates. Output supply current values are specified with no output load present. See figures 6 through 8 for information on per channel supply current as a function of data rate for unloaded and loaded conditions. See figures 9 and 10 for total V<sub>DD1</sub> and V<sub>DD2</sub> supply currents as a function of data rate for device channel configurations.

- $4/I_{OX}$  is the channel X output current, where X = A, B, C, or D.

- 5/ VIXH is the input side logic high.

- 6/ VIXL is the input side logic low.

- CM<sub>H</sub> is the maximum common mode voltage slew rate that can be sustained while maintaining the (V<sub>OUT</sub>) > 0.8 V<sub>DD2</sub>.

CM<sub>L</sub> is the maximum common mode voltage slew rate that can be sustained while maintain V<sub>OUT</sub> < 0.8 V.</p>

The common mode voltage slew rates apply to both rising and falling common mode voltage edges.

The transient magnitude is the range over which the common mode is slewed.

- 8/ Dynamic supply current is the incremental amount of supply current required for a 1 Mbps increase in signal data rate. See figures 6 through 8 for information on per channel supply current for unloaded and loaded conditions.

- 9/ All voltages are relative to their respective ground.  $3.135 \text{ V} \le \text{V}_{DD1} \le 3.6 \text{ V}$  and  $3.135 \text{ V} \le \text{V}_{DD2} \le 3.6 \text{ V}$ . Unless otherwise specified, all minimum / maximum specifications apply over the entire recommended operation range. All typical specifications are at  $T_A = 25^{\circ}\text{C}$ ,  $V_{DD1} = V_{DD2} = 3.3 \text{ V}$ .

- $\underline{10}$ / All voltages are relative to their respective ground. For 5 V / 3.3 V operation, 4.5 V ≤ V<sub>DD1</sub> ≤ 5.5 V and 3.135 V ≤ V<sub>DD2</sub> ≤ 3.6 V, and for 3.3 V / 5 V operation, 3.135 V ≤ V<sub>DD1</sub> ≤ 3.6 V and 4.5 V ≤ V<sub>DD2</sub> ≤ 5.5 V. Unless otherwise specified, all minimum / maximum specifications apply over the entire recommended operation range. All typical specifications are at T<sub>A</sub> = 25°C, V<sub>DD1</sub> = 3.3 V, V<sub>DD2</sub> = 5 V or V<sub>DD1</sub> = 5 V, V<sub>DD2</sub> = 3.3 V.

| DLA LAND AND MARITIME | SIZE     | CODE IDENT NO. | DWG NO.          |

|-----------------------|----------|----------------|------------------|

| COLUMBUS, OHIO        | <b>A</b> | <b>16236</b>   | <b>V62/14630</b> |

|                       |          | REV            | PAGE 15          |

FIGURE 1. Case outline.

| DLA LAND AND MARITIME | SIZE     | CODE IDENT NO. | DWG NO.          |

|-----------------------|----------|----------------|------------------|

| COLUMBUS, OHIO        | <b>A</b> | <b>16236</b>   | <b>V62/14630</b> |

|                       |          | REV            | PAGE 16          |

|        | Dimensions |        |             |       |  |  |

|--------|------------|--------|-------------|-------|--|--|

| Symbol | Inches     |        | Millimeters |       |  |  |

|        | Min        | Max    | Min         | Max   |  |  |

| А      | 0.0925     | 0.1043 | 2.35        | 2.65  |  |  |

| A1     | 0.0039     | 0.0118 | 0.10        | 0.30  |  |  |

| b      | 0.0122     | 0.0201 | 0.31        | 0.51  |  |  |

| С      | 0.0079     | 0.0130 | 0.20        | 0.33  |  |  |

| D      | 0.3976     | 0.4134 | 10.10       | 10.50 |  |  |