# AN-1084 应用笔记

One Technology Way • P.O. Box 9106 • Norwood, MA 02062-9106, U.S.A. • Tel: 781.329.4700 • Fax: 781.461.3113 • www.analog.com

### 通道切换: AD7190、AD7192、AD7193、AD7194、AD7195

作者: Mary McCarthy

#### 简介

Σ-Δ型ADC一般指定输出数据速率。输出数据速率是指当一个信号通道被选中且ADC连续进行转换时的转换速率。在数据采集系统等多通道应用中,会读取多个通道的转换值,也就是说,每个通道被轮流选中并进行转换。在这样的应用中,转换的速率不同于单通道系统。本应用笔记描述AD7190、AD7192、AD7193、AD7194和AD7195器件(以下简称为AD719x)所采用的切换程序。

#### 多通道系统

在PLC系统等应用中,需要数个输入通道来处理来自传感器的各种信号或输出。AD719x支持PGA和宽范围的可编程输出数据速率,可用于以不同的输出数据速率来转换不同幅度的信号。

应用通常都有一定的吞吐量要求,也就是说需要在一定的时间内读取一定数量的通道。具体要实现的吞吐量取决于要读取的通道数量和ADC转换每个通道所需的时间。本应用笔记中涉及的ADC具有如下不同的工作模式:

- Sinc⁴滤波器或Sinc³滤波器

- 斩波使能/禁用

- 零延迟

- 单次转换模式

- 自动通道时序控制

每种工作模式允许的输出数据速率和/或建立时间(即通道 改变后产生第一个转换所需的时间)各不相同。因此,吞吐 量还取决于工作模式。

# **AN-1084**

# 目录

| 简介1              | 使能斩波   | 5 |

|------------------|--------|---|

| 多通道系统1           | 零延迟    | 6 |

| 修订历史2            | 单次转换模式 | 6 |

| SINC⁴滤波器 (禁用斩波)3 | 通道序列器  | 7 |

| SINC³滤波器(禁用斩波)4  | 总结     | 7 |

### 修订历史

2010年9月—修订版0:初始版

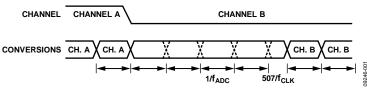

#### SINC<sup>4</sup>滤波器(禁用斩波)

选择sinc<sup>4</sup>滤波器并禁用斩波时,单通道连续转换的输出数据速率(f<sub>ADC</sub>)等于

$$f_{ADC} = f_{CLK}/(1024 \times FS[9:0])$$

其中, f<sub>CLK</sub>为主时钟频率, 而FS[9:0]为读入模式寄存器的滤波器字。通道改变后产生第一个转换所需的时间大概等于

$$t_{SETTLE} = 4/(f_{CLK}/(1024 \times FS[9:0]))$$

$$= 4096 \times FS[9:0]/f_{CLK}$$

采用低输出数据速率时,该等式足够精确。完整的建立时间计算公式为

$$t_{SETTLE} = 4/(f_{CLK}/(1024 \times FS[9:0])) + 507/f_{CLK}$$

$$= (4096 \times FS[9:0] + 507)/f_{CLK}$$

因此, 当通道发生改变时, 需要建立时间才可产生第一个 转换。接下来这个通道上的转换会以编程的输出数据速率 (f<sub>ADC</sub>)进行。如果应用中采用了数个通道且从每个通道读取一个转换,则每次转换都需要建立时间。因此,每秒读取的通道数等于

$$= f_{CLK}/(4096 \times FS[9:0] + 507)$$

当一个通道上的转换完成时,需要写入配置寄存器,以选择要转换的下一个通道。该SPI通信会降低吞吐量。表1总结了一些样本FS[9:0]值的输出数据速率、建立时间和吞吐量(忽略了SPI通信所需的时间)。

表1. Sinc<sup>4</sup>滤波器(禁用斩波)的输出数据速率、建立时间 和吞吐量

| FS[9:0] | f <sub>ADC</sub> (Hz) | t <sub>SETTLE</sub> (ms) | 每秒读取的通道数 |

|---------|-----------------------|--------------------------|----------|

| 96      | 50                    | 80.1                     | 12       |

| 80      | 60                    | 66.8                     | 14       |

| 1       | 4800                  | 0.936                    | 1067     |

图1. 通道切换(Sinc<sup>4</sup>滤波器,禁用斩波)

## AN-1084

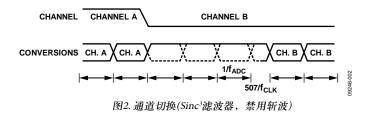

#### SINC3滤波器(禁用斩波)

通过设置模式寄存器的SINC<sup>3</sup>位,可以将数字滤波器改为 sinc<sup>3</sup>滤波器。选择sinc<sup>3</sup>滤波器并不会影响输出数据速率。 因此,单通道连续转换的输出数据速率还是

$$f_{ADC} = f_{CLK}/(1024 \times FS[9:0])$$

不过, 通道改变后产生有效转换所需的时间有所缩短。

$$t_{SETTLE} = 3/(f_{CLK}/(1024 \times FS[9:0])) + 507/f_{CLK}$$

$= (3072 \times FS[9:0] + 507)/f_{CLK}$

采用低输出数据速率时,该等式可近似为

$$t_{SETTLE} = 3072 \times FS[9:0]/f_{CLK}$$

在从每个通道读取一个转换的多通道应用中,系统的吞吐 量为

吞吐量 =

$$f_{CLK}/(3 \times 1024 \times FS[9:0] + 507)$$

$$= f_{CLK}/(3072 \times FS[9:0] + 507)$$

表2总结了一些样本FS[9:0]值的输出数据速率、建立时间和 吞吐量。在实际操作中,手动选择每个通道时,吞吐量会 下降。

#### 表2. Sinc³滤波器(禁用斩波)的输出数据速率、建立时间 和吞吐量

| FS[9:0] | f <sub>ADC</sub> (Hz) | t <sub>SETTLE</sub> (ms) | 每秒读取的通道数 |

|---------|-----------------------|--------------------------|----------|

| 96      | 50                    | 60.1                     | 16       |

| 80      | 60                    | 50.1                     | 19       |

| 1       | 4800                  | 0.728                    | 1373     |

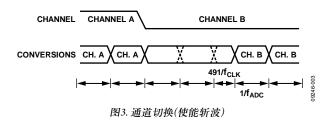

#### 使能斩波

#### Sinc⁴滤波器

选择sinc<sup>4</sup>滤波器并使能斩波时,单通道连续转换的输出数据速率(fADC)为

$$f_{ADC} = f_{CLK}/(1024 \times \text{FS}[9:0] \times 4 + 16)$$

=  $f_{CLK}/(4096 \times \text{FS}[9:0] + 16)$

通道改变后产生一个转换所需的时间(建立时间)等于

$$\begin{split} t_{\text{\tiny SETTLE}} &= 2/(\text{fCLK}/(1024 \times \text{FS}[9:0] \times 4 + 16)) + 491/f_{\text{\tiny CLK}} \\ &= (8192 \times \text{FS}[9:0] + 523)/\text{fCLK} \end{split}$$

采用低输出数据速率时,这些等式可近似为

$$f_{ADC} = f_{CLK}/(4096 \times FS[9:0])$$

$$t_{SETTLE} = 8192 \times FS[9:0]/f_{CLK}$$

如果应用中采用了数个通道且从每个通道读取一个转换, 则吞吐量为

$$f_{\text{CLK}}/(2 \times (1024 \times \text{FS}[9:0] \times 4 + 16) + 491)$$

$$= f_{CLK}/(8192 \times FS[9:0] + 523)$$

写入配置寄存器来选择各个通道也进一步降低吞吐量。

表3总结了一些样本FS[9:0]值的输出数据速率、建立时间和 吞吐量。

表3. Sinc<sup>4</sup>滤波器(使能斩波)的输出数据速率、建立时间 和吞吐量

| FS[9:0] | f <sub>ADC</sub> (Hz) | t <sub>SETTLE</sub> (ms) | 每秒读取的通道数 |

|---------|-----------------------|--------------------------|----------|

| 96      | 12.49                 | 160.1                    | 6        |

| 80      | 14.99                 | 133.4                    | 7        |

| 1       | 1195.3                | 1.773                    | 563      |

#### Sinc<sup>3</sup>滤波器

选择sinc<sup>3</sup>滤波器并使能斩波时,单通道连续转换的输出数据速率为

$$f_{ADC} = f_{CLK} / (1024 \times FS[9:0] \times 3 + 16)$$

=  $f_{CLK} / (3072 \times FS[9:0] + 16)$

建立时间为

$$\begin{split} t_{SETTLE} &= 2/(f_{CLK}/(1024 \times \text{FS[9:0]} \times 3 + 16)) + 491/f_{CLK} \\ &= (6144 \times \text{FS[9:0]} + 523)/f_{CLK} \end{split}$$

采用低输出数据速率时,这些等式可近似为

$$f_{ADC} = f_{CLK}/(3072 \times FS[9:0])$$

$t_{SETTLE} = 6144 \times FS[9:0]/f_{CLK}$

因此,通道改变后第一个转换的用时为tSETTLE,而接下来这个通道上的转换则以1/fADC的速率进行。

当系统中使能斩波且使用数个通道时, 吞吐量为

$$f_{CLK}/(2 \times (1024 \times FS[9:0] \times 3 + 16) + 491)$$

=  $f_{CLK}/(6144 \times FS[9:0] + 523)$

而选择各个通道所需的SPI通信会进一步降低吞吐量。

表4总结了一些样本FS[9:0]值的输出数据速率、建立时间和 吞吐量。

表4. Sinc<sup>3</sup>滤波器(使能斩波)的输出数据速率、建立时间 和吞吐量

| FS[9:0] | f <sub>ADC</sub> (Hz) | t <sub>SETTLE</sub> (ms) | 每秒读取的通道数 |

|---------|-----------------------|--------------------------|----------|

| 96      | 16.67                 | 120.1                    | 8        |

| 80      | 19.99                 | 100.1                    | 9        |

| 1       | 1591.7                | 1.356                    | 737      |

## AN-1084

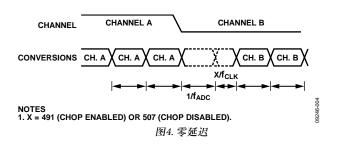

### 零延迟

这些Σ-Δ型ADC还支持零延迟模式。通过将模式寄存器的 MR11位(Single位)置1可以使能该模式。使能该模式 时,单通道连续转换的转换时间约等于建立时间。该模式 的优势在于,无论转换是在一个通道上发生的还是使用了 多个通道,所有转换之间的时间间隔都类似。

切换通道时,第一个转换会有491/fCLK或507/fCLK的额外延迟。采用低输出数据速率时,该额外延迟几乎不会对建立时间的数值造成影响。不过,采用高输出数据速率时,应当考虑到该延迟。表5总结了单通道连续转换的输出数据速率和切换通道来使用不同滤波器配置时的输出数据速率。

切换通道时,AD719x允许利用完整的建立时间来在通道改变后产生第一个转换。因此,使能多个通道时,ADC会自动进入零延迟模式,也就是说设置Single位不会产生任何作用。

例如,如果选择sinc4滤波器、禁用斩波并使能零延迟,则

当FS = 96时,输出数据速率等于12.5 Hz。因此,转换时间为80 ms。建立时间为80.1 ms。当FS = 96时,每秒最多可对12个通道进行采样。因此,吞吐量与采用sinc4、禁用斩波并禁用零延迟配置时相同。

#### 单次转换模式

这些ADC还支持单次转换模式,在该模式下器件在执行一次转换之后即会进入关断模式。该模式并不适用于PLC等ADC进行连续转换的应用。不过,如果应用中采用多个输入通道且会定期从通道回读转换,那么该模式会很有用。

用户可以通过写入模式寄存器的MD2、MD1和MD0位来启动一次转换。相应地设置这些位后,ADC即会上电。内部时钟(若使用)需要一些时间才能完成上电。接着,需要完整的建立时间才会产生转换。ADC将本次转换值放入数据寄存器,把DOUT/RDY置为低电平,然后回到关断模式。在这种情况下,吞吐量取决于所用的通道数量、选定的输出数据速率和与ADC通信所需的时间。

表5. 输出数据速率和建立时间(零延迟)

| 滤波器               | 斩波 | fadc                                 | <b>t</b> settle                       |

|-------------------|----|--------------------------------------|---------------------------------------|

| Sinc <sup>4</sup> | 否  | $f_{CLK}/(4096 \times FS[9:0])$      | $(4096 \times FS[9:0] + 507)/f_{CLK}$ |

| Sinc <sup>3</sup> | 否  | $f_{CLK}/(3072 \times FS[9:0])$      | $(3072 \times FS[9:0] + 507)/f_{CLK}$ |

| Sinc <sup>4</sup> | 是  | $f_{CLK}/(8192 \times FS[9:0] + 32)$ | $(8192 \times FS[9:0] + 523)/f_{CLK}$ |

| Sinc <sup>3</sup> | 是  | $f_{CLK}/(6144 \times FS[9:0] + 32)$ | $(6144 \times FS[9:0] + 523)/f_{CLK}$ |

#### 通道序列器

本部分与AD7194无关,因为该器件没有序列器。

FS[9:0]位的值和工作模式是影响吞吐速率的主要因素。不过,在前文提到的所有模式中,用户必须在转换之间写入配置寄存器,以便选择用于转换的下一个通道。在单次转换模式下,用户必须写入模式寄存器和配置寄存器,才可启动另一个单次转换。

这些ADC片內集成通道序列器,可简化多通道应用中的器件使用。应用中使用的所有通道均被使能。然后,序列器逐个转换使能通道并在每个通道上执行一次转换。只有所有通道都采用相同的PGA增益和输出数据速率,才可使用通道序列器。如果遇到每个通道具有不同的PGA增益等情况,那么必须禁用序列器。

通过设置配置寄存器的CH0至CH7位可以使能要使用的通道。开始转换时,ADC会自动依次选择各个使能通道并在每个通道上执行一次转换。每当可以从通道中读取转换时,DOUT/RDY引脚都会变为低电平。当模式寄存器的DAT\_STA位置1时,状态寄存器的值会添加到每次转换。状态寄存器将指示与转换对应的具体通道。它还通过ERR位指示转换是否有效。

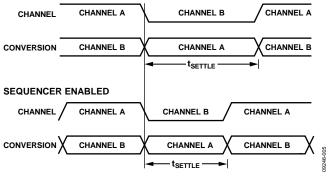

使能通道序列器时,每个通道的建立时间取决于所使用的滤波器配置。不过,与前文讨论的配置(已禁用序列器)相比,使能序列器时建立时间有所缩短。禁用序列器时,通道改变时建立时间存在491/f<sub>CLK</sub>或507/f<sub>CLK</sub>的延迟。使能序列器时,则该延迟仅存在于被转换的第一个通道中。后续通道的建立时间有所缩短。表6总结了使能序列器时每个通道的建立时间。第一个转换存在491/f<sub>CLK</sub>的额外延迟。

#### 表6.建立时间(使能序列器)

| 滤波器               | 斩波  | <b>t</b> SETTLE                        |

|-------------------|-----|----------------------------------------|

| Sinc <sup>4</sup> | No  | $(4096 \times FS[9:0] + 16)/f_{CLK}$   |

| Sinc <sup>3</sup> | No  | $(3072 \times FS[9:0] + 16)/f_{CLK}$   |

| Sinc <sup>4</sup> | Yes | $(8192 \times FS[9:0] + 32)/f_{CLK}$   |

| Sinc <sup>3</sup> | Yes | (6144 × FS[9:0] + 32)/f <sub>CLK</sub> |

#### 表7. 吞吐量(禁用/使能序列器)

| <u> </u> | <b>₹</b> 八十二十二十二十二十二十二十二十二十二十二十二十二十二十二十二十二十二十二十二 |       |  |  |

|----------|--------------------------------------------------|-------|--|--|

|          | 每秒读取的通道数(Sinc4,禁用斩波)                             |       |  |  |

| FS[9:0]  | 禁用序列器                                            | 使能序列器 |  |  |

| 96       | 12                                               | 12    |  |  |

| 80       | 14                                               | 14    |  |  |

| 1        | 1067                                             | 1195  |  |  |

表7比较了禁用斩波的sinc<sup>4</sup>滤波器在使能序列器和禁用序列器两种情况下每秒转换的通道数。本次比较并未包括禁用序列器时与ADC接口以选择下一通道所需的时间。采用低输出数据速率时,通道数量相同。不过,采用高输出数据速率时,序列器使通道数明显增加。

#### **SEQUENCER DISABLED**

图5. 使能/禁用序列器的比较

#### 总结

单通道应用和多通道应用的可用转换速率并不相同。在多通道系统中,每次选择通道时,需要建立时间才能产生第一个转换。而建立时间又取决于器件所配置的模式,如斩波使能/禁用和滤波器阶数。因此,在多通道系统中,用户需要计算给定配置所需的建立时间和应用中使用的通道数,才能确定器件的吞吐量。

| Λ | N  | -1  | n | Ω | 1 |

|---|----|-----|---|---|---|

| н | IV | - 1 | w | O | 4 |

注释