# AN-826 应用笔记

One Technology Way • P.O. Box 9106 • Norwood, MA 02062-9106, U.S.A • 电话: 781.329.4700 • 传真: 781.461.3113 • 网址: www.analog.com

## 2.4 GHz WiMAX直接变频发射机

作者: Cecile Masse和Qui Luu

#### 特性

直接变频发射链

使用5芯片实现Tx无线功能

双通道AD9862 MxFE、14位DAC、128 MSPS,提供可

编程满量程电流

3 GHz正交调制器ADL5373

2.7 GHz VGA ADL5330, 提供50 dB功率控制范围

4 GHz小数N分频频率合成器ADF4153

3 GHz均方根功率检波器AD8362

支持10 MHz信道频宽,提供1024子载波OFDM

支持QPSK、16 QAM和64 QAM OFDMA

发射机输出功率: 13 dBm(最大值)CW

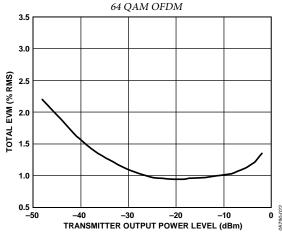

EVM 64 QAM OFDM: 1.2%(-3 dBm输出)

20 MHz偏移时的发射机噪声: -142.5 dBm/Hz (-1 dBm)

精确输出均方根功率控制

双电源供电: 5 V (380 mA), 3.3 V (165 mA)

#### 应用

WiBro/WiMAX 5 V CPE和基站

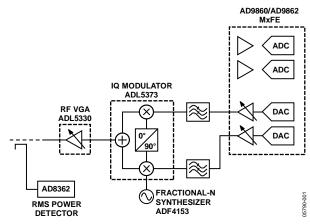

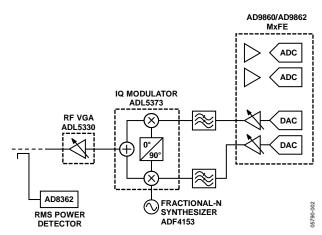

图1. 直接变频发射机

# 目录

| <b>特性</b> | 1 |

|-----------|---|

| 应用        |   |

| 简介        |   |

|           |   |

| 架构        |   |

| 模拟基带信号生成  |   |

| IQ调制器     | 5 |

| IO類家会成界   | Q |

| VGA和IQ调制器接口 | 9  |

|-------------|----|

| 均方根功率检测     | 10 |

| 总体系统性能      | 12 |

| 典型工作特性      | 13 |

| 测定性能总结      | 15 |

| 主要元件物料清单    | 16 |

## 简介

本应用笔记目的是示范ADI公司WiMAX 5 V发射信号链在 最高2.7 GHz频率下的应用。

随着无线通信行业迈向更高的RF频率,调制带宽越来越宽,数据速率也越来越高,日益需要高性能线性发射链。WiMAX无线宽带网络响应了这一趋势。在点对点和点对多点固定应用中,2.5 GHz和3.5 GHz频段的部署工作已经开始。利用宽带正交频分多路复用(OFDM)调制,可以实现高达80 Mbps的数据速率。

802.16 WiMAX固定或移动标准基于2<sup>N</sup>载波OFDM调制: 802.16d支持256点, 802.16e支持512至2048点。2<sup>N</sup>个子载波中的每一个均可采用QPSK、16 QAM或64 QAM数据序列进行调制。上述标准还支持从1.25 MHz至20 MHz的不同信号带宽以适应各种速率,不过目前配置定义了5 MHz至10 MHz的信道带宽。OFDM复合信号包络幅度可表现出明显的波峰和波谷,调制深度接近100%,峰均比大约为10 dB。这对发射链的线性度提出了严格要求。

为了解决这些挑战,选择了直接变频架构。对于该特定分析,评估了从基带信号生成直至电压控制放大器和功率检波器功能(但不包括功率放大器)的整个Tx信号链。重点是无线宽带(WiBro)频段2.3 GHz至2.4 GHz,该频段在韩国用于部署802.16d(固定)和802.16e(移动)标准。不过,此信号链在高达27 GHz的频率下也可使用(性能详情请参见AD9862、ADL5373、ADL5330、ADF4153和AD8362数据手册)。

#### 架构

无线电架构为直接上变频,具有下列优点:元件数少、更少混频杂散、更少滤波器、更低功耗。

此外,该架构仅需要单一上变频操作,因此仅需一个频率合成器。事实上,WiMAX OFDM或正交分频多址(OFDMA)信号内的大量子载波使得这种调制对相位噪声十分敏感,因为N个子载波均会通过本振(LO)的相位噪声进行调制。为此,必须尽可能减小加入调制的相位误差量。

Figure 2. Direct Conversion Tx Chain

该架构包括发射DAC、固定增益IQ调制器、LO小数N分频 频率合成器、RF VGA和均方根功率检波器。DAC输出端还需 要片外低通滤波器,以滤除采样频率倍频处的镜像。DAC 和频率合成器需要3.3 V电源,而所有其他元件采用5 V单电源供电。用于Tx信号链的具体元件如下:

- AD9860/AD9862, 12位/14位、128 MSPS采样DAC, SNR ≥ 70 dB

- ADL5373, 3 GHz IQ调制器

- ADF4153, 4 GHz LO小数N分频频率合成器

- ADL5330, 2.7 GHz电压控制放大器/衰减器VGA

- AD8362, 2.7 GHz均方根功率检波器

鉴于OFDM信号的性质以及极高数据速率带来的严格矢量 误差幅度(EVM)要求,根据上述元件在最高2.7 GHz频率下 的线性度和噪声性能,选择了上述元件。

以下部分介绍该Tx信号链内的各主要功能,重点说明系统设计原理、实现方案和接口。

#### 模拟基带信号生成

Tx DAC是该信号链内最重要的元件之一,因为它需要提供 最接近理想状态的模拟信号,以便执行上变频和放大。 DAC信噪比(SNR)和采样速率决定了驱动IQ调制器的调制 信号的频谱纯度及信号质量。

#### SNR和SFDR

为本应用选择的Tx DAC是AD9860/AD9862混合信号前端系列(MxFE\*)芯片,分别为12位和14位,最大采样速率为128 MHz。Tx DAC的输出是电流源,可编程峰值电流介于2 mA和20 mA之间。通过寄存器写操作对满量程电流进行编程,可以灵活调整IQ调制器的峰峰值输入电压,同时保持12位/14位分辨率。

在本应用中,建议信噪比至少为60 dB,以便满足最大功率水平下的频谱模板和最低功率水平下的EVM(例如,即使在天线最小输出功率下,64 QAM四分之三OFDM也需要31.4 dB的信噪比加上裕量)。12位AD9860和14位AD9862均提供优于70 dB的信噪比。在某些BTS应用中,需要更高的信噪比来满足严苛的频谱模板,此时建议使用16位DAC,例如AD9779。

此外,无论信号频率位于1 MHz还是6 MHz,第一奈奎斯特区内的无杂散动态范围(SFDR)在-76 dBc下始终恒定。例如,当处理大信号带宽时,例如以直流为中心的OFDM 10 MHz WiMAX信号,这一特性很有用。

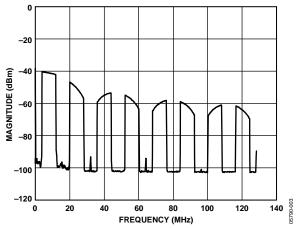

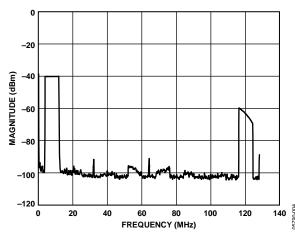

### 采样频率

采样频率可根据最大调制带宽适当加以选择。例如,具有8.75 MHz带宽的WiBro复OFDM信号需要的DAC采样速率  $f_{SAMPLING}$ 至少为2 × 10 MHz,或者两倍于奈奎斯特最小值 (OFDM调制采样频率= $n \times$ 带宽= $8/7 \times 8.75e6=10$  MHz)。但所有采样混叠将位于 $n \times 20$  MHz,从而落在20 MHz以上的RF 频率带宽的频段上。此类镜像仅可在DAC输出端通过片外重构滤波器进行滤波。

对在采样频率倍频处的镜像进行优质滤波需要更高阶滤波器实现。使用DAC内提供的插值滤波器可以避免该问题。 在DAC输入数据速率保持相同的前提下,插值滤波器 可以增加DAC采样频率。因此,镜像表现为远离主输入信号。图3和图4显示的是在AD9860/AD9862上使能4×插值滤波器的效果。

图3. AD9860/AD9862 Tx DAC通过1×插值生成OFDM信号 (fSAMPLE = 32 MSPS, 1×插值)

图4. AD9860/AD9862 TxDAC通过4×插值生成OFDM信号 (fSAMPLE = 32 MSPS, 4×插值)

因此,虽然Tx数字数据仅以20 MHz速率更新,但4×插值滤波器将总体采样速率有效增加至80 MHz。这样DAC输出端便可提供简单三阶贝塞尔LPF(参见"IQ调制器"部分)。

#### IQ调制器

#### 调制器AC驱动电平

调制器I和Q输入应采用差分驱动。对于峰均比为10 dB或更高的调制,如WiMAX OFDM,峰值驱动电平应低于压缩点至少10 dB,以将失真降至最低。最佳电平实际上是通过将调制器输出端频谱失真降至最低,同时保持足够的信噪比来确定的。

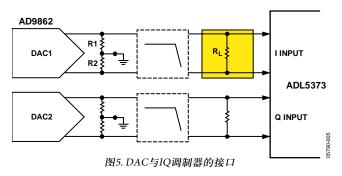

图5中显示了AD9862 DAC和ADL5373调制器之间的接口。 电阻R1和R2为调制器设置直流偏置电平,电阻 $R_L$ 设置基带 I和Q电压电平。

调制器差分输入电压可用公式1计算,与电阻 $R_L$ 和DAC满量程电流 $I_{DAC}$ 成函数关系。

$$V_{diff} = \frac{2 \times I_{DAC} \times R_{DC} \times R_L}{2 \times R_{DC} + R_L} = f(I_{DAC}) = g(R_L)$$

$$R_{DC} = RI = R2$$

(1)

ADL5373具有固定电压增益。调制器输出电平可通过选择 适当的输入负载电阻来设置。或者,也可选择较大电阻, 并可将DAC的满量程输出电流调整至所需驱动电平。

对于WiMAX这样的OFDM调制,ADL5373 IQ调制器的最佳驱动电平为0.650 V p-p ± 10%(详情请参见"寻找IQ调制器最佳工作点"部分)。在此电平下,调制器输出的均方根功率水平约为-12 dBm,在输出功率电平与频谱质量之间达到了最佳平衡。

要获得该输入电压,可使用 $50 \Omega R_L$ 电阻,同时以20 mA满量程电流驱动调制器。

不过,通常是在距满量程一定距离的水平下工作。例如,也可选择用于实现足够高峰值电压的R<sub>L</sub>(例如选择200 Ω以实现1.3 V p-p)并将DAC输出电流调整至大约10 mA

(或-6 dBFS), 从而设置上述最佳交流电平。接着需要在连接点R1和R2施加直流失调,以保持500 mV的直流偏置电平。注意,在此较低满量程电流下,DAC交流动态性能降低约2 dB。

#### 直流偏置电平

电阻R1和R2设置直流偏置电平。共模电压建议电平为500mV。

50 Ω值在20 mA的DAC满量程电流下产生所需的500 mV直流偏置,该直流偏置与R<sub>1</sub>值无关。

#### 基带滤波

在80 MHz(20 MHz + 4×插值)下对信号进行采样时,可定义 镜像抑制要求。DAC的采样保持作用等效于在频域中通过 sin(x)函数对采样波形进行卷积。

$$V_{out}(f) = V_{sampled}(f) \times \left(\frac{\sin(\pi f T)}{\pi f T}\right)$$

(2)

图3是该采样镜像整形效果的示例。因此,最高镜像通常处于 $1 \times f_s$ ,此处为 $80~MHz_s$

这些采样镜像的电平可用sin(x)/x函数来计算。

采样频率为80 MHz时,计算的电平在 $1 \times f_s$ 和 $2 \times f$ S下分别为-31.6 dBc和-37.6 dBc。上述镜像的测定电平实际上与这些计算值差别不大:第一和第二镜像分别为-33 dBc和-40 dBc。

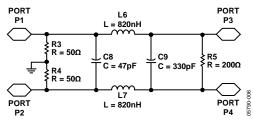

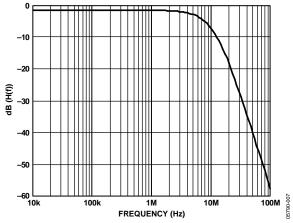

位于DAC调制器接口的重构滤波器用于为调制器提供干净的基带信号,不会因上变频将镜像搬移到RF带宽内。低通贝塞尔结构具有平坦的带内群延迟)参见图8),十分适合本应用。在8 MHz时具有3 dB截止频率的三阶滤波器在80 MHz时提供50 dB抑制,使采样镜像降至80 dBc。

图6至图8显示了基带滤波器的详细信息。

图6. 基带滤波器原理图,包括源电阻与端接电阻

图7. 基带滤波器增益响应,以分贝表示

该滤波器应考虑具有最低容差的无源元件,以将I与Q信号 路径间的不匹配降至最低。

#### LO馈诵和边带调零

调制器输出端的LO泄漏有不同来源:

- I和Q间的直流失调

- 导致差分信号I与 Ī或者Q与Q失衡的直流失调

- LO至RF隔离不良

通常,LO泄漏的最重要来源是信号生成与调制器混频器输入之间的基带信号上累积的无用直流失调。

另一方面,I与Q信号之间的幅度和相位不匹配以及LO 90°移相器误差也会造成无用的上边带镜像。当Tx DAC配置为复输出模式时,调制器输出端的有效镜像抑制非常重要,因为该杂散会进入通道,且无法进行滤波。该设计中的相位不匹配无法补偿,但通过DAC一级的独立增益校正可实现幅度匹配。

类似地,AD9862 DAC可让直流失调校正电压实现LO泄漏抑制。

I和Q幅度不匹配校正通过电流缩放来实现。使用精调和粗调增益控制(寄存器14和寄存器15)均可独立调整Tx通道的满量程输出电流。在未执行电流缩放时,粗调增益控制可予以旁路,或者可将电流缩小至满量程电流的1/2或1/11。该操作使电流产生-6 dB或-20 dB变化。如需更精细的分辨率,精调增益控制可将每一侧的满量程电流分别缩放±4%。

对于LO抑制,可在I通道或Q通道上施加正或负失调。在10位精度(寄存器10至寄存器13)下,可对任一差分通道施加最高达20 mA满量程±12%(或±2.4 mA)的失调电流。这远高于LO调零通常所需的水平。

增益和失调不匹配在模拟转换后予以校正,从而保持信号分辨率。调制器输出端的LO泄漏可抑制至75 dBc,无用边带在室温下可缩小至-60 dBc。

尽管WiMAX OFDM信号在直流中无子载波,也必须实现良好的直流失调校正,以帮助解调器区分WiMAX突发脉冲的开关时间,确保不会使接收机ADC在低发射功率下饱和。

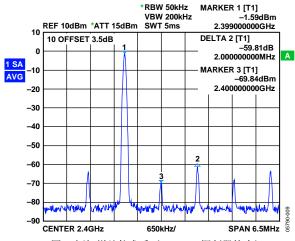

图9显示在施加直流失调和增益校准后,IQ调制器输出端的单边带频谱特性。无用边带位于-60 dBc,LO泄漏位于-70 dBc。

图9. 直流/增益校准后(DAC+IQ调制器输出), 2.4 GHz下的单边带频谱

#### 寻找IQ调制器最佳工作点

调制器最佳输出电平可通过测量频域中的上变频信号失真来确定。扫描调制器输入端的输入电压,使得输出功率水平从-6 dBm变化至-20 dBm。

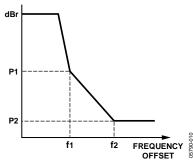

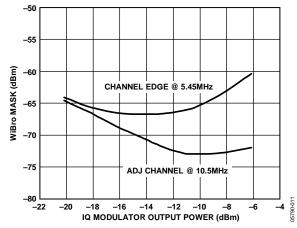

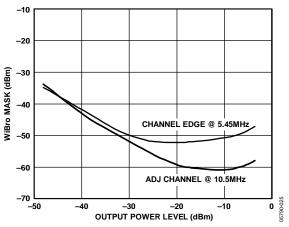

频谱模板目前正在定义之中,但通常是由当地法规针对带外发射做出规定。迄今为止,韩国WiBro标准提供适用于2.3 GHz至2.4 GHz频段的特定频谱模板,如图10所示。其他模板是针对固定和移动无线电系统定义的,例如在美国,针对2.5 GHz至2.69 GHz (FCC 04-258)的部署进行了定义。

例如,图10显示的是WiBro BTS模板的特性,调制信号带宽为8.75 MHz。

图10. BTS WiBro频谱模板(RBW = 100 kHz)

WiBro标准根据天线发射功率指定了不同的ACPR要求。此处的要求是针对+33 dBm天线处的功率水平推算出的:

- P1 ≤ -34.5 dBr, f1 = 4.77 MHz(主通道边缘)

- P2 ≤ -52.4 dBr, f2 = 9.23 MHz(相邻通道中心)

图11显示的是依据该屏蔽的16 QAM、256-OFDM信号的调制器频谱性能,其中针对10 MHz OFDM信号调整了偏移。输入驱动电平已改变,使IQ调制器输出功率处于-20 dBm至-6 dBm范围内。最佳工作点在大约-12 dBm的均方根输出下获得,此时屏蔽获得20 dB以上的裕量。

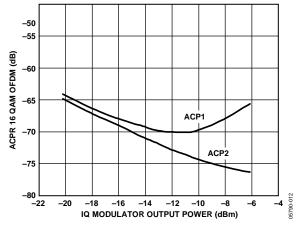

图12显示更一般的ACPR特性,同样是针对10 MHz OFDM 信号,并将相邻和相间通道功率与主通道功率水平进行比较。所有通道功率水平在9 MHz带宽内求积分,ACP1和ACP2分别在载波出现10 MHz和20 MHz偏移时计算。

在第一个频率偏移下(ACP1),随着功率水平下降,越远离压缩点和三阶交调截点,越有助于减少信号失真并改善ACPR性能。随着输出功率进一步下降,信噪比降低(因为相对于调制器噪底,信号能量较少)会造成逐dB的ACPR降低。在ACP2给出的第二个频率偏移下,频谱不会再生,ACPR基本上随信噪比下降而降低。

图11. 依据WiBro模板、16 QAM OFDM调制、I和Q输入电压函数 (或IQ调制器输出功率),在2400 MHz下的调制器性能

图12. 依据16 QAM OFDM调制、I和Q输入电压函数(或IQ调制器输出功率),在2400 MHz下的调制器输出ACPR

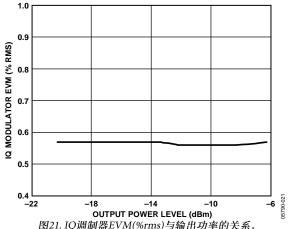

对于IQ调制器本身,WiMAX OFDM波形的EVM性能在0.6% rms时仍十分出色。这主要来自于有限的上边带消除和主通道内每个子载波的二阶和三阶交调。

#### LO频率合成器

本直接变频架构需要一个本振(LO)。从直流至所需RF频率的上变频直接通过IQ调制器实现。诸如相位噪声、频率分辨率和建立时间等性能决定了如何选择小数N分频频率合成器以生成LO。

#### 相位噪声

对于上变频,将WiMAX OFDM信号混合至本振时,相位噪声叠加在所有N个子载波上。

LO相位噪声有两方面的影响:

- 所有子载波的随机相位旋转;

- 由于特定子载波被N-1个高噪声相邻子载波损毁,出现载波间干扰。

为了校正这些构成EVM降低主因的相位误差,OFDM符号包含八个子载波,通过已知数据训练序列进行调制。这些训练子载波称为导频音,可帮助接收机跟踪和移除LO产生的大部分近载波相位噪声。不过,该方法仅能移除慢于符号周期的相位变化,而快于符号周期的相位变化无法跟踪,因此会影响EVM。

对于64 QAM调制OFDM,发射机输出端的EVM要求在3.1% rms下非常严苛。这也是为什么PLL环路带宽和总积分相位误差对PLL设计至关重要的原因。低于1°rms的总相位误差已成为选择频率合成器的标准。

至于整数N分频频率合成器,N分频器足以在提供精细分辨率的同时合成>2.3 GHz的RF频率。在PLL环路带宽内,参考和鉴相鉴频器(PFD)噪声水平均增加20×log(N)倍。这直接使PLL总相位误差降低,后者通常可高于1°rms。

小数N分频频率合成器由于内在具有良好的相位噪声性能而成为首选。使用较高比较频率时,可实现极小的频率分辨率,从而有助于减少总相位噪声。上述小数N分频频率合成器的典型相位噪声误差可小于0.5°rms,非常适合本应用。

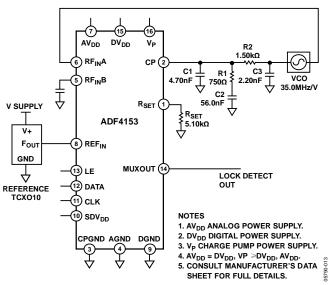

ADF4153是一款4 GHz小数N分频频率合成器,具有三种模式:低噪声模式、低噪声/低杂散模式及低杂散模式。环路滤波器带宽较窄时建议使用低噪声模式,因为环路滤波器响应已经使杂散衰减。WiMAX双工模式就是这种情况,不需要快速锁定环路。

对于快速环路,由于杂散处于环路带宽内,衰减数量较少。低杂散模式会使能扰动。这将使小数量化噪声随机化,使其类似于白色噪声,而不是杂散噪声。

#### 频率合成器频率分辨率

IQ调制器LO要求的最低频率分辨率可从802.16标准要求的信道栅推算出。迄今为止,大多数情况的信道栅要求是250 kHz,某些特定规范是200 kHz。这意味着PLL产生的载波频率至少应为250 kHz的倍数。

#### 参考频率

下列公式决定小数N分频频率合成器的编程方式:

$$RF_{out} = [INT + K/MOD] \times [f_{REF}]$$

(3)

$$MOD = \frac{f_{REF}}{f_{RES}} \tag{4}$$

其中,

RF。业是PLL合成频率。

fpp是参考频率,也等于本例中的PFD比较频率。

INT是整数分频系数。

K设置合成频率小数值。

MOD是模数。

fprs是PLL频率分辨率。

在小数N分频频率合成器中,杂散出现间隔等于通道间隔(小数杂散),也可以是通道间隔的分数(次分小数杂散)。表1显示模数值对次分小数杂散位置的影响。

#### 表1

| 条件               | 杂散间隔   |

|------------------|--------|

| MOD能被2整除,但不能被3整除 | 通道步进/2 |

| MOD能被3整除,但不能被2整除 | 通道步进/3 |

| MOD能被6整除         | 通道步进/6 |

| 其它情况             | 通道步进   |

从公式4可以看出,模数值(MOD)取决于PFD频率和信道间隔。信道间隔是固定的,因此选择PFD时应尽可能避免模数值产生次分小数杂散。

此外,选择的参考频率应足够高,以减小整数INT分频比(参见公式3)。大于10 MHz的基准频率有助于改善PLL相位噪声,作用甚至优于整数N分频频率合成器。

#### 锁定时间

PLL锁定时间在下列情况中可能很重要:

- 使用频率双工和时间双工的HFDD系统。

- 在用于实现较佳信号质量、增加数据安全性、避免多路径衰落或避免干扰的跳频期间。

PLL锁定时间可通过增加基准或比较频率来优化,如果需要还可增加环路带宽。

对于ADF4153,最高可选择32 MHz的参考频率或PFD频率,或者通过可用的倍频器增加PFD频率,同时使用较低频率的基准时钟。

定义PLL环路带宽时需要在所需建立时间、可接受的相位 误差和杂散水平之间进行权衡。环路带宽越大,锁定时间 越短,但相位误差和杂散水平也较高。如果锁定时间不重 要,建议使用窄环路带宽,具体理由如"相位噪声"部分所 述。

#### 性能

从该特定特性上看,PLL是专为约20 kHz的闭环带宽设计的。对于10 MHz 256 OFDM信号,符号持续时间为25.6 μs,对应于39 kHz的子载波间隔。因此,PLL环路有意设计成慢于符号持续时间,以便通过导频跟踪算法跟踪和移除大部分相位噪声。图13显示内置环路滤波器的PLL的原理图。

图13. PLL环路原理图

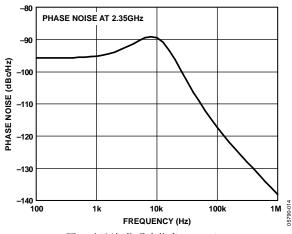

图14显示该PLL的闭环相位噪声性能。

VCO为Sirenza VCO190-2350T(Y),调谐灵敏度为35 MHz/V (典型值)。PLL闭环带内相位噪声为-95 dBc/Hz。

该设计的等效均方根相位噪声仅为0.35°rms,等效于0.6%的EVM贡献。该小数N分频PLL对于总体EVM性能的贡献在"总体系统性能"部分中讨论。

图14. 闭环相位噪声仿真, 2.35 GHz

#### VGA和IQ调制器接口

由于WiMAX系统可用于非视线应用,因此有必要对发射机进行增益控制以根据信道质量调整输出Tx电平。

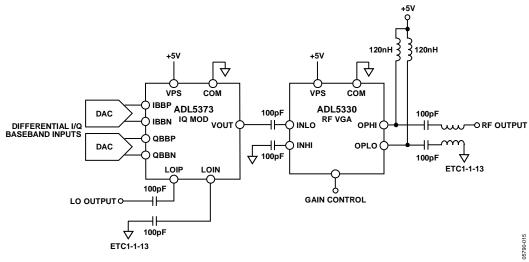

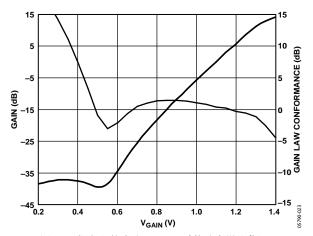

ADL5330是一款高性能VGA,  $50 \Omega$  I/O, 在2.3 GHz下提供接近50 dB的增益控制,增益控制斜率约为60 dB/V。VGA增益控制需要0.5 V至1.4 V的正控制电压。在VGAIN = 1.4 V时,可实现接近15 dB的最大增益。实现ADL5373 IQ调制器与ADL5330接口的基本连接如图15所示。

图15. IQ调制器和RF VGA接口

ADL5373专为驱动50  $\Omega$ 负载而设计,可轻松地与VGA实现接口。

如果要减小来自VGA的功率,建议在调制器和VGA之间添加焊盘。这有助于保持最佳线性度,同时可改善输出噪底。

同时,为了在2 GHz至3 GHz带宽内工作,建议使用专门匹配该带宽的差分至单端巴伦。ADL5330可提供差分输入和输出。对于单端接口,使用Murata SP-LDZ-49\_LDB182G5005G这样的巴伦很有帮助,至少可将RF增益改善1 dB。

#### 均方根功率检测

为了使功率控制精确快速,可在功率放大器输出端使用AD8362均方根功率检波器。这是一款高精度、宽带均方根-直流平方律检波器。此平方律函数的输出是正电流,通过片内电容和外部电容CLPF求积分。然后通过直流耦合放大器缓冲所得电压,从而提供可用于测量和控制用途的输出。

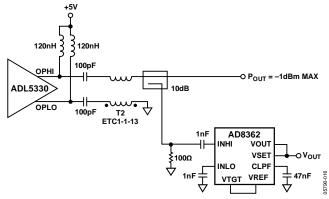

图16显示通过定向耦合器实现的均方根功率测量。出于实用目的,器件放置在VGA输出端,但也可用于检测功率放大器(PA)输出端的功率水平。

图16. 使用AD8362的功率检测

AD8362既可接受差分输入(检测范围最佳),也可接受单端输入。由于耦合器的耦合端口不平衡,AD8362特别采用单端驱动,以适合802.16标准中的所有电位调制。

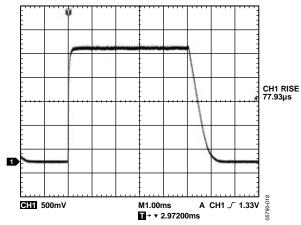

为了移除信号包络残余,平方律检波器的输出端需要使用外部滤波分流电容。对于WiMAX信号, 0.1 μF电容就能实现检波精度与建立时间的良好平衡。为了获得更快的响应,可使用较小电容以及快速采样ADC。

#### 表2

| CLPF   | 40 dB内精度         | 建立时间   |

|--------|------------------|--------|

| 0.1 μF | +0.3 dB/-0.5 dB  | 160 μs |

| 47 nF  | +0.3 dB/-0.75 dB | 78 μs  |

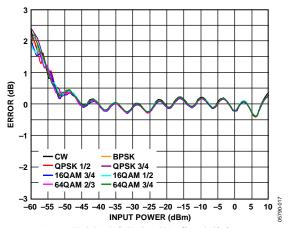

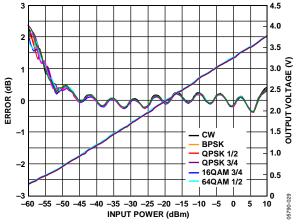

图29和图30显示了功率检波器的预期测定性能。

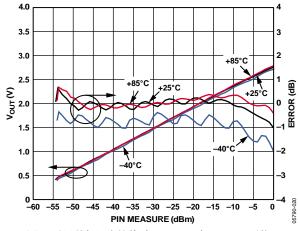

图17显示CLPF = 1 μF且VTG = 0.625 V时的功率检测误差。

图17. 均方根功率检波器检测范围和精度, $CLPF = 1 \mu F$

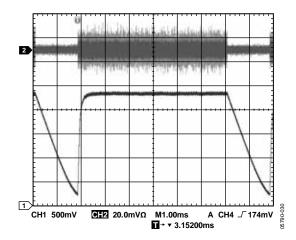

当VTG = 0.625 V(通过电阻分压器连接VREF与VTG)且CFLT电容较小时,通过高速求平均值ADC可实现类似的性能。此类配置中,均方根检波器对施加给它的OFDM调制类型完全不敏感。因此,无论是QPSK还是64 QAM调制OFDM子载波均不需要校准。图18显示CLPF = 47 nF时的功率检波器建立时间。

图18. 功率检波器对WiMAX下行链路突发脉冲 $(T_{SYMB}=25.6~\mu s)$ 的时间响应,CLPF=47~n

#### 温度补偿

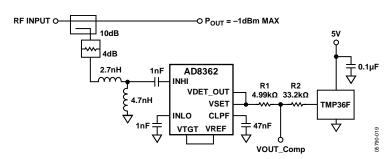

为了改善在2.35 GHz下AD8362在整个温度范围内的测量精度,可使用简单的温度补偿方案。它有助于校正具有V<sub>DET</sub> = f(Pin)特性的检波器交调点的漂移。随着温度提高,整个传递函数会下降,而斜率则相当稳定。因此,对于特定输入电平(如-15 dBm)下漂移的补偿在整个动态范围内有效(参见图20)。

补偿方法很简单,依靠的是TMP36精密温度传感器。TMP36在25°C时的输出电压为750 mV,温度系数为10 mV/°C。TMP36的正温度系数可直接补偿检波器的负温度系数。实现的电路如图19所示。(注意,为避免图示混淆,AD8362的VOUT引脚显示为VDET\_OUT。)R1和R2的电阻比可加以计算,使得校正后的VOUT\_Comp电压在整个温度范围内保持稳定。

AD8362在2.35 GHz时的温度漂移是-0.03 dB/°。该值是在-15 dBm的检波器输入功率下测得的。

以下公式显示电阻比计算方式:

$$\frac{R2}{R1} = \frac{-\frac{\Delta V_{TM}P}{\Delta T}}{\frac{\Delta V_{DET}}{\Delta T}} = -\frac{10 \text{ mV/°C}}{AD8362 \text{ Drift (mV/°C)}}$$

AD8362温度漂移单位dB/°C通过乘以检波器的对数斜率 (2.35 GHz时为49.79 mV/dB)转化为mV/°C。本应用中, - 0.03 dB/°C的漂移等效于-1.51 mV/°C。

图20显示了补偿后的电路在整个温度范围内的测定性能 (2.35 GHz)。请注意,选择的补偿因数是为了优化0℃至85℃ 范围内的温度漂移。这与不太重视低温性能的终端设备一致。

图19. AD8362在2.35 GHz下的功率检测和温度补偿

图20. 采用外部温度补偿时, AD8362在2.35 GHz下的 输出电压和温度漂移

#### 总体系统性能

表3总结整个Tx链性能。系统性能描述如下:

- 功率控制范围

- 最大线性输出功率

- 增益平坦度

- 噪底

- OP1dB及OIP3

- 功率检波器精度和检测范围

- WiMAX OFDM信号EVM

- WiMAX OFDM信号频谱质量

OFDM信号通过从WiMAX信号发生器获取I和Q矢量来生 成。EVM性能使用Agilent 89600解调软件来测量。

对于OFDM信号,大部分EVM降低是由IQ调制器的不足和 本振相位噪声或相位误差引起的。通过在接收机或解调器 内实现相位跟踪算法,可以移除在上变频后调制副载波的 部分近载波相位噪声。

在-3 dBm输出功率下,该发射链内每一构建模块对于EVM 的贡献如下:

- DAC和IQMOD, 理想LO: EVM = 0.6%

- DAC和IQMOD + VGA, 理想LO: EVM = 1.02%

- DAC和IQMOD + VGA, 小数N分频PLL: EVM = 1.21%

用于该参考设计的小数N分频PLL存在由0.35°相位噪声引 起的相位误差,仅使总体系统EVM降低0.2%。

在这些特性下, IQ调制器输出功率水平在-14 dBm时到达最 佳功率水平。接着添加3 dB焊盘以驱动Tx VGA。

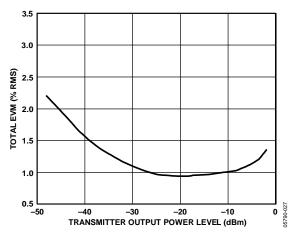

图21. IQ调制器EVM(%rms)与输出功率的关系,

图22. 与Tx VGA增益成函数关系的信号链总EVM

输入功率为-17dBm时, VGA可提供约-3dBm, 且具有1.2%的 极佳EVM性能,如图22所示。

图22重点说明ADL5373 IQ调制器在适当输出功率水平下的 出色EVM性能。它对级联EVM性能的贡献极小。

在中间功率下, EVM基本上由IQ调制器和LO频率合成器 驱动。随着输出功率到达动态范围最低部分,EVM性能开 始随信噪比下降而降低。

## 典型工作特性

对于ADL5373、ADL5330、AD8362元件, VPS1=5 V。对于ADF4153及AD9860/AD9862, VPS2=3.3 V。射频频段: 2.3 GHz至2.4 GHz。

图23. IQ调制器输出为-10 dBm时的功率增益范围, 以及2350 MHz时增益法则一致性与V<sub>GAIN</sub>的关系

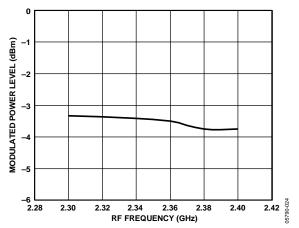

图24. 关于调制OFDM信号,调制功率水平与RF频率的关系

图25. 依据WiBro模板(64 QAM WiMAX OFDM, 10 MHz BW)、 输出功率函数或V<sub>GAIN</sub>电压的发射机频谱质量

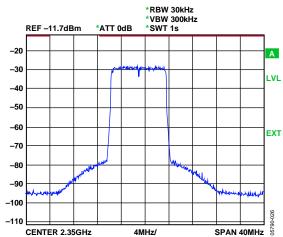

图26. 2.35 GHz (64 QAM WiMAX OFDM, 带宽= 10 MHz) 、 -5 dBm输出功率时的发射机输出频谱

图27. 802.16 64 QAM OFDM信号的发射机总EVM, 信号带宽为10 MHz

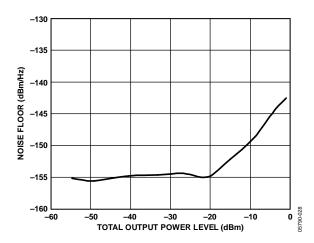

图28. 发射机输出噪底与输出功率 (QPSK、16 QAM、 64 QAM OFDM调制信号) 的关系

图29. QPSK、16 QAM、64 QAM OFDM调制中,均方根功率检波器响应 及检波误差与Tx信号链输出功率水平的关系

图30. WiMAX下行链路突发脉冲(长前同步码,FCH、64 QAM OFDM 数据序列)的功率检波器时间响应,T<sub>SYMB</sub> = 25.6 μs

## 测定性能总结

VPS1=5 V (ADL5373、ADL5330和AD8362)。VPS2=3.3 V (ADF4153、AD9860/AD9862 DAC)。射频频段: 2.3 GHz至2.4 GHz。信号带宽=10 MHz。QPSK、16 QAM及64 QAM、256副载波OFDM调制。

## 表3

| 参数          | 条件                                                           | 典型值    | 单位     |

|-------------|--------------------------------------------------------------|--------|--------|

| 最大线性输出功率水平  | 64 QAM OFDM, EVM = 1.2 %                                     | -3     | dBm    |

| 输出功率控制范围    | 2.35 GHz, ±3 dB增益法则一致性, VGA输入功率<-10 dBm                      | 51     | dB     |

| 增益平坦度与频率的关系 | 2.3 GHz至2.4 GHz频段                                            | 0.005  | dB/MHz |

|             | BW = 20 MHz为最差情况                                             | 0.25   | dB     |

| OIP3        | @ 2.35 GHz, $V_{GAIN}^1 = 1.4 \text{ V}$                     | 19     | dBm    |

| OP1dB       | @ 2.35 GHz, V <sub>GAIN</sub> = 1.4 V                        | 12.4   | dBm    |

| 频谱模板/ACP    | RBW = 100  kHz, VBW = 30  kHz                                |        |        |

|             | 64 QAM OFDM – POUT = -5 dBm,10 MHz信号                         |        |        |

|             | 10MHz偏移下的相邻信道                                                | -55    | dB     |

|             | 信道边缘的WiBro模板第一偏移                                             | -48.5  | dBr    |

|             | 相邻信道中心的WiBro模板第二偏移                                           | -59    | dBr    |

| EVM与增益控制的关系 | 64 QAM OFDM, 2.35 GHz                                        |        |        |

|             | $P_{OUT} = -3 \text{ dBm}, V_{GAIN} = \overline{\mathbf{a}}$ | -38.4  | dB     |

|             |                                                              | 1.2    | %      |

|             | $P_{OUT} = -30 \text{ dBm}, V_{GAIN} = \text{ ff}$           | -39.1  | dB     |

|             |                                                              | 1.1    | %      |

| 宽带噪底        | 偏移频率 = 20 MHz, Роит = -1 dBm or V <sub>GAIN</sub> = 1.4 V    | -142.5 | dBm/Hz |

|             | 偏移频率= 20 MHz, Pout ≤ -20 dBm or V <sub>GAIN</sub> ≤ 1 V      | -155   | dBm/Hz |

| 均方根功率检测范围   | 所有调制类型,误差<±0.5 dB                                            | 60     | dB     |

<sup>&</sup>lt;sup>1</sup> VGAIN是ADL5330增益控制电压。

#### 表4. 电源

| 参数     | 条件                                    | 典型值 | 单位 |

|--------|---------------------------------------|-----|----|

| 正电源电压1 |                                       | 5   | ٧  |

| 静态电流   | ADL5373、ADL5330及AD8362总电流             | 380 | mA |

| 正电源电压2 |                                       | 3.3 | V  |

| 静态电流   | ADF4153、AD9860/AD9862 Tx在80 MSPS下的总电流 | 165 | mA |

## 主要元件物料清单

### 表5. 元件描述(不包括无源器件)

| 代号            | 功能              | 供应商       | 评估板产品型号              |

|---------------|-----------------|-----------|----------------------|

| AD9860/AD9862 | 混合信号前端(ADC和DAC) | Analog 公司 | AD9860-EB, AD9862-EB |

| ADL5373       | 直接变频IQ调制器       | Analog 公司 | ADL5373-EVALZ        |

| ADL5330       | 电压控制放大器/衰减器     | Analog 公司 | ADL5330-EVAL         |

| ADF4153       | 小数N分频PLL        | Analog 公司 | EVAL-ADF4153EB1      |

| AD8362        | 均方根响应功率检波器      | Analog 公司 | AD8362- EVALZ        |