# AN-1260 应用笔记

One Technology Way • P.O. Box 9106 • Norwood, MA 02062-9106, U.S.A. • Tel: 781.329.4700 • Fax: 781.461.3113 • www.analog.com

# 视频解码器、HDMI接收器和收发器的晶振设计考虑因素

# 简介

为实现频率稳定性和精确性,使用本应用笔记作为振荡器 外部电路的设计指南。

此外,本应用笔记还描述视频解码器的振荡器电路。在基频模式下,大部分ADI视频解码器通常都需要一个标称频率为28.63636 MHz1、频率稳定性为50 ppm的晶振。表1详细罗列了用于ADV7403评估板的晶振规格。本应用笔记基于ADV7401和ADV7403;然而它同样适用于ADV740x、ADV718x、ADV728x、ADV7800、ADV7802、ADV7842、ADV7844和ADV7850视频解码器。

视频产品内置独立的高清多媒体接口(HDMI®)接收器(ADV7611、ADV7612、ADV7619和ADV7604)以及HDMI视频接收器,这些器件无法对模拟视频进行数字化(比如ADV7622和ADV7623),可以使用最小化传输差分信号(TMDS)时钟来接收像素信号。这些器件不需要高精度晶振时钟源,因为晶振精度不影响视频质量。这种情况下,来自晶振电路的时钟主要用于测量TMDS频率时钟,以便产生自由运行的视频图案,并执行其他非视频相关操作,比如扩展显示识别数据(EDID)和高带宽数字内容保护(HDCP)。因此,它不会影响已处理视频的质量。

表1. 用于ADV7403评估板的晶振规格(参见参考文献1)

| 特性         | 数值           |

|------------|--------------|

| 封装形式       | HC49         |

| 标称频率       | 28.63636 MHz |

| 振荡模式       | 基频           |

| 频率校准(25℃时) | ±0.0030%     |

| 频率温度稳定性容差  | ±0.0050%     |

| 工作温度范围     | -10℃至+60℃    |

| 等效电阻(最大值)  | 30 Ω         |

| 负载电容       | 30 pF        |

| 驱动电平       | 100 μW       |

| 分流电容(最大值)  | 7.0 pF       |

| 年老化率       | ±0.0003%     |

## 振荡器说明

#### 电路

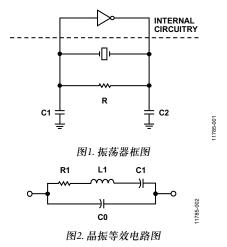

图1显示视频解码器中振荡器的框图。石英晶振的等效电路如图2所示。C0是晶振的分流或静态电容。R1表示动态电阻,L1表示动态电感,C1表示动态电容。R1、L1和C1由晶振的机械属性所决定。它们位于晶振的动态支臂上,并且仅在晶振振荡时才会产生影响(参见参考文献2)。R是外部分流电阻,对于ADV740x系列产品而言,其建议值为1 MΩ。

额外的外部分流电阻适用于大部分视频解码器和HDMI接收器,但ADV7850和ADV7619除外。如需最新的信息,请参见ADI网站上相关视频器件的推荐原理图:www.analog.com。

<sup>1</sup> 若使用ADV7850,则该值为27 MHz,更多信息请参见相关视频器件的推荐 原理图。

# AN-1260

#### 串联和并联谐振

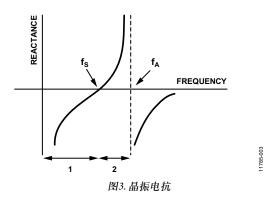

晶振的有效电抗曲线如图3所示。区域1和区域2中的频率 范围表示基频模式。

基频模式有两种谐振类型: 串联和并联。

当L1动态电感与C1动态电容谐振时,将会产生串联谐振。 串联谐振频率由下式近似确定:

$$f_S = \frac{1}{2\pi\sqrt{L1C1}}$$

当负载电容C<sub>L</sub>两端连接晶振引脚时,产生并联谐振。并联谐振中晶振的振荡频率由下式近似确定:

$$f_{XTAL} = f_S \left( \frac{C1}{2(C0 + C_L)} + 1 \right)$$

注意,图3区域2显示的并联谐振可计算如下:

$$f_A = \frac{1}{2\pi\sqrt{L1C1(C1C0)/(C1+C0)}}$$

用于ADV740x解码器的晶振在并联谐振模式下振荡,本应用笔记的其余部分将会讨论。工作频率等于区域2范围内显示的晶振频率(见图3)。

#### 晶振规格

#### 频率容差

频率容差是指晶振适当调谐时,在有限频率范围内振荡的能力。制造商通常给出与频率容差有关的两个规格,包括:

- 频率校准容差,表示25°C时标称频率的最大偏差。

- 频率温度稳定性容差,表示温度在工作温度范围内波动时,标称频率的最大偏差。

表1中的频率校准容差为 $\pm 0.0030\%$ ,因此,最大频率偏差 ( $\Delta f$ )由下式给出:

$$\Delta f = 28.63636 \text{ MHz} \times 0.000030 \approx 859.09 \text{ Hz}$$

因此,下式正确:

$$0.0030\% = \frac{0.0030}{10^2} = \frac{30}{10^6} = 30 ppm$$

#### 负载电容

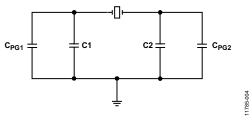

晶振数据手册中的负载电容给出25℃时,容差范围内的并 联谐振频率。因此,设计一个匹配负载电容的电路很重 要,以便达到制造商规定的频率。使用下式计算负载:

$$C_L = \frac{(C_{PG1} + C1)(C_{PG2} + C2)}{C_{PG1} + C1 + C_{PG2} + C2} + C_S$$

其中:

$C_{PGI}$ 和 $C_{PG2}$ 表示引脚到地电容。

C。表示印刷电路板(PCB)杂散电容。

一个较好的原则是 $C_{PG_1}$ 和 $C_{PG_2}$ 近似取5 pF至10 pF,而 $C_s$ 近似取2 pF至3 pF。

图4. 计算晶振负载电容

例如,使 $C_{PG1} = C_{PG2} = C_{PG} = 4 \text{ pF} \\ \text{EC} 1 = C2 = C. C_{PG} \\ \text{表示寄生接地电容。如需使负载电容} \\ C_L = 30 \text{ pF,则C值必须为已知(见表1)。C值可从上式获取。}$

$$C = 2(C_L - C_S) - C_{PG}$$

= 2(30 - 3) - 4

= 50 pF

因此,针对C1和C2,可选择两个47 pF电容。通过改变C1和C2的起始值,可优化电路性能。

#### 等效串联电阻

等效串联电阻(ESR)通常由制造商指定。假定振荡器匹配负载电容(CL),则ESR是晶振阻抗的实值部分。

$$ESR = R1 \left( 1 + \frac{C0}{C_L} \right)^2$$

例如,表1中给出的晶振ESR为30  $\Omega$ , $C_L$ 等于30 pF。针对 ADV740x解码器,建议ESR  $\leq$  30  $\Omega$ 。

# 驱动电平

驱动电平等于晶振功耗。将功耗限制在规格数值以内很重要,以防晶振受损。如果晶振峰值电压由于直流电源而取近似值,那么功耗可近似表示为:

$$P = 2R1(\pi f_{XTAL}(C_L + C0)V_{CC})^2$$

#### 质量因数

晶振数据手册中通常不提供品质因数(Q)。Q因数是存储电能的无功功率与所有电能损耗总和之比。因此,当不存在任何损耗时,理想振荡器中的Q因数等于无穷大。标准晶振的Q因数范围为20,000至200,000。Q因数极高的晶振有助于晶振的高频稳定性。

## 参考文献

- <sup>1</sup> 产品规格: HC49标准晶振系列(产品型号MA01377), Golledge Electronics, Ltd.,有关该器件的更多信息,请联 系Golledge Electronics。

- <sup>2</sup> 应用笔记AP-155: 用于微控制器的振荡器(英特尔公司, 1983年6月)。

## 修订历史

2013年10月—修订版0: 初始版

| Δ | N | _1 | 12 | 6 | N |  |

|---|---|----|----|---|---|--|

| _ |   |    | _  | u | • |  |

注释